AD9851——FPGA调试(并行模式)

工程功能:使用FPGA来调试AD9851芯片,使用的是并行模式

芯片手册:AD9851 CMOS 180 MHz DDS/DAC Synthesizer Data Sheet (Rev. D) (analog.com)

管脚功能

| 管脚名称 | 管脚功能 |

|---|---|

| D0-D7 | 8位数据输入。用于加载32位频率和8位相位/控制字的数据端口。D7 = MSB ; Do = LSB ; D7引脚25也可作为40位串行数据字的输入引脚。 |

| PGND | 6倍参考时钟倍乘器 地 |

| PVCC | 6倍参考时钟倍乘器电源 |

| W-CLK | 字量时钟。上升沿将并行或串行频率/相位/控制字异步加载到40位输入寄存器中。 |

| FQ_UD | 更新频率。上升沿异步地将40位输入寄存器的内容传输给DDS核。当已知输入寄存器的内容只包含有效的、允许的数据时,应该发出FQUD。 |

| REFCLOCK | 参考时钟输入。CMOS/ ttl级脉冲序列,直接或通过6× REFCLK倍增器。在直接模式下,这也是SYSTEM CLOCK。如果使用了6× REFCLK乘法器,那么该乘法器的输出就是SYSTEM CLOCK。系统时钟的上升沿启动操作。 |

| AGND | 模拟地。模拟电路(DAC和比较器)的接地返回 |

| AVDD | 模拟电路的正电源电压(DAC和比较器,引脚18)和带隙参考电压,引脚11。 |

| RSET | DAC的外部RsET连接-名义上是一个3.92 kΩ电阻到地,输出10 mA。这设置了从IOUT和IOUTB可用的DAC满量程输出电流。RsET = 39.93/IOUT。 |

| VOUTN | 电压输出负。比较器的互补CMOS逻辑电平输出。 |

| VOUTP | 电压输出正。比较器的真实CMOS逻辑电平输出。 |

| VINN | 输入电压负。比较器的反相输入。 |

| VINP | 电压输入正。比较器的非反相输入。 |

| DACBP | DAC旁路连接。这是DAC电压参考旁路连接,通常为NC (NO CONNECT),用于最佳SFDR性能。 |

| IOUT | 除了IOUTB =(满量程输出-IOUT)外,与IOUT具有相同特性的互补DAC输出。输出负载应等于IOUT,以获得最佳的SFDR性能。 |

| IOUT | 平衡DAC的真实输出。电流是源,需要电流到电压 |

| RESET | 主复位引脚;活性高;清除DDS累加器和相位偏移寄存器,以实现0 Hz和0°输出相位。将编程设置为并行模式并解除6× REFCLK乘法器。Reset不清除40位输入寄存器。在上电时,在编程开始之前,断言RESET应该是第一优先级。 |

| DVDD | 数字电路的正电源电压引脚。 |

| DGND | 数字地。数字电路的接地返回引脚。 |

上面为机翻,其中有几个管脚在调试过程中比较重要:

- 供电,我用3.3V来给芯片供电。

- REFCLOCK 参考时钟,我用125M的晶振来直接接入芯片。

- RESET,这个管脚很重要,可以清除DDS累加器和相位,还可以调控串并行模式(但是这个模式切换我还没有研究明白,之后再补充)。

- D0-D7、W-CLK、FQ_UD ,时序的关键信号。

- IOUT、IOUT,输出、用示波器测试的管脚,

输出频率、相位

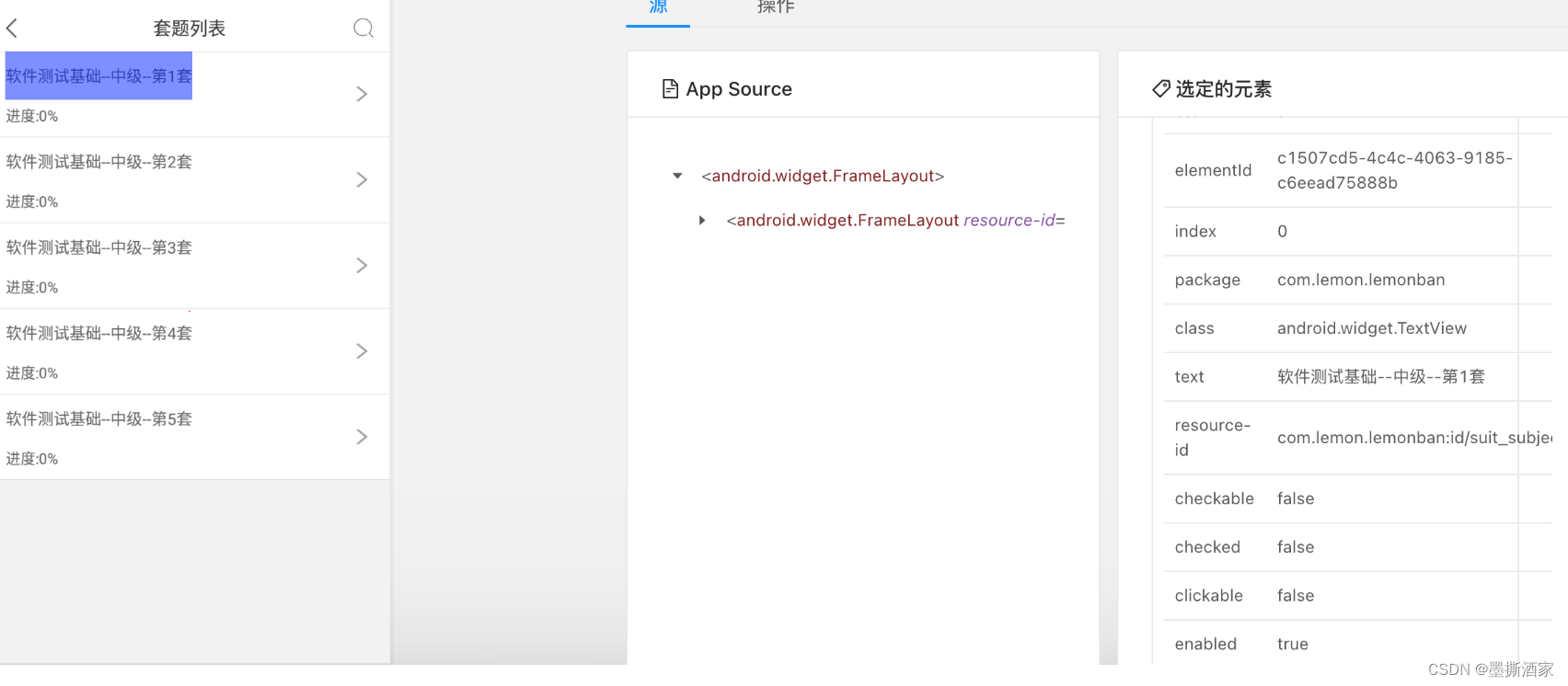

如上图,并行输入控制字。

第一个控制字W0: Data[0]是6倍频使能信号,为0时关闭6倍频

Data[1]置为0

Data[2]置为0,不在Power-Down模式

Data[3]-Data[7] :相位控制字

剩下4个控制字W1-W4:32位的频率控制字

频率计算如上图所示,下图是官方手册给的一个示例,我们根据这个示例来解释

系统时钟为180MHZ,5个控制字为:

W0 = 00001001

W1 = 00001110

W2 = 00111000

W3 = 11100011

W4 = 10001110

由W0可知,开启了6倍频,所以这180MHZ的系统时钟是这样来的:REFCLOCK 参考时钟输入为30MHZ,再6倍频为180MHZ

*相位控制字为1,相位为:(1/(2^5))360° = 11.25°

频率控制字为 0000 1110 0011 1000 1110 0011 1000 1110 ,转换为十进制为:238609294

所以频率为:238609294*180/(2^32) = 10HMZ

由上面方法可轻松计算出想要的频率和相位

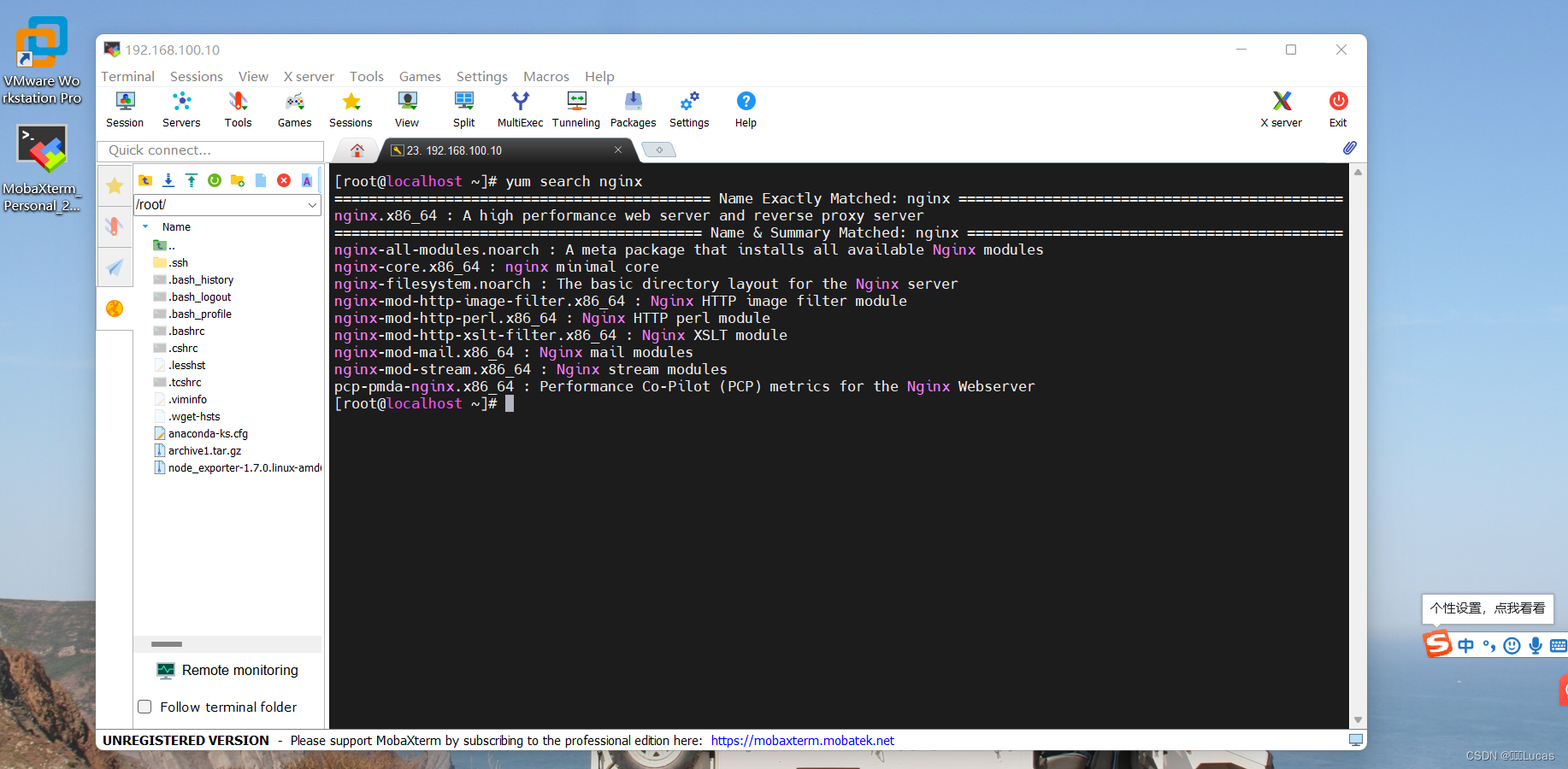

时序图

这个时序图就是写代码的关键

参考文章:AD9851调试过程----相位设置、频率计算、控制字设置-CSDN博客

在控制字准备好之后,拉高W_CLK,控制字在W_CLK的上升沿写入芯片中。连续写完5个控制器后,拉高FQ_UD

下面给出我的仿真波形:

至于RESET,我是这样写的:

上电时先拉底,保持一段时间高电平后,再拉底 (说实话,这个RESET我也不是特别透彻,有理解的可以在评论中补充)

关键代码

always @(posedge CLK_2M or negedge rst_n)beginif(!rst_n)begincnt<=16'd0;start<=0;order<=4'd0;FreUp<=1'b0;RESET<=0;endelse begin if(cnt<=10)begincnt<=cnt+16'd1;RESET<=0;endelse if(cnt<=50)begincnt<=cnt+16'd1;RESET<=1;endelse if(cnt<=100)begincnt<=cnt+16'd1;RESET<=0;endelse begin if(order<=4'd4)beginstart<=1;case(order) //写入5个控制字, Com (W0) 和 Fre (W1 W2 W3 W4) 一共40位控制字4'd0:wr_dat[7:0]<=commond[7:0];4'd1:wr_dat[7:0]<=fre_set[31:24];4'd2:wr_dat[7:0]<=fre_set[23:16];4'd3:wr_dat[7:0]<=fre_set[15:8];4'd4:wr_dat[7:0]<=fre_set[7:0];default: ;endcaseorder <= order+4'd1;endelse if (order<=4'd7)beginstart<=0;order <= order+4'd1;case(order)4'd6:begin //五个控制字写完之后,又过了一个W_CLK时钟周期后,给FQ_UD高电平脉冲FreUp<=1'b1;wr_dat[7:0]<=commond[7:0];end4'd7:beginFreUp<=1'b0;order<=4'd0;enddefault: ;endcaseendendendend//时序图中W_CLK的波形

always @(posedge CLK_10M or negedge rst_n)beginif(!rst_n)beginWR_CLK<=0;count<=8'd0;//wr_dat[7:0]<=commond[7:0];endelse beginif(start)begincount = count+8'd1;case(count)8'd1 :WR_CLK<=1;8'd4 :WR_CLK<=0;8'd6 :WR_CLK<=1;8'd9 :WR_CLK<=0;8'd11 :WR_CLK<=1;8'd14 :WR_CLK<=0;8'd16 :WR_CLK<=1;8'd19 :WR_CLK<=0;8'd21 :WR_CLK<=1;8'd24 :WR_CLK<=0;default : ;endcaseendelsebeginWR_CLK<=0;count<=8'd0;endendend

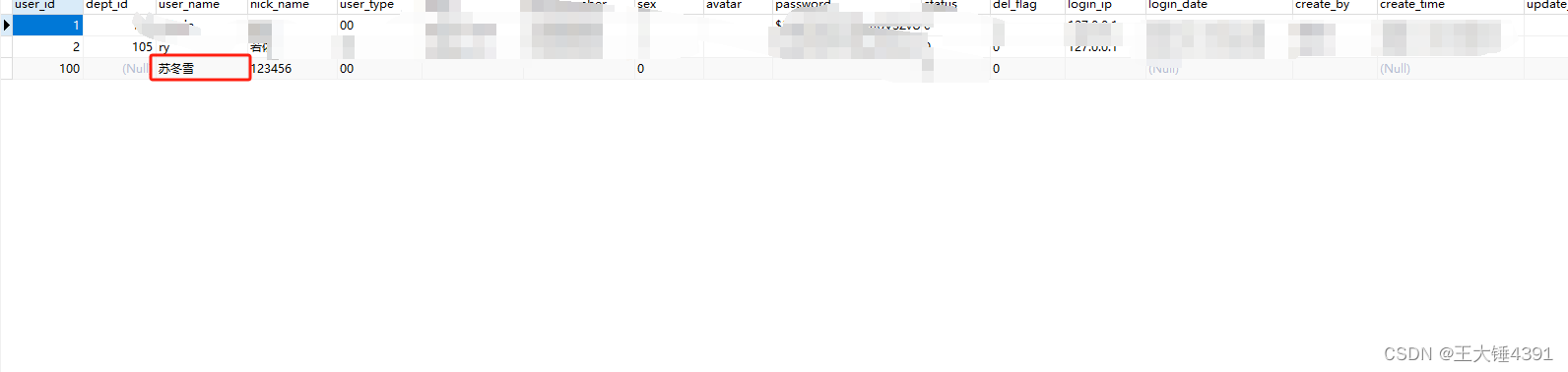

测试结果

ILA波形:

示波器波形:

输出结果:(幅度为200mV是因为示波器探针选择的 ×10)

工程资源、补充

在这个工程中,我用的是正点原子的达芬奇开发板xc7a35t-2 ffg484(50MHZ时钟),将J2排针引出来接入AD9851中

在代码中,我用50MHZ的系统时钟分频生成了2MHZ和10MHZ,用于满足时序要求

分频器参考:https://zhuanlan.zhihu.com/p/620290497

工程下载:AD9851-FPGA调试(并行模式)资源-CSDN文库