LVDS,全称Low-Voltage Differential Signaling,即“低电压差分信号”,有两种含义(LVDS电平与LVDS协议),要根据具体的情况来区分对方说的是LCD屏的LVDS协议或者仅指LVDS电平标准。

举例:示波器测量的是LVDS电平,招聘网站上说的熟练掌握LVDS指的是LCD屏的LVDS协议

当然了,LCD屏的LVDS协议遵循LVDS电平标准。

一、LVDS电平标准

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

1.1 LVDS信号传输组成

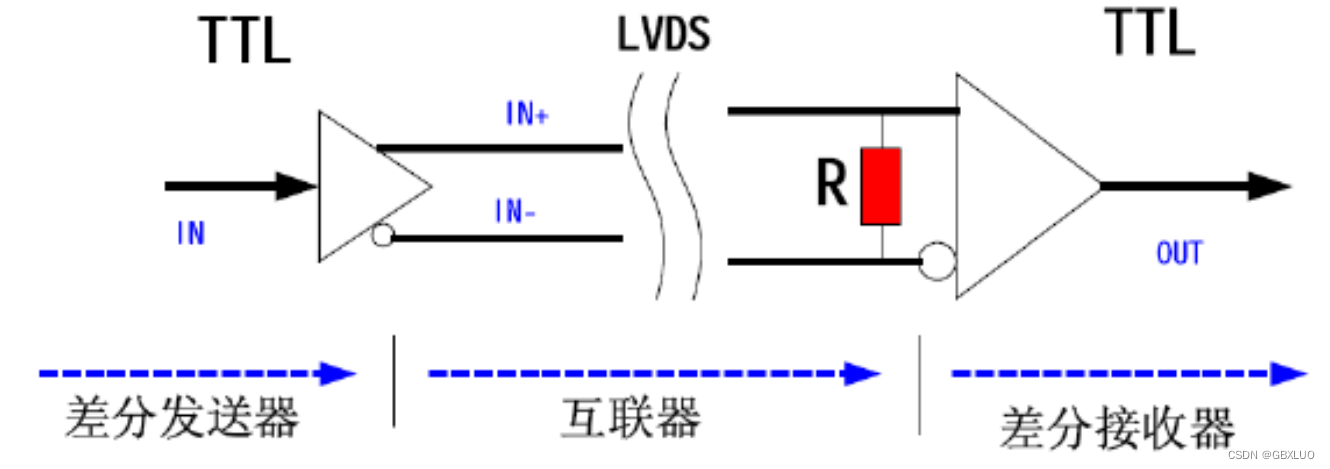

LVDS信号传输一般由三部分组成,如图1所示:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

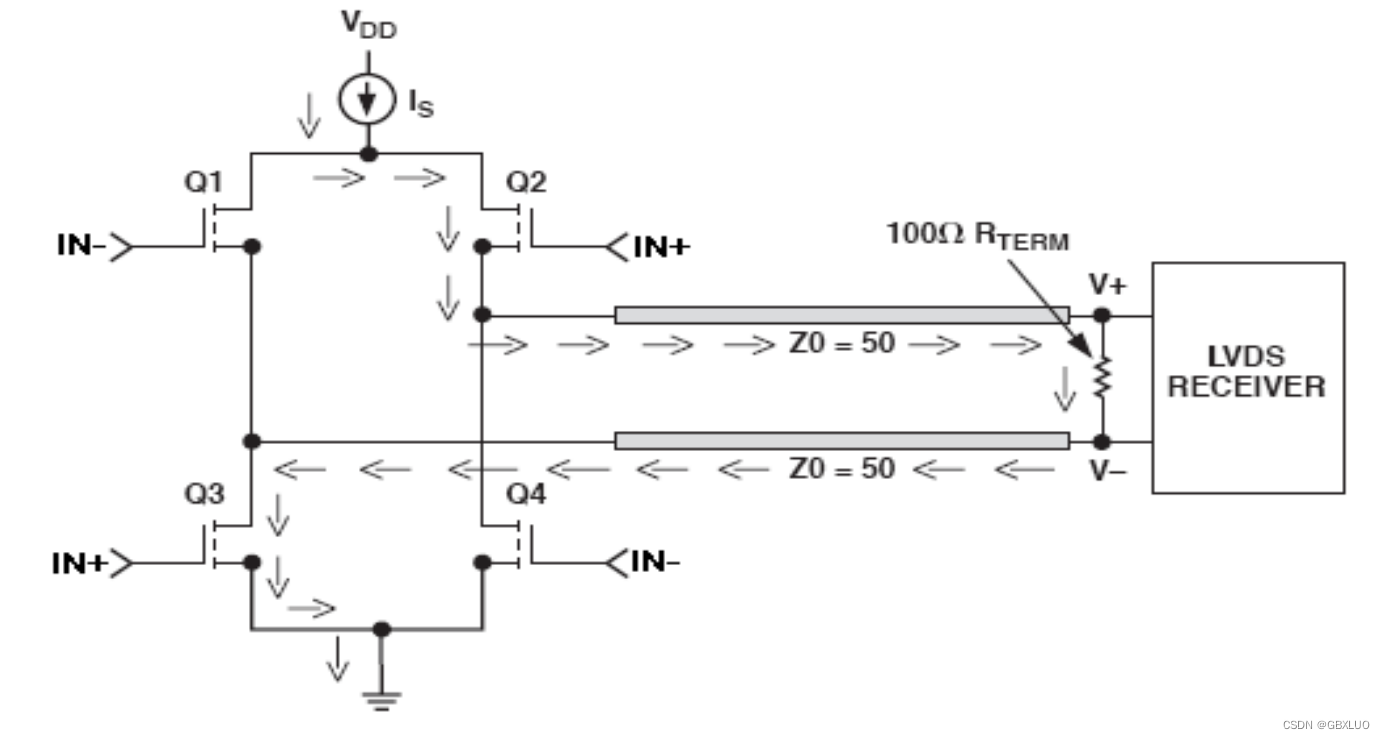

如上图所示,LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV的电压。

驱动器的输入为两个相反的电平信号,四个nMOS管的尺寸工艺是完全相同的。当输入为“1”时,标号IN+的一对管子导通,另一对管子截止,电流方向如上图所示,并产生大约350mV的压降;反之,输入为“0”时,电流反向,产生大约350mV的压降。这样根据流经电阻的电流方向,就把要传输的数字信号(CMOS信号)转换成了电流信号(LVDS信号)。接受端可以通过判断电流的方向就得到有效的逻辑“1”和逻辑“0”状态从而实现数字信号的传输过程。

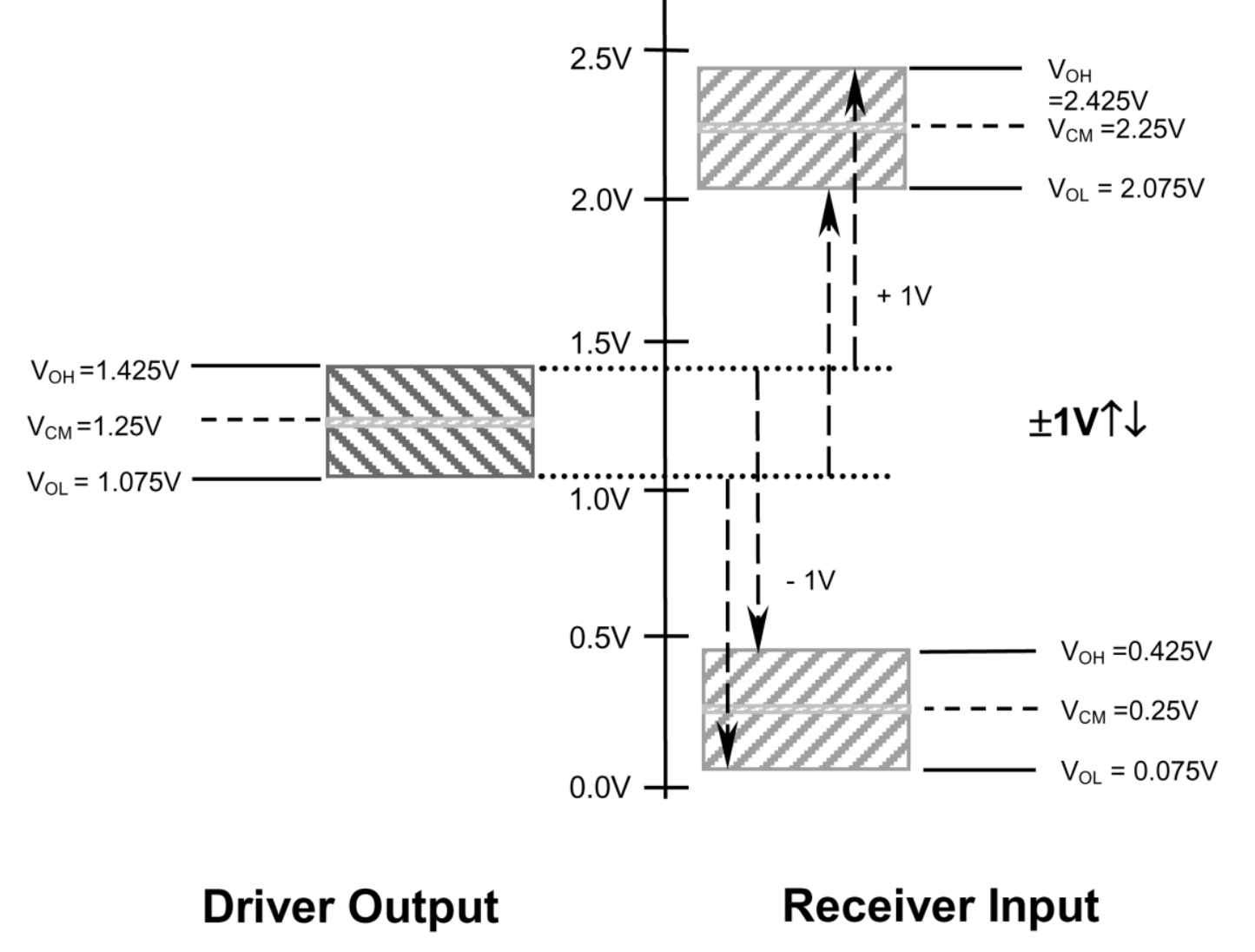

由于MOS管的开关速度很高,并且LVDS的电压摆幅低(350mV),因此可以实现高速传输。其电平特性如下图所示

1.2 LVDS技术特点

LVDS技术和其他的接口相比,有着很大的优势,主要表现在下面几个方面:

1.2.1 高速率:

由于LVDS逻辑状态间的电压变化仅为350mV,因而能非常快地改变状态从而实现高速率。

1.2.2 低功耗

随着工作频率的増加,LVDS的电源电流仍保持平坦,而CMOS和GTL技术的电源电流则会随频率增加而呈指数上升,这得益于使用恒流线路驱动器。电流源把输出电流限制到约3.5mA(功耗约为1.2mW),同时也限制跳变期间产生的任何尖峰电流。这样在得到高达1.5Gbps的高数据率的同时而不明显增加功耗。恒流驱动输出还能容忍传输线的短路或接地,而不会产生热问题。LVDS降低了终端电阻压降,因此还降低了电路的总功耗。

1.2.3 噪声性能好

LVDS产生的电磁干扰低。这是因为低电压摆幅、低边缘速率、奇模式差分信号,以及恒流驱动器的Is尖峰只产生很低的辐射。通过减小电压摆幅和电流能量,LVDS把场强减到了最小;差分驱动器引入了奇模式传输,即等量方向相反的电流分别在传输线上传输,形成电流环路,使电流回路产生最低的电磁干扰;在差分信号的传输中,由于差分接受器只响应正负输入之差,因此当噪声同时出现在两个输入中时,差分信号的幅度并不受影响。

1.2.4 具有故障安全(fai-safe)特性确保可靠性

恒流式驱动不会对系统造成任何损害,所以LVDS驱动器可以带电插拔,另一特点是接收器的故障保抑功能。LVDS接收器在内部提供了可靠性线路,保证在接收器输入悬空、接收器输入短路以及接收器输入处于驱动器三态输出或驱动器供电终止等情况下输出可靠(约定为“1”),防止产生输出振荡。

二、LVDS数据格式

LVDS信号格式有两种,一种JEIDA的标准,一种是VESA的标准。

| VESA | Video Electronics Standards Association | 视频电子标准协会 |

| JEIDA | Japan Electronic Industry Development Association | 日本电子产业发展协会 |

- 旧LCD屏有6bit的,常见的LCD屏是8bit,新一点的LCD屏是10bit。

- LVDS的一个Port是指一个差分时钟对与3/4/5个数据差分对的组合,LVDS屏可能有1/2/4个Port

- 每个像素时钟周期对应一个Port的一个像素

- 每个像素时钟周期对应一个数据差分对通道的7bit数据,也就是串行数据速率是像素时钟Pixel Clock的7倍

2.1 VESA:6/8/10bit屏

| VESA:单port 6bit 屏:3个数据差分对+一个像素时钟差分对Pixel Clock | |||||||

| 数据差分对 | T1 | T2 | T3 | T4 | T5 | T6 | T7 |

| 0+/- | R0 | R1 | R2 | R3 | R4 | R5 | G0 |

| 1+/- | G1 | G2 | G3 | G4 | G5 | B0 | B1 |

| 2+/- | B2 | B3 | B4 | B5 | HS | VS | DE |

note:

- 时间从左T1到右T7增加

- T1=T2=T3=T4=T5=T6=T7=串行数据时钟周期

- T1+T2+T3+T4+T5+T6+T7=像素时钟周期

| VESA:单port 8bit 屏:4个数据差分对+一个像素时钟差分对Pixel Clock | |||||||

| 数据差分对 | T1 | T2 | T3 | T4 | T5 | T6 | T7 |

| 0+/- | R0 | R1 | R2 | R3 | R4 | R5 | G0 |

| 1+/- | G1 | G2 | G3 | G4 | G5 | B0 | B1 |

| 2+/- | B2 | B3 | B4 | B5 | HS | VS | DE |

| 3+/- | R6 | R7 | G6 | G7 | B6 | B7 | XX |

| VESA:单port 10bit 屏:5个数据差分对+一个像素时钟差分对Pixel Clock | |||||||

| 数据差分对 | T1 | T2 | T3 | T4 | T5 | T6 | T7 |

| 0+/- | R0 | R1 | R2 | R3 | R4 | R5 | G0 |

| 1+/- | G1 | G2 | G3 | G4 | G5 | B0 | B1 |

| 2+/- | B2 | B3 | B4 | B5 | HS | VS | DE |

| 3+/- | R6 | R7 | G6 | G7 | B6 | B7 | XX |

| 4+/- | R8 | R9 | G8 | G9 | B8 | B9 | XX |

可见:VESA的10bit屏的接口兼容8bit与6bit的屏接口,8bit屏的接口兼容6bit的屏接口。

2.2 JEIDA:8/10bit屏

| JEIDA:单port 8bit 屏:4个数据差分对+一个像素时钟差分对Pixel Clock | |||||||

| 数据差分对 | T1 | T2 | T3 | T4 | T5 | T6 | T7 |

| 0+/- | R2 | R3 | R4 | R5 | R6 | R7 | G2 |

| 1+/- | G3 | G4 | G5 | G6 | G7 | B2 | B3 |

| 2+/- | B4 | B5 | B6 | B7 | HS | VS | DE |

| 3+/- | R0 | R1 | G0 | G1 | B0 | B1 | XX |

| JEIDA:单port 10bit 屏:5个数据差分对+一个像素时钟差分对Pixel Clock | |||||||

| 数据差分对 | T1 | T2 | T3 | T4 | T5 | T6 | T7 |

| 0+/- | R4 | R5 | R6 | R7 | R8 | R9 | G4 |

| 1+/- | G5 | G6 | G7 | G8 | G9 | B4 | B5 |

| 2+/- | B6 | B7 | B8 | B9 | HS | VS | DE |

| 3+/- | R2 | R3 | G2 | G3 | B2 | B3 | XX |

| 4+/- | R0 | R1 | G0 | G1 | B0 | B1 | XX |

可见:JEIDA的10bit屏的接口不兼容8bit的屏接口 !!!

三、参考链接

LVDS屏的俩种接口:JEIDA&&VESA-CSDN博客

24Bit LVDS中的JEIDA和VESA标准差异-CSDN博客

浅谈LVDS | Frozen Sphere

LVDS和VX1详细介绍 - 道客巴巴