AXI(Advanced Extensible Interface)总线是一种高性能、低延迟的片上系统(SoC)接口标准,广泛应用于现代数字系统设计中。它允许不同的硬件组件以高效、可靠的方式进行数据传输和控制。本教程将介绍AXI总线的基本操作和关键概念,帮助读者更好地理解和使用AXI总线。

一、AXI总线概述

AXI总线是一种基于数据包传输的接口,它采用主从设备模式进行通信。主设备负责发起数据传输请求,而从设备则响应这些请求,完成数据传输。AXI总线支持多种数据传输模式,包括单向和双向传输,以及不同的数据宽度和突发长度。

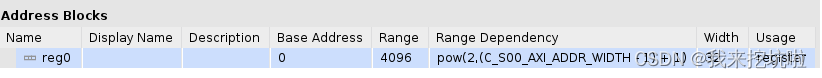

下面是关于AXI总线数据宽度和地址宽度的初始化代码。

// Users to add parameters here// User parameters ends// Do not modify the parameters beyond this line// Width of S_AXI data busparameter integer C_S_AXI_DATA_WIDTH = 32,// Width of S_AXI address busparameter integer C_S_AXI_ADDR_WIDTH = 7

二、AXI总线基本操作

1.地址映射与数据传输

AXI总线使用地址映射机制来定位和管理内存资源。主设备通过发送包含目标地址的数据传输请求来启动数据传输操作。从设备根据请求中的地址信息,从相应的内存位置读取数据或写入数据。

2.数据包格式

AXI总线使用标准的数据包格式进行数据传输。每个数据包包含有效的数据负载以及相关的控制信息和状态信息。这些信息帮助主从设备正确地解析和处理数据。

可以通过对寄存器写操作进行数据传输

.I_sys_clk_0(S_AXI_ACLK),.I_rst_n_0(!S_AXI_ARESETN),.I_err_switch_0(slv_reg31[11:10]), .I_Qspi_CPHA_0(slv_reg31[9]),.I_Qspi_CPOL_0(slv_reg31[8]),

可以通过对寄存器读操作进行数据传输

5'h7 : beginreg_data_out[0] <= err_flag_3;reg_data_out[1] <= err_flag_2;reg_data_out[2] <= err_flag_1;reg_data_out[3] <= err_flag_0;reg_data_out[4] <= O_finish_0 ;reg_data_out[6:5] <= O_finish_state_0 ;end应用层对寄存器操作格式:

#define WRITE_REG(data, base, address) *((int *)((unsigned int)base + (unsigned int)address)) = data

#define READ_REG(base, address) *((int *)((unsigned int)base + (unsigned int)address))

3.突发传输

AXI总线支持突发传输模式,允许主设备连续发送多个数据传输请求,从而提高数据传输的效率和吞吐量。从设备根据突发传输的设置,连续地读取或写入数据,减少了传输过程中的延迟。

//stream read flag logicalways @( posedge S_AXI_ACLK )beginif ( !S_AXI_ARESETN || m_axis_tready_0 )beginm_axis_tready_0 <= 0;end elsebegin if (slv_reg_rden)begincase ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] )3'h6 : beginif(m_axis_tvalid_1)m_axis_tready_0 <= 1;enddefault : m_axis_tready_0 <= 0;endcaseend endend .s_axis_aresetn_1(slv_reg4[1]),.s_axis_aresetn_0(slv_reg4[0]),.m_axis_tready_0(m_axis_tready_0), .s_axis_tvalid_0(s_axis_tvalid_0),

4.错误检测与纠正

AXI总线具有强大的错误检测和纠正机制。在数据传输过程中,如果出现错误,AXI总线能够及时发现并采取相应的纠正措施,确保数据的完整性和可靠性。

三、AXI总线操作注意事项

1.同步与异步操作

AXI总线支持同步和异步操作模式。在选择操作模式时,需要根据具体的应用场景和需求进行权衡。同步操作模式具有更高的实时性和确定性,而异步操作模式则具有更好的灵活性和可扩展性。

2.地址对齐与访问粒度

在使用AXI总线进行数据传输时,需要注意数据的地址对齐和访问粒度。某些硬件组件可能要求数据以特定的地址对齐方式进行访问,而访问粒度则决定了每次数据传输的字节数。

3.传输超时与重试机制

为了避免因数据传输失败而导致的系统崩溃或性能下降,AXI总线提供了传输超时和重试机制。当数据传输请求未能及时完成时,可以启用超时机制来中断请求;同时,重试机制允许在特定条件下重新尝试传输操作。

四、总结

AXI总线作为一种高性能、低延迟的片上系统接口标准,为现代数字系统设计提供了强大的支持。通过掌握AXI总线的基本操作和关键概念,读者可以更好地利用AXI总线实现高效、可靠的数据传输和控制功能。在实际应用中,需要根据具体需求选择合适的操作模式和参数设置,以充分发挥AXI总线的性能优势。