相关阅读

静态时序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

目录

指定值

指定端口/引脚列表

简单使用

set_case_analysis命令用于对电路进行特定模式的设定,例如对于一个工作在正常模式下的芯片,其扫描触发器的测试引脚应该设定为0;对于一个时钟选择器的选择引脚,在特定模式工作时应该为确定值。这个命令很有用,因为它可以帮助减少很多不必要的时序路径分析。

set_case_analysis指令的BNF范式(有关BNF范式,可以参考以往文章)为:

set_case_analysisvalue port_or_pin_list//注:该命令的port_or_pin_list参数一定要放在value参数后该命令可以指定端口或引脚处是恒定的1或0,或者端口或引脚处仅允许上升沿或下降沿。

指定值

参数value指定了端口或引脚处的固定值或转换方向。对于固定值,它可以是1、0、one或zero。对于转换方向,它可以是rising、falling、rise或fall。

指定端口/引脚列表

指定一个端口/引脚列表,包含端口对象或引脚对象,如果有多于一个对象,需要使用引号或大括号包围。

简单使用

本文仅讨论固定值的模式分析,这是多数情况下该命令的使用方式。

首先我们可以解决静态时序分析:SDC约束命令create_clock详解一文中出现的时序路径混乱问题,原文的图7如本文图1所示,首先在输入端口clk_1和clk_2定义两个时钟。

create_clock -period 10 [get_port clk_1]

create_clock -period 15 [get_port clk_2]

图1 有两个时钟驱动的电路单元

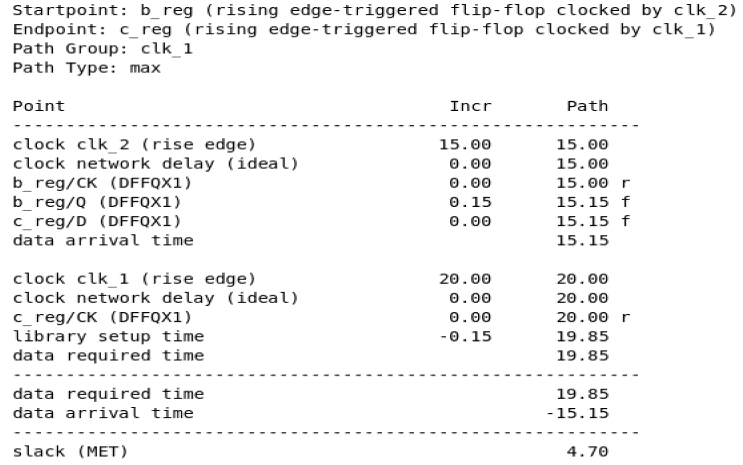

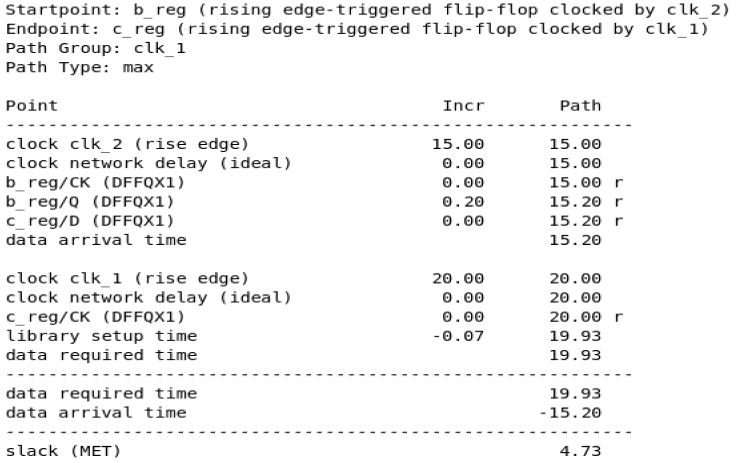

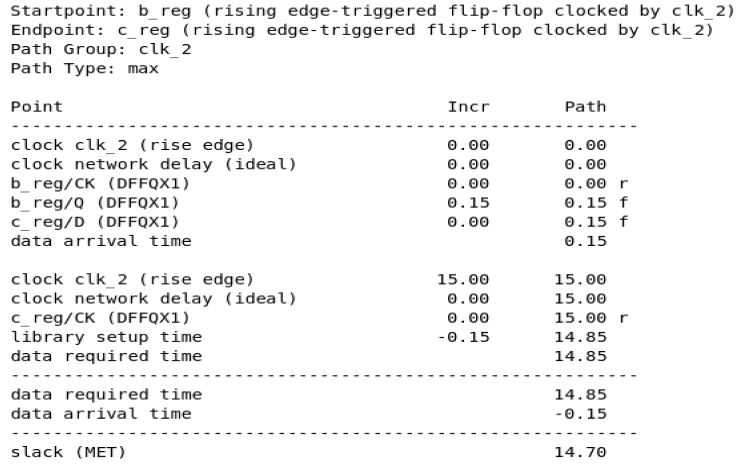

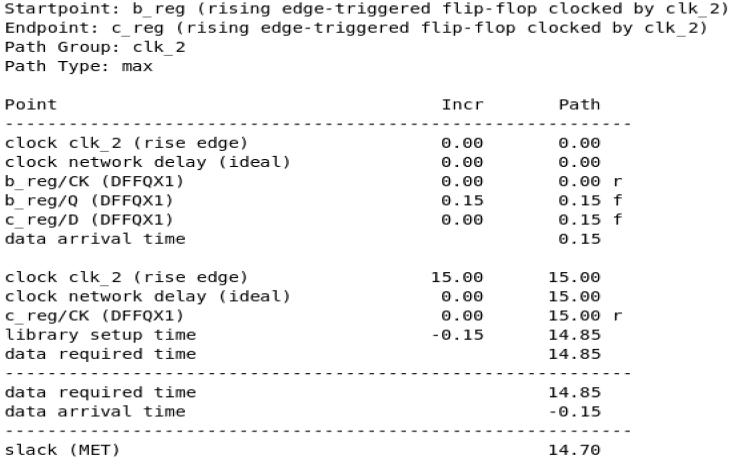

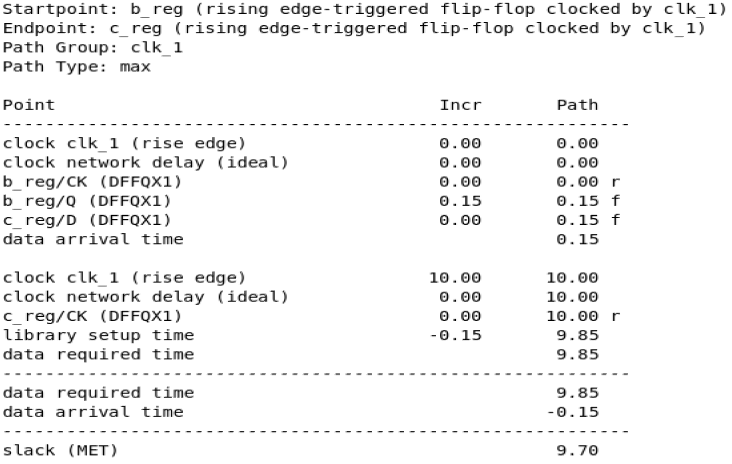

对于上面的电路,本意是b_reg触发器和c_reg触发器同时受时钟clk_1或时钟clk_2之一触发,但如果不使用set_case_analysis命令,在使用report_timing命令后会出现时钟clk_2和时钟clk_1之间的时序分析报告,如图2、图3所示,我们真正需要的是图4的时序报告(本文如不加说明,默认时序报告为建立时间报告)。

图2 发射时钟是clk_2,捕获时钟时clk_1

图3 发射时钟是clk_2,捕获时钟时clk_1

图4 发射时钟是clk_2,捕获时钟是clk_2

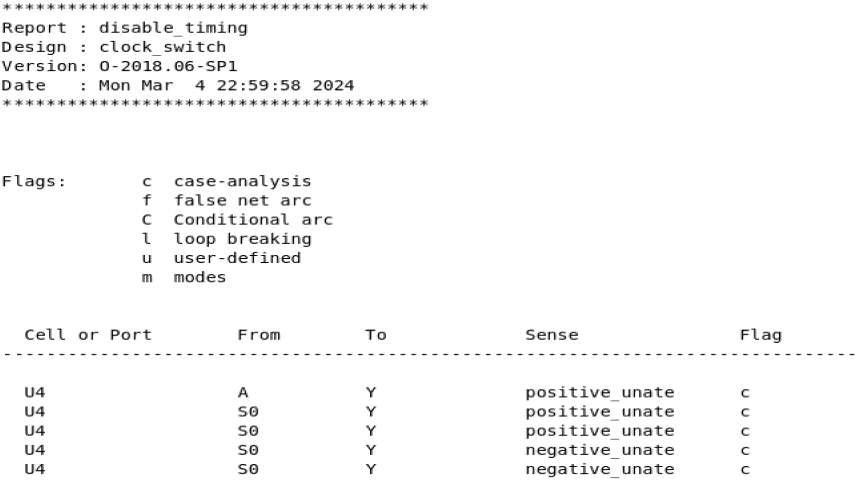

下面我们使用set_case_analysis命令,固定选择端sel的信号为0,可以使用report_case_analysis命令查看指定的模式分析值,如图5所示。还可以使用report_disable_timing命令查看此时失效的时序弧,如图6所示,可以看到此时选择引脚S0到输出引脚Y的时序弧和输出引脚B到输出引脚Y的时序弧都失效了。此时的时序分析结果如图7和图8所示。

set_case_analysis 0 [get_port sel]

图5 模式分析报告

图6 失效时序弧报告

图7 发射时钟和捕获时钟都是clk_2

图8 发射时钟和捕获时钟都是clk_2

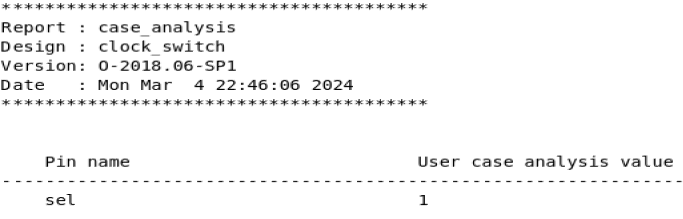

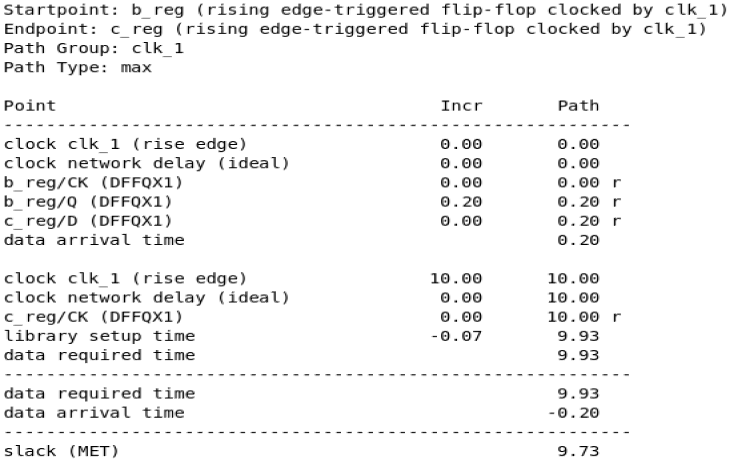

下面我们使用set_case_analysis命令,固定选择端sel的信号为1,可以使用report_case_analysis命令查看指定的模式分析值,如图9所示,可以看到之前设置的0被更改为了1。还可以使用report_disable_timing命令查看此时失效的时序弧,如图10所示,可以看到此时选择引脚S0到输出引脚Y的时序弧和输出引脚A到输出引脚Y的时序弧都失效了。此时的时序分析结果如图11和图12所示。

set_case_analysis 1 [get_port sel]

图9 模式分析报告

图10 失效时序弧报告

图11 发射时钟和捕获时钟都是clk_1

图12 发射时钟和捕获时钟都是clk_1

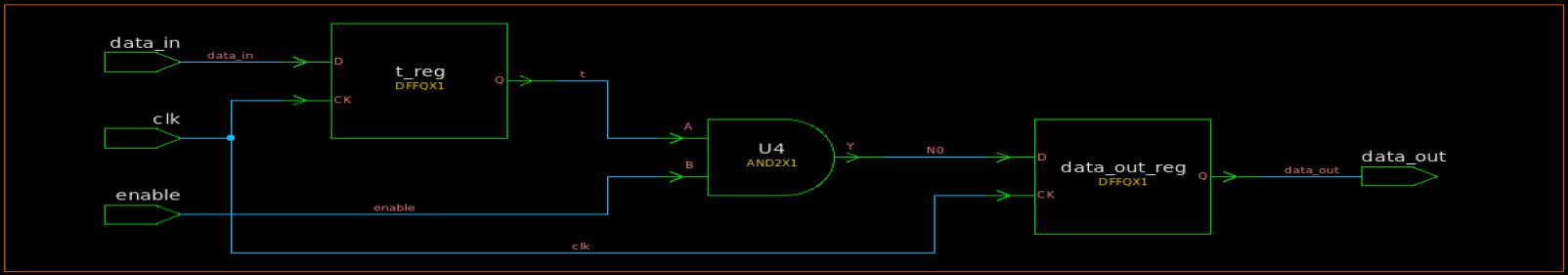

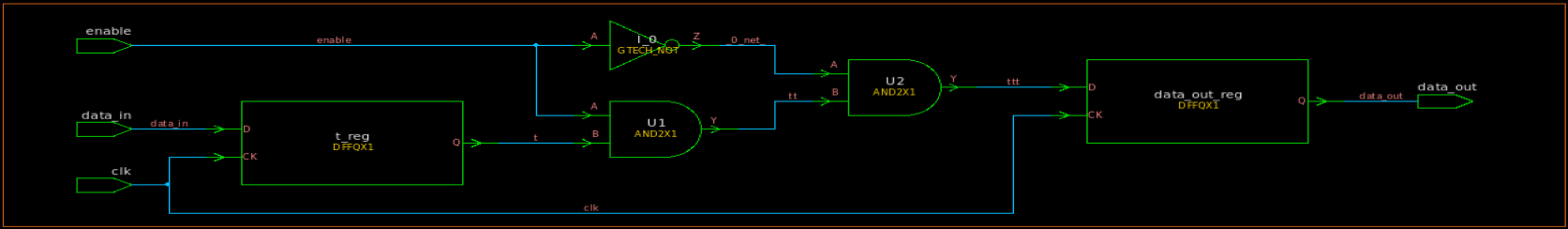

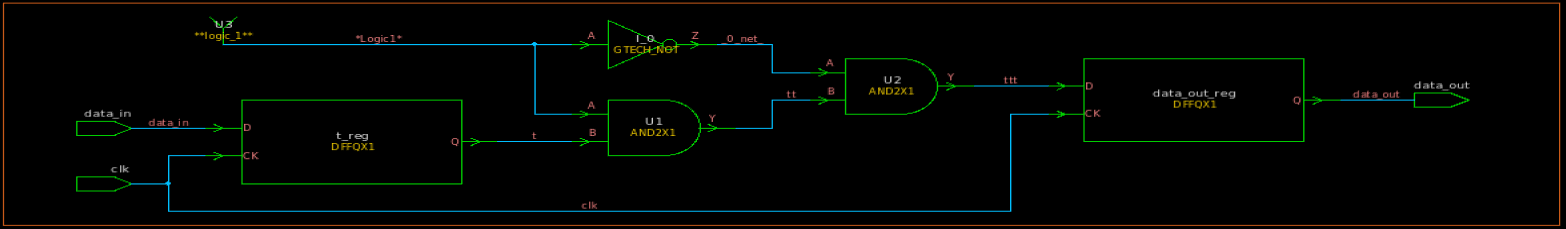

set_case_analysis命令还会导致设定的值沿着时序路径向后传播,从而打断某些时序路径(使这些路径不能出现信号翻转),例如对于图13所示的电路图。

图13 一个简单的例子

首先在输入端口clk定义一个时钟。

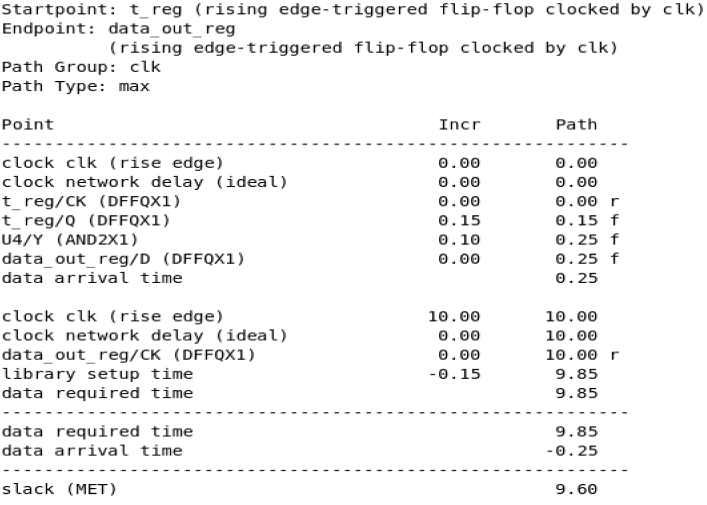

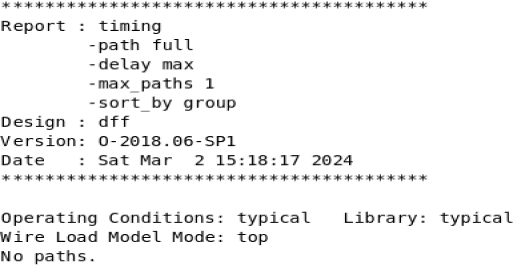

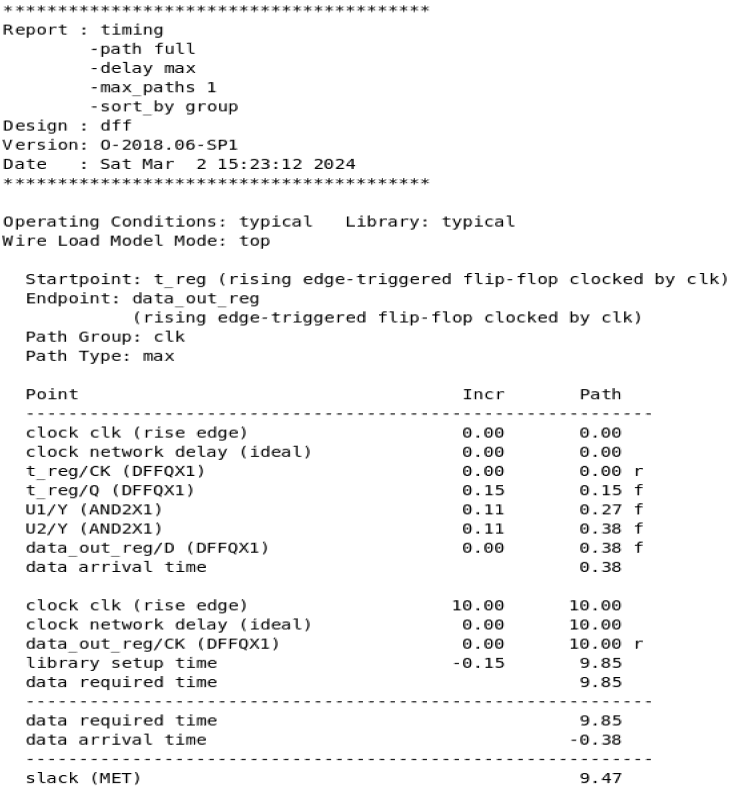

create_clock -period 10 [get_port clk]此时如果直接使用report_timing命令,则t_reg和data_out_reg之间的时序路径会正常报告,如图14所示。

图14 两个触发器间的时序报告

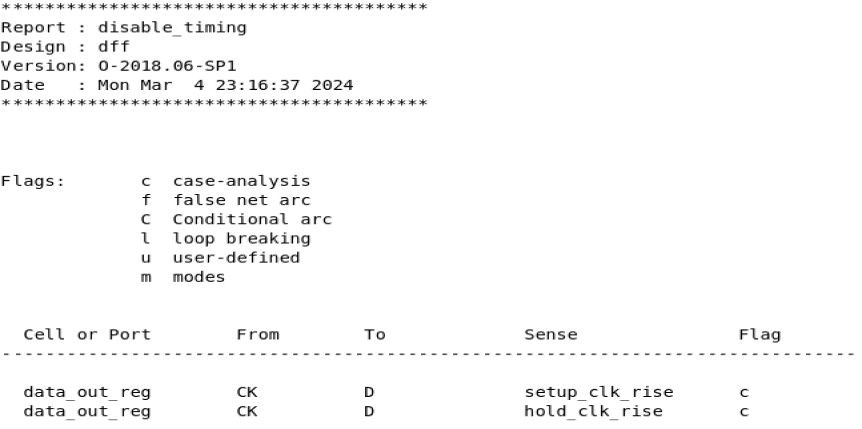

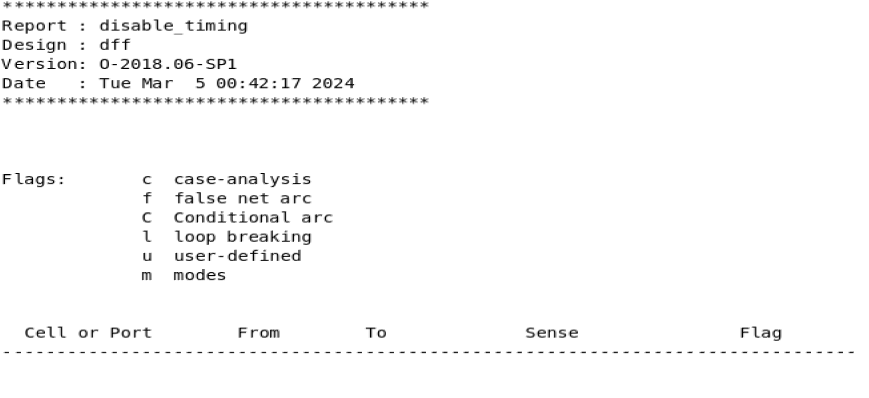

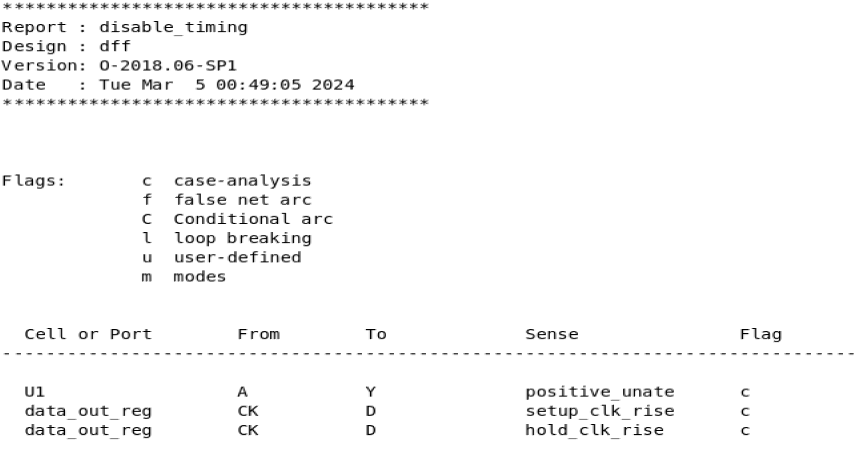

下面使用set_case_analysis命令固定使能信号enable为0,可以使用report_disable_timing命令查看此时失效的时序弧,如图15所示,我们发现,这和图10报告有所差异,按照之前的分析,此时应显示单元U4从输入引脚A和输入引脚B到输出引脚Y的时序弧失效,但图15却显示触发器data_out_reg从时钟引脚CK到输入引脚D的建立时间和保持时间时序弧失效了,这是因为DC检测到此时D引脚的值为固定值0,因此无需检测建立时间和保持时间。触发器t_reg和触发器data_out_reg之间的时序路径消失了(实际上,某点的固定值会使通过该点时序路径直接消失),如图16所示。

set_case_analysis 0 [get_port enable]

图15 失效时序弧报告

图16 两个触发器间的时序路径消失了

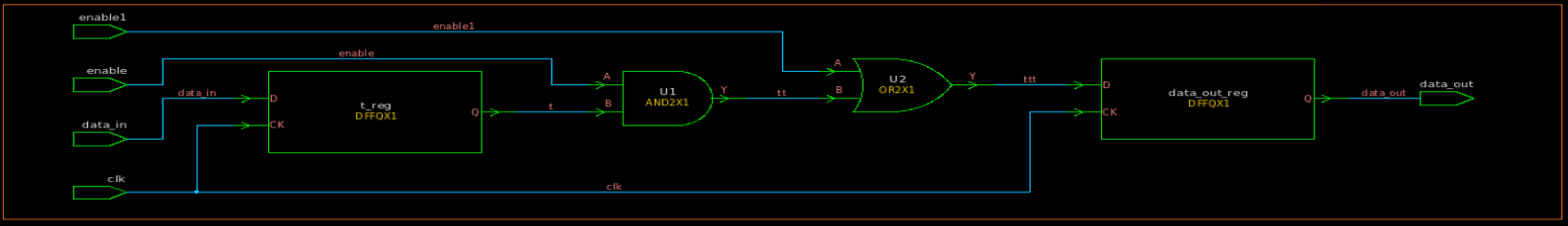

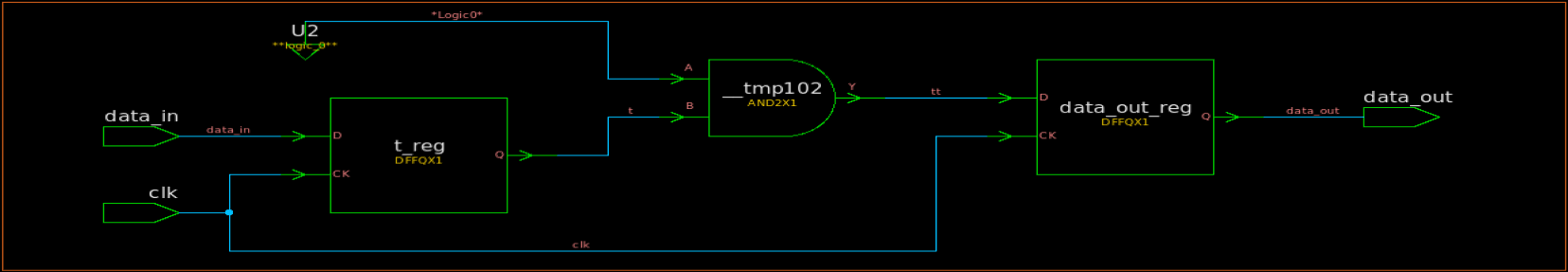

图17所示的例子在与门U4后又添加了一个或门,这样的话,即使与门U1的输出固定为0,也不会传播到触发器data_out_reg的D引脚,此时使用set_case_analysis 0 [get_port enable]命令后的失效时序弧报告如图18所示,可以看到固定值0传播至或门U2输入,并使或门U2的输入到输出的时序弧失效了,这里没有明确给出U1的的输入到输出的时序弧失效,它们被包含在U2时序弧的失效中,报告只会列出传播终点的时序弧失效情况。如果此时使用set_case_analysis 0 [get_port enable_1]命令,则定值0会继续传播至触发器data_out_reg的D引脚,此时的失效时序弧报告就和图15一样了。

图17 定值0不会传播至触发器输入

图18 失效时序弧报告

在编写Verilog代码时,直接将与门的一个输出引脚固定为0,这也会打断时序路径(假设电路没有被逻辑优化),如图19所示的电路图。

图19 编写代码时指定引脚值为0

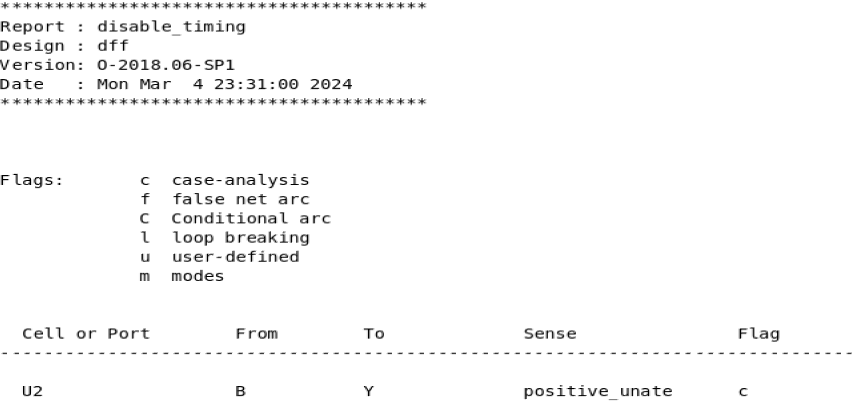

在图19中,我们设法使得某些器件不被优化掉,并构造了一个奇怪的电路图。此时在逻辑上讲,与门的输出是一个固定值0,使用report_disable_timing命令查看此时失效的时序弧,如图20所示,可以看到此时居然和图15的报告一模一样,这代表着DC正确识别了这种情况,并且从Flag栏的c也可以看出,此时DC按照模式分析的规则传播了这个固定值0。此时使用report_timing命令无法看到t_reg和data_out_reg之间的时序路径,如图21所示。

图20 失效时序弧报告

图21 两个触发器间的时序路径消失了

但是我们再来看一下图22所示的电路图(假设电路没有被逻辑优化),可以看出按照逻辑关系,与门U2的输出是一个固定值0,但是此时使用report_timing命令可以看到t_reg和data_out_reg之间的时序路径,如图23所示。此时使用report_disable_timing命令查看此时失效的时序弧,图24显示此时没有失效的时序弧。这代表了,即使DC会考虑直接指定常数和使用模式分析指定常数时电路的逻辑传播情况,但不会考虑更复杂的情况。

图22 与门U2的输出引脚值为0

图23 两个触发器间的时序报告

图24 失效时序弧报告

如果此时在编写Verilog代码时又将enable信号固定为1(假设电路没有被逻辑优化),这和使用set_case_analysis固定输入端口enable为1是一样的,如图25所示,则时序路径又会被打断。使用report_disable_timing命令查看此时失效的时序,如图26所示,其中固定值1传播至触发器data_out_reg的输入引脚D,导致触发器data_out_reg从时钟引脚CK到输入引脚D的建立时间和保持时间时序弧失效了,并且固定值1还传播到了U1的1输入端A,这导致了与门U1输入端A到输出端Y的时序弧失效了,但这不会继续传播下去了,因为一个与门输入固定为1并不会使输出也为固定值(但其实这条是多余的,因为触发器data_out_reg从时钟引脚CK到输入引脚D的建立时间和保持时间时序弧都已经失效了)。

图25 编写代码时指定引脚值为0

图26 失效时序弧报告

最后要注意的是,固定值的传播会在到达时序路径终点而停止,并不会继续传播下去,比如图25中的data_out_reg到输出端口的时序路径并不会因为触发器时钟引脚CK到输入引脚D的时序弧失效而被打断。

最后做个总结,不管是直接明确使用固定值还是使用模式分析命令set_case_analysis指定固定值,固定值都会沿着逻辑传播(与门的某个输入为固定0,或门的某个输入为固定1,与门的所有输入固定为1,或门的所有输入固定为0,等情况),直到传播终点为止(固定值不能继续传播下去),时序弧失效报告中,只显示传播终点的失效时序弧(因为这也能间接说明传播路径中的时序弧也失效了),如果传播终点是触发器的输入端,则触发器从时钟引脚CK到输入引脚D的时序弧会失效,此时不会进行建立时间和保持时间的检查。