导语

芯片是电子产品的核心,为了满足不同应用领域的需求,芯片被分为不同的等级。其中,工业级芯片适用于工业自动化、控制系统和仪器仪表等领域,对芯片的可靠性和稳定性要求较高。这些芯片通常具有更宽的工作温度范围(-40°C至85°C),能够在更恶劣的工作环境下正常运行,如高温、低温、湿度和振动等。

本篇将从静电可靠性入手,解答ArtInChip芯片在静电相关验证项目的成果,打造“工业级”芯片ESD天花板。

Part 01.静电可靠性:电子产品无法忽视的指标

对于芯片来说,其可靠性可初略分为静电可靠性、生产制造可靠性、寿命可靠性。

静电可靠性的相关验证项目,主要包含HBM (Human Body Model,人体对产品静电放电模型)、CDM(Charge Device Model,产品带静电对外放电模型)、LU(Latch-Up,闩锁)。

HBM、CDM是面向半导体器件的静电放电测试模型,用于指导半导体的制造、封测、PCBA加工、装配测试等生产过程中的ESD管控,其管控标准应远低于所有被加工的元器件中最低ESD耐压等级。而在进行产品设计选型时,应尽量选用ESD耐压等级高的元器件,以提高产品的可靠性。

Part 02.静电抗扰度:等级划分及行业标准要求

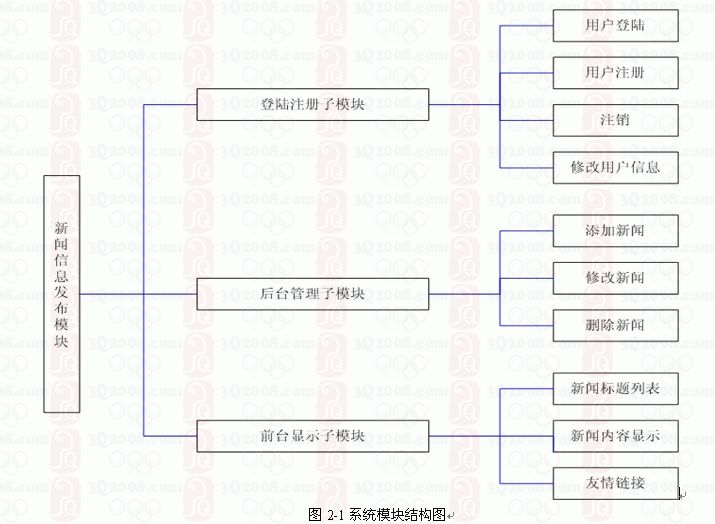

如表1所示为JEDEC和AEC-Q100标准针对半导体器件HBM的静电抗扰度等级划分,表2所示为针对CDM的静电抗扰度等级划分。而AEC-Q100通常要求HBM通过级别为±2000V;CDM通过级别为±500V,角引脚±750V。

表1:HBM静电抗扰度等级划分

表2:CDM静电抗扰度等级划分

Part 03.精密防护:匠芯创打造“工业级”ESD天花板

ESD可能会发生在I/O与电源、地之间,可能会发生在不同的I/O之间,也可能出现在电源和地之间,因此对于ESD保护电路的设计需要考虑所有可能发生ESD的情形。有一种常见的芯片ESD设计方案,没有直接的电压钳位保护结构,而是利用全芯片整个电路的阱与衬底的接触空间作为ESD电流泄放通道,这种方案成本较小但静电性能有限。

为了显著提高芯片的ESD防护水平,匠芯创在芯片ESD设计上从整个芯片防护及可能发生的ESD情形考虑。每个I/O电路中设计相应的ESD保护电路包含二极管、MOS管、静电泄放器的组合,在发生ESD时能提供电源到地直接低阻抗电流泄放通道;并在合适的位置增加芯片电源和地引脚数量,有效增强抗ESD能力;此外严格把控版图设计,避免出现ESD薄弱环节。

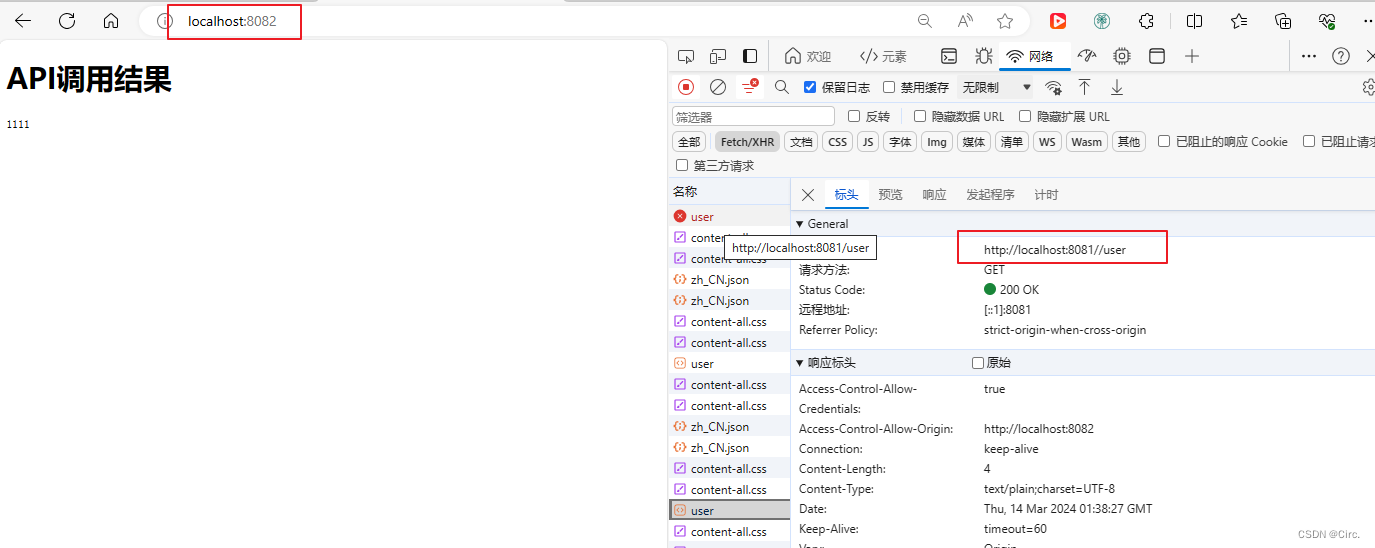

匠芯创D21x、D13x、D12x系列产品在静电可靠性项目测试结果表现十分抢眼,远超行业标准要求。其中,在HBM项目上至少通过±4kV Class-3A级别,超出AEC-Q100要求的±2kV Class-2级别;在CDM项目上至少通过±750V C2b级别,超出AEC-Q100要求的±500V C2a级别。

表3:匠芯创产品在静电可靠性项目测试结果

Part 04.严控成本:匠芯创板级ESD兼具性价比优势

在板级ESD方面,通常严格、完善的ESD设计意味着成本的增加。

基于匠芯创系列产品设计的两层板EVB方案,能达到接触放电±6kV工业三级以上级别,不需要过多的防护器件及增加板卡层数,在满足工规行业静电可靠性的同时,还能大大降低成本和设计复杂度,极具性价比。

详情服务

对芯片感兴趣的小伙伴欢迎来【芯智云城】!