主页: 元存储博客

文章目录

- 前言

- 1. Channel

- 2. Dimm

- 3. Rank

- 4. Bank

- 5. Row

- 6. Column

- 7. Beat

- 8. Burst Length

- 总结

前言

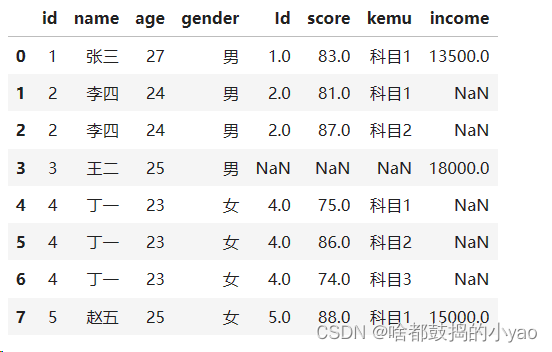

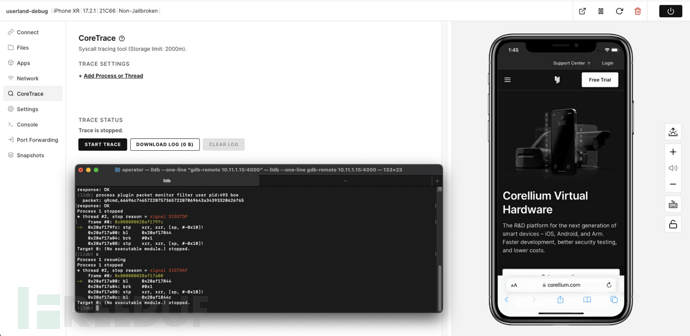

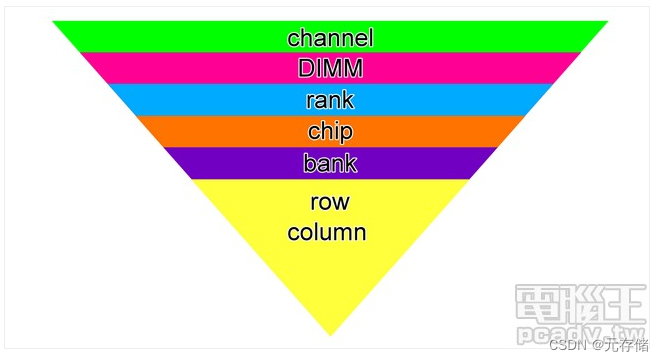

从CPU至DRAM晶粒之间依据层级由大至小为channel>DIMM>rank>chip>bank>row/column。

图片来源: 电脑王

DRAM层级关系

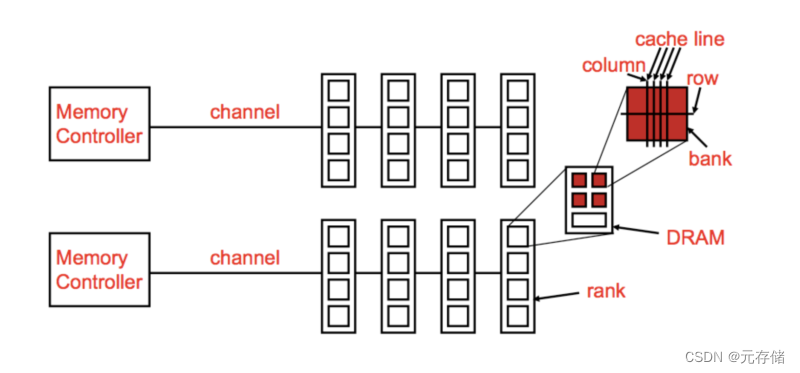

DRAM 不同层级结构示意

来源: DRAM Nomenclature explained,thebeardsage

上图有:

两个 channel,

每个 chanle 有 4 个 Dimm,

每个 Dimm 有 1 个 rank

每个 rank 有一个 DRAM chip

一个 chip 有 4 个 Bank

这仅仅是一个示意, 不同的 DRAM 存储器是不同的。

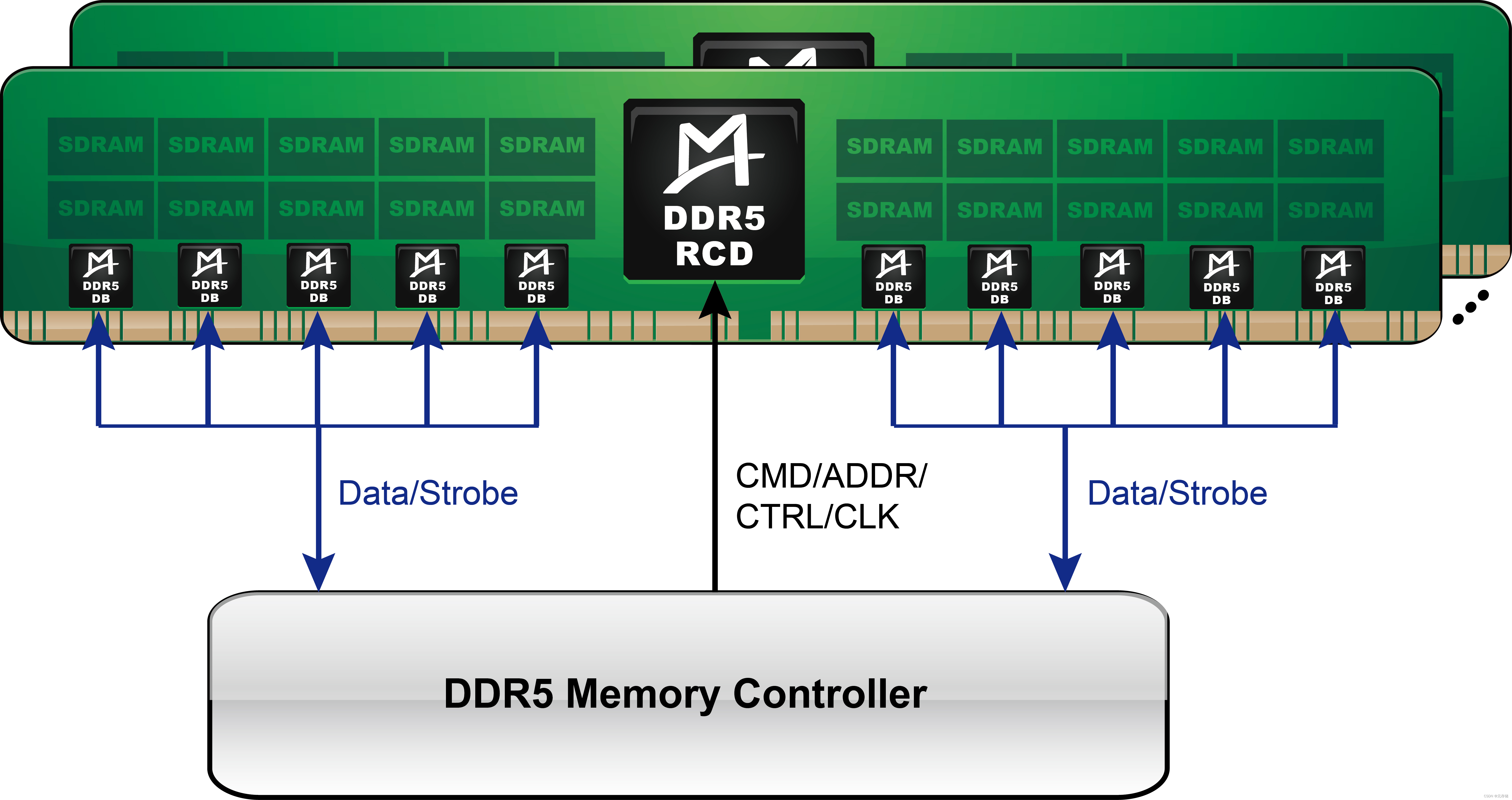

1. Channel

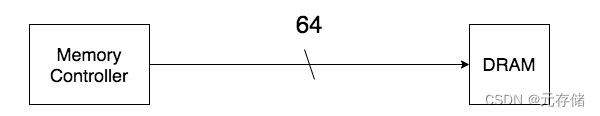

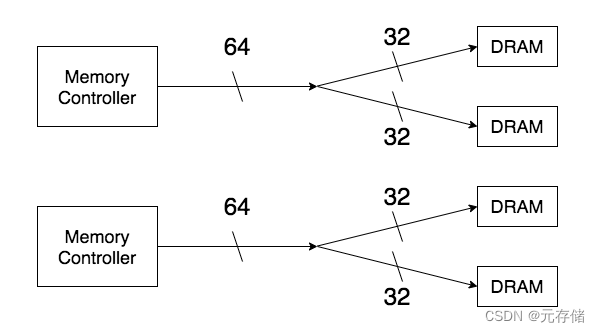

存储控制器和DRAM模组之间的连接线称为channel (通道).

一个存储器可以只有一个 controller 和 1 个 channel.

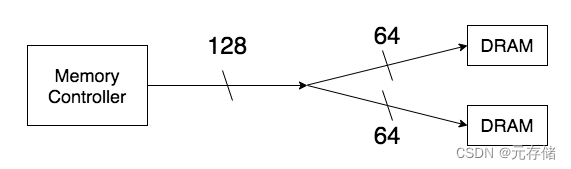

也可以一个 Controller 带两个 channel。

还可以含两个 controller, 每个 controlle 有两个 channel。

这两个 controller 相互独立, 可以并行,提高带宽。

2. Dimm

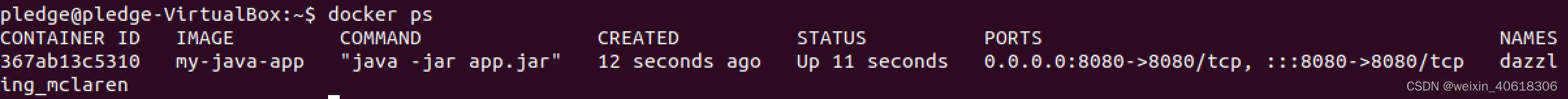

Dimm 实物图

Dimm(dual in-line memory module),是计算机内存, 常见位宽为 64 bit。我们买的内存条就是长这个样子。

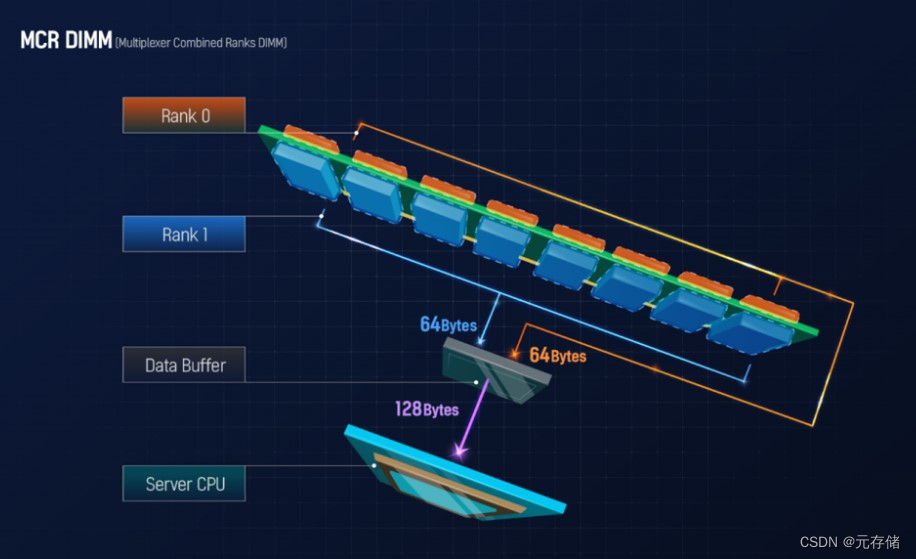

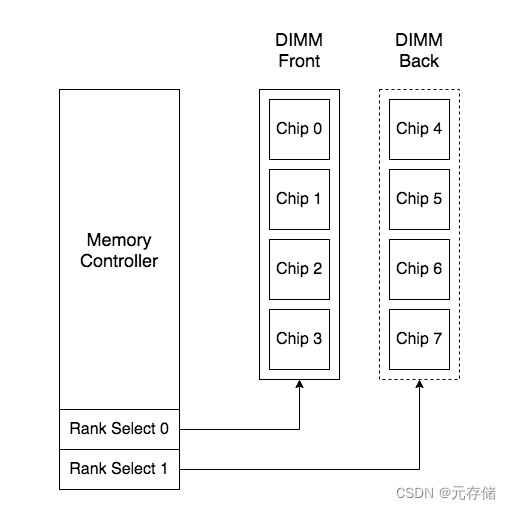

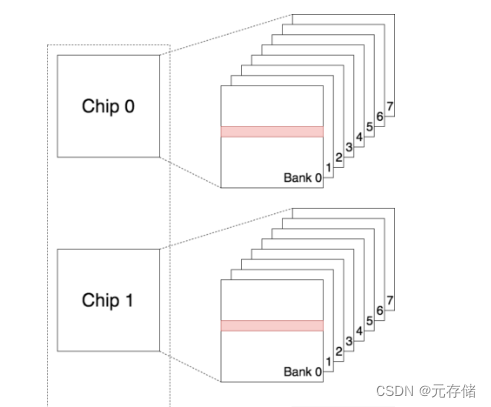

3. Rank

拿出内存条看的话, Dimm 有两面,每一面是一个 Rank。

同一个 Rnak 含有多个 chip, 一个 Rank 里的 chips 共用命令线和地址线,但吐出不同的数据。

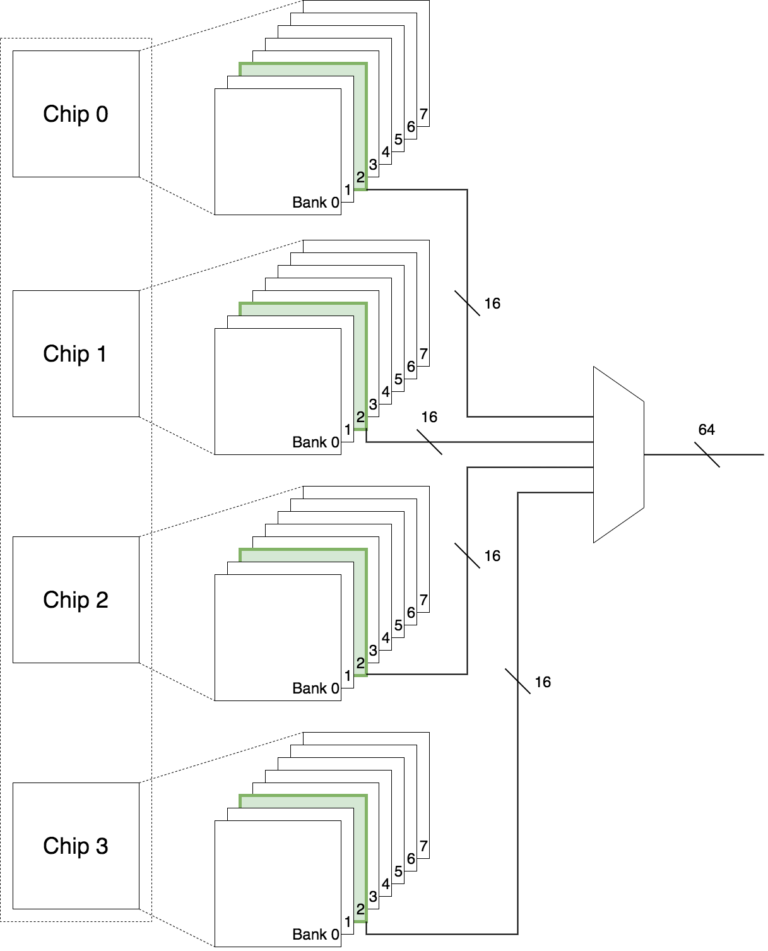

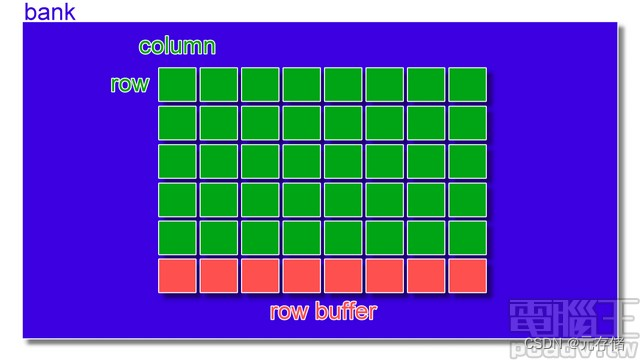

4. Bank

一个 Chip 里有很多 bank, 这些 bank 在不同的 cycle 吐出数据, 可以 pipiline 流水线访问。一个Rank内的所有 DRAM chip都会同时访问同一个Bank位置。

假设需要从第 2 Bank 中的一个位置读取 64 字节的数据。在这种情况下,每个 DRAM chip 将从各自的Bank 中提供 16 字节的数据。

Bank 通过 Row 地址 和 Column 地址访问数据。

Row 地址即行地址, Column 即列地址。

5. Row

row 即 bank 中的一行, 一个 row 地址,对应到多个 chip 中所有 bank 的同一行。

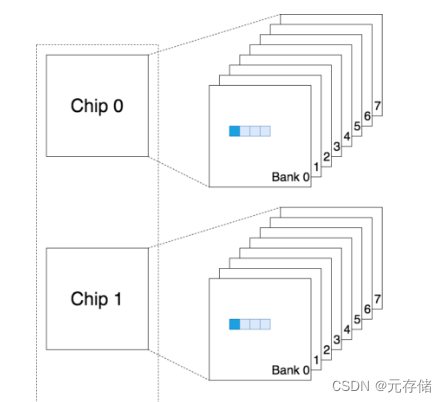

6. Column

Column 是 DRAM 最小访问单元,每个 column 地址可以获取多个 chip 中这个 column address 对应的数据。读的长度取决于 burst length.

7. Beat

SDR RAM 一个周期传一次数据, DDR 一个周期传输两次数据(上升沿和下降沿各一次)

8. Burst Length

一个Read command 可以读多个 column 的数据, 比如 burst length 是 128 bit, 一个 column data 是 32 bit, 那么一次可以读 4 个 column.

总结

参考文献

-

圖解RAM結構與原理,系統記憶體的Channel、Chip與Bank

-

DRAM Nomenclature explained

声明

本文仅为学习交流目的。

文中部分文字和图片来源于互联网,列在参考的文献,但可能有遗漏。如有侵权,请告知我删除。