快速链接:

- 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈

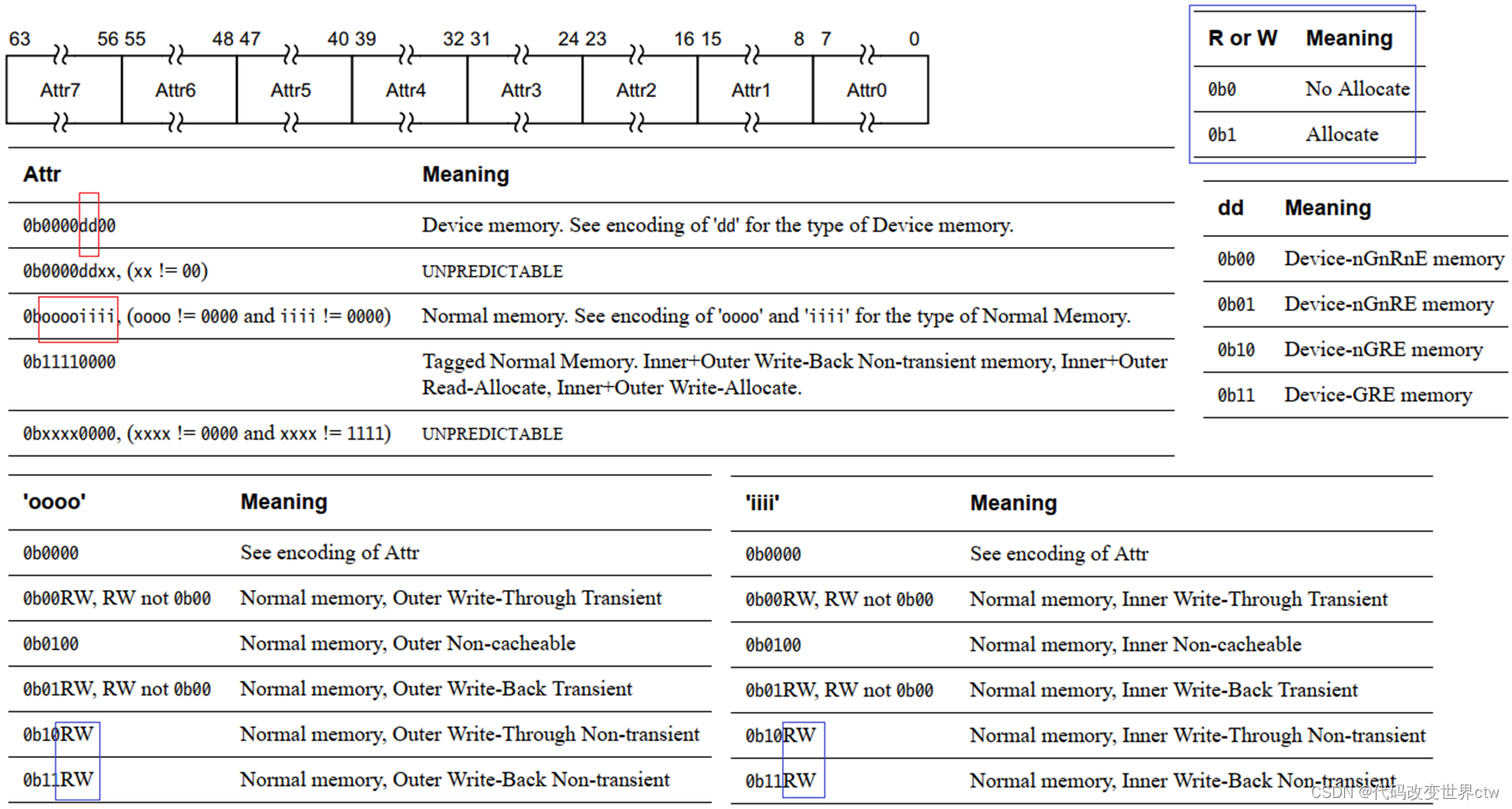

在学习MMU章节时,我们发现在页表的entry中,BIT[4:2]指向了MAIR寄存器,该寄存器描述了内存属性,其实就是cache的缓存策略属性(inner\outer\shareable\cacheable)。 也就是页表中的每一个entry都指向了一个这样的Attr。 那么我如果把MMU disable了呢? 就没有页表的事了,那么此时缓存的策略是怎样的呢?

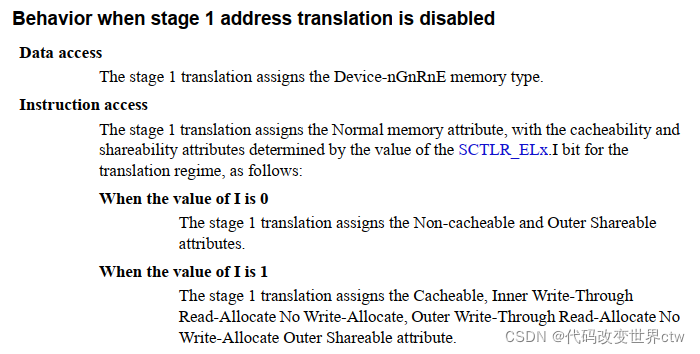

我们在ARM ARM的D5.2.9 The effects of disabling a stage of address translation章节的Behavior when stage 1 address translation is disabled 中找到答案

MMU关闭后,cache的缓存策略总结如下:

- data的访问,视为 Device-nGnRnE

- 指令的访问,要根据

SCTLR_ELx.I的值:

(1)SCTLR_ELx.I == 0,视为Non-cacheable、Outer Shareable

(2)SCTLR_ELx.I == 1,

Cacheable

Inner Write-Through, Read-Allocate, No Write-Allocate

Outer Write-Through, Read-Allocate, No Write-Allocate

Outer Shareable attribute

关注"Arm精选"公众号,备注进ARM交流讨论区。