视频链接

USB HUB电路设计01_哔哩哔哩_bilibili

USB HUB 电路设计

1、USB HUB基本介绍

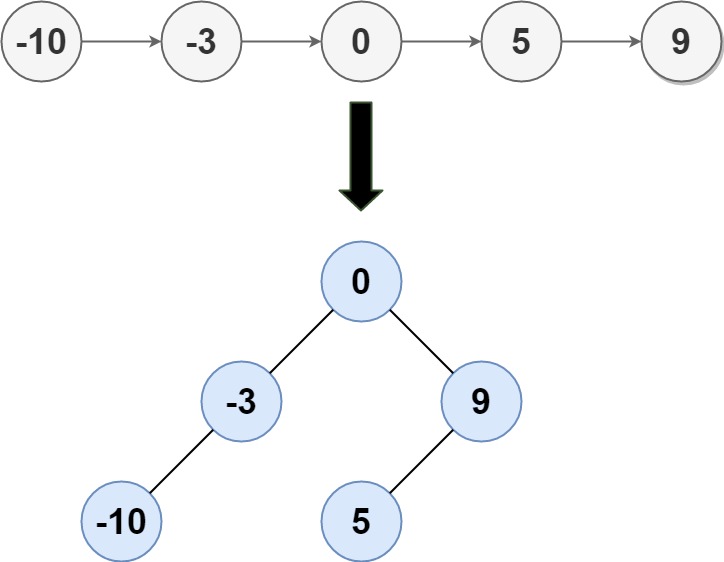

USB Hub,指的是一种可以将一个USB接口扩展为多个,并可以使这些接口同时使用的装置。

Hub也是大家常说的集线器,它使用星型拓扑结构连接多个USB接口设备。

USB Hub,可连U盘、风扇、鼠标、键盘等等。

HUB的特点:

1、可将一个USB接口扩展成多个独立工作的USB接口

2、直接与电脑相连, 无须外接电源,简单好用

3、电脑自动识别安装, 无须驱动程序,即插即用,插拔自如

4、支持USB2.0,速度高达480Mbps,向下兼容USB1.1

5、内置电流过载短路保护装置

HUB的分类:USB HUB根据所属USB协议可分为USB2.0 HUB、USB3.0 HUB与USB3.1 HUB。

USB2.0 HUB支持USB2.0,理论带宽达480Mbps;

USB3.0 HUB支持USB3.0,向下兼容USB2.0/1.1,理论带宽达5Gbps;

USB3.1 HUB支持USB3.1,向下兼容USB3.0/2.0/1.1,理论带宽达10Gbps.

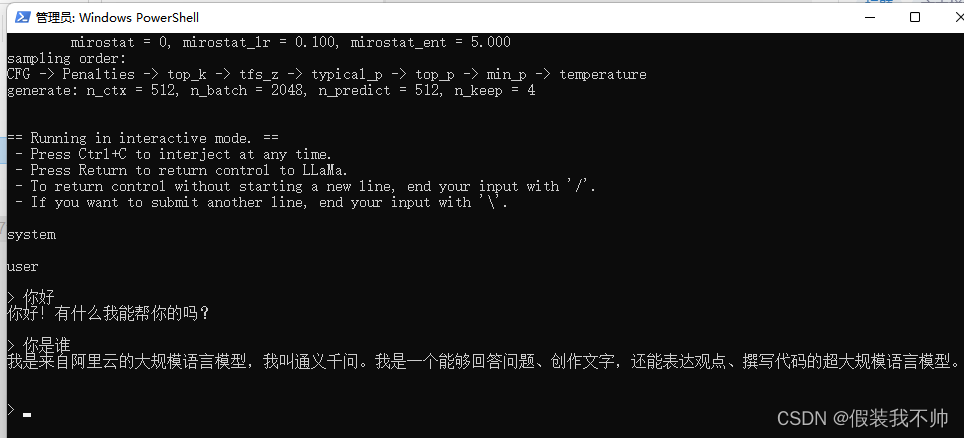

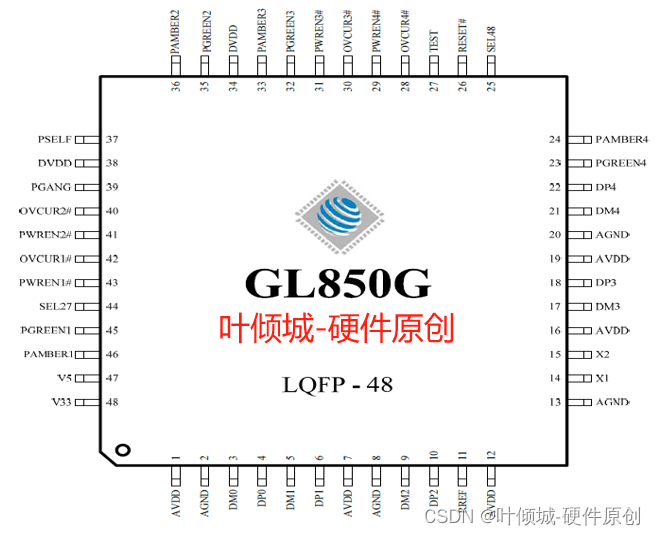

创维的GL850G主控芯片:

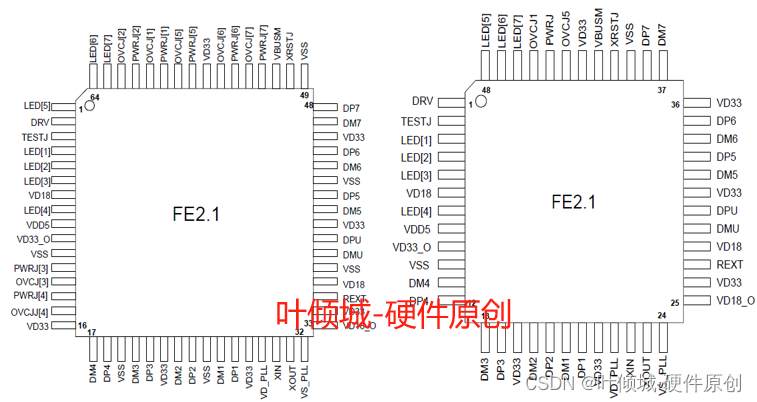

2、(汤铭)FE2.1 48-PIN LQFP ; USB 2.0 一拖七(★)

汤铭-Terminus

高速7端口USB2.0集线器控制芯片

无需编程。FE2.1芯片是高度集成,高品质,高性能,低能耗,总体花费低的高速7端口USB2.0集线器解决方案。

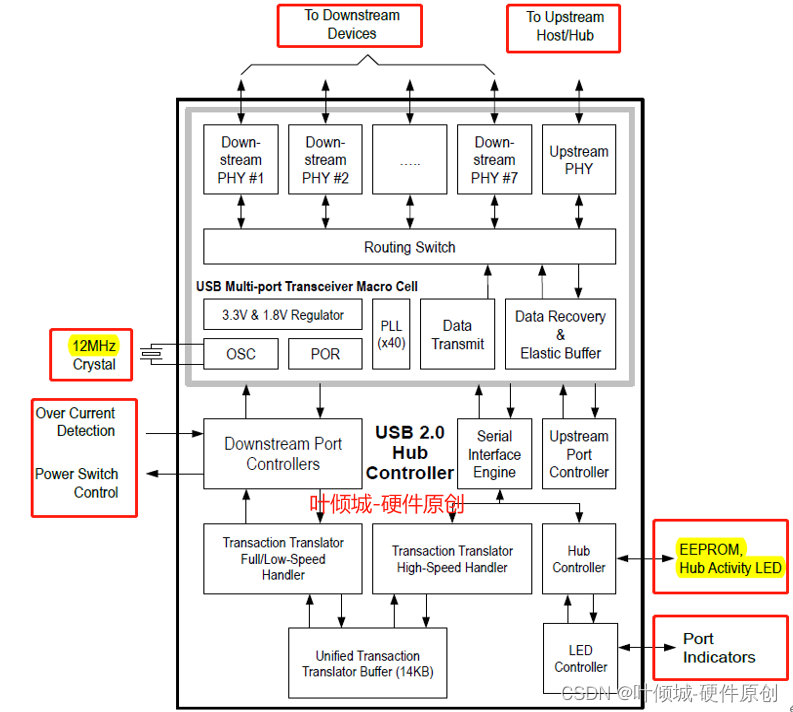

2.1、结构及功能框图

64脚的比48脚的(除了电源数目以外)多 (VSS多4 VD33多1 )

PWRJ[2、3、4、5、6、7] 和 OVCJ[2、3、4、6、7] (共11根控制线)

2.2、管脚定义(FE2.1)

电源管脚

| 管脚符号 | 类型 | 描述 |

| VDD5 | Power | 5V power input for integrated 5V→3.3V regulator. |

| VD33_O | Power | 3.3V power output from 5V→3.3V integrated regulator–a 10μF output capacitor is required. |

| VD33 | Power | 3.3V Power Input. |

| VD18_O | Power | 1.8V power output from 3.3V→1.8V integrated regulator–a 10μF output capacitor is required.(稳压) |

| VD18 | Power | 1.8V power input. |

| VD_PLL | Power | 1.8V Power for PLL. |

| VS_PLL | Power | Ground for PLL. |

| VSS | Power | Ground. |

其他

| 管脚符号 | 类型 | 描述 |

| DMU | UTU | The D- pin of the Upstream Facing Port. |

| DPU | UTU | The D+ pin of the Upstream Facing Port. |

| DM[0:7] | UTD | The D- pin of the xx Downstream Facing Port. |

| DP[0:7] | UTD | The D+ pin of the xx Downstream Facing Port. |

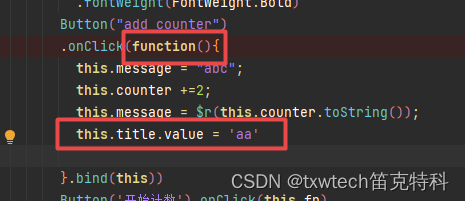

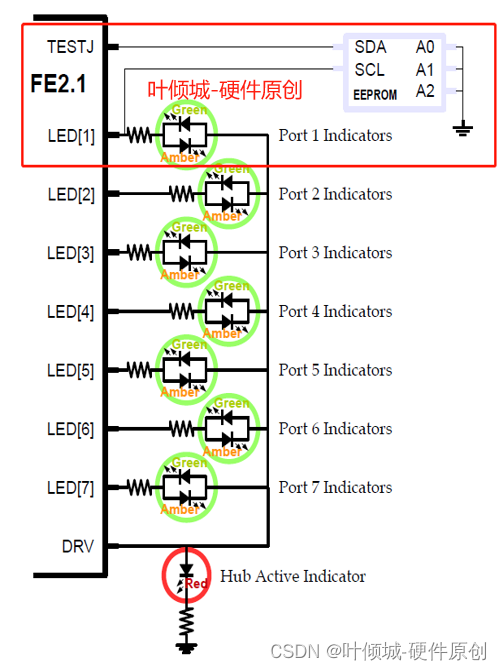

| DRV | O | Driving Control for all LED. 驱动控制所有LED。 //DRV和LED配合使用,作为LED的正极。 LED[1-7]:LED是用于指示每一路下行数据的通信状态,当数据在传输的时候,灯会闪烁。// |

| TESTJ | IO-PU | Test Mode Enable during hardware reset, active low.Otherwise,SDA,Serial Data/Address pin for external Serial EEPROM. // TESTJ 和LED[1],配合驱动外部的EEPROM:可以外挂,写一些数据// |

| LED[1] | O/ IO-PU | LED Control for the 1st Downstream Facing Port Status, and SCL, Serial Clock pin for external Serial EEPROM. |

| LED[2-7] | O/I-PU | LED Control for the 2-7 Downstream Facing Port Status. |

| PWRJ[X] | OD | Power Enable for X Downstream Facing Port, active low. 使能第X个下游面向端口的电源,低有效。 //48PIN的只有PWRJ; 64PIN的PWRJ[1-7]// |

| OVCJ[X] | I-PU | Over-current Detect for X Downstream Facing Port, active low. 过电流检测为第X下游面向端口,低有效。 //48PIN的只有OVCJ[1]和OVCJ[5]; 64PIN的OVCJ[1-7]// |

| REXT | Analog I/O | 2.7KΩ(±1%) resistor should be connected to VSS to provide internal bias reference. 一个2.7KΩ(±1%)电阻应连接到VSS以提供内部偏置参考。 |

| VBUSM | I | The VBUS Monitor of upstream facing port. 上行接口的VBUS监视器。 //串电阻,检测主USB是否接入// |

| XRSTJ | I | External Reset, active low, is an optional source of chip reset signal. The minimum low pulse width is 10 μs. |

| XIN | OSC | 12 MHz Crystal Oscillator input |

| XOUT | OSC | 12 MHz Crystal Oscillator output. |

2.3、FE2.1设计注意事项

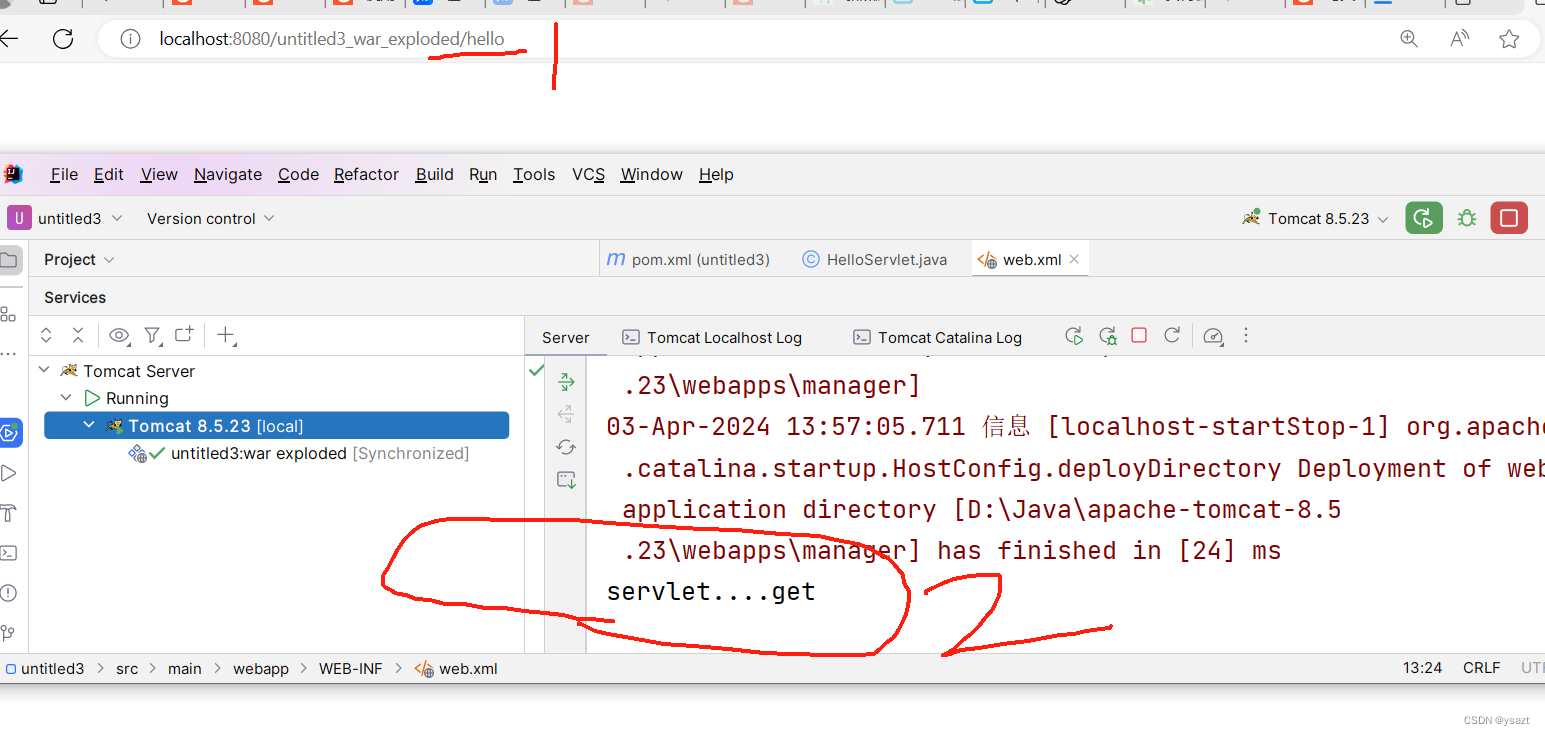

2.4、FE2.1硬件实战(★)

建议:图中的40脚,再接一个0.1UF的电容到地,RC复位。

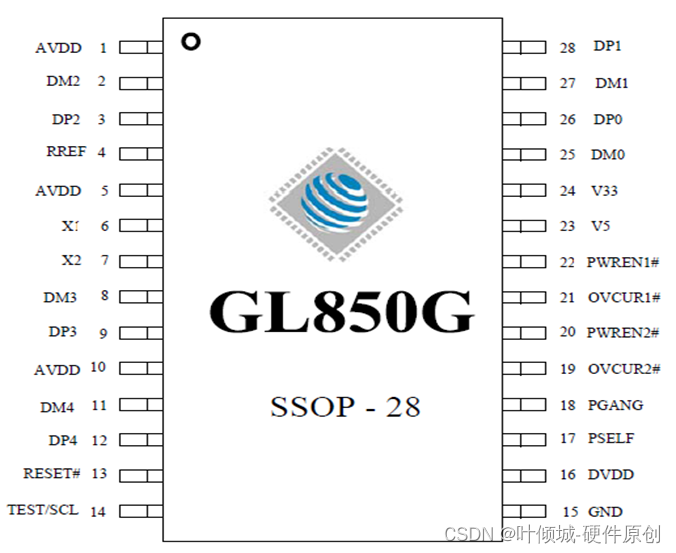

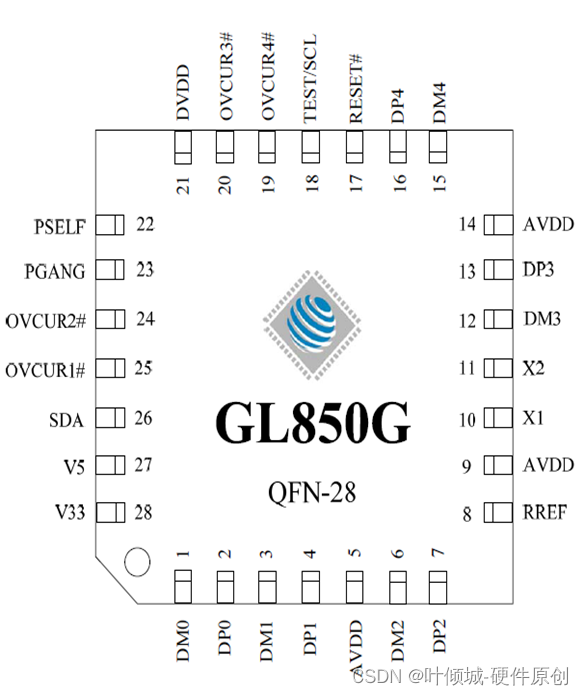

3、(创惟)GL850G-SSOP28 PIN ; USB2.0一拖四 (★)

台湾---创惟科技股份有限公司 創惟科技股份有限公司

GL850G拥有低耗电、温度低及接脚数减少等产品特性。

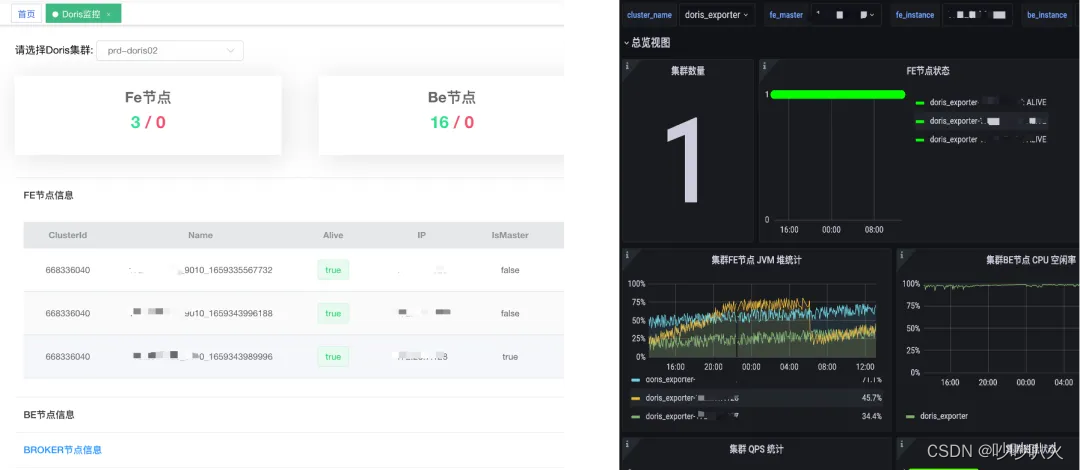

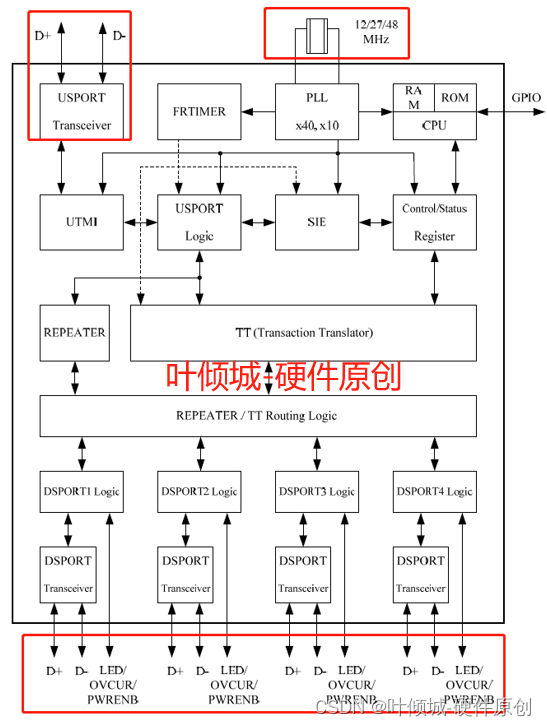

3.1、结构及功能框图

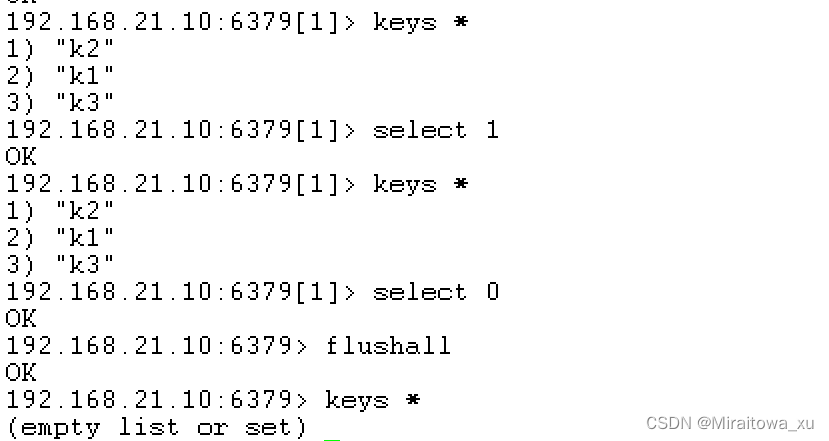

3.2、管脚定义(GL850G-SSOP28)

3.2.1、电源

3.2.2、USB Interface

3.2.3、Hub Interface

3.2.4、Clock and Reset Interface

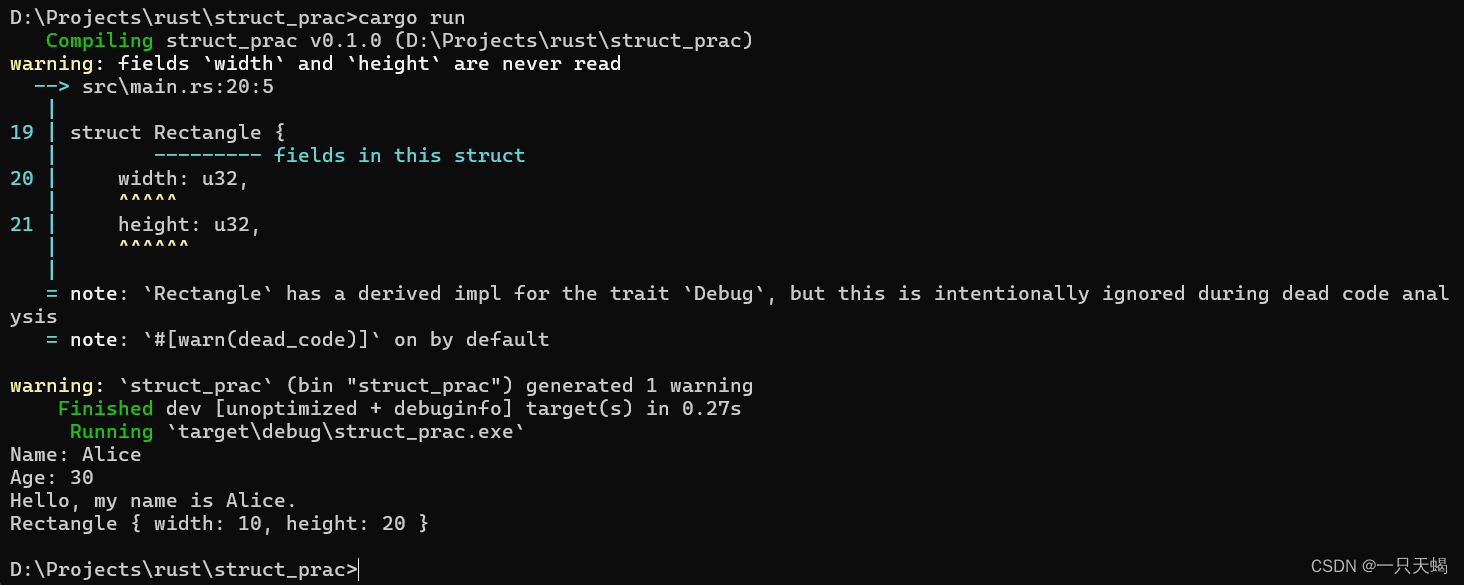

3.3、GL850G硬件实战

3.4、GL850G设计注意事项

4、USB layout设计要求

4.1、布局要求

1、USB接口靠近板边放置,避开其他高速信号

2、ESD保护器件和Common mode choke(共模电感、共模扼流圈)应该尽可能的靠近USB接口放置。

3、USB转换芯片与USB连接器应该尽可能的靠近,以减少走线的长度。其晶振不可放置过远,2个防漂移电容放晶振旁边。

4、用于去耦和消除高频噪声干扰的磁珠和去耦电容应该尽可能的靠近USB连接器放置。

5、USB电压稳压器尽可能靠近连接器放置。

4.2、布线要求

1、USB差分阻抗控制:USB2.0/USB3.0——90Ω(±10%),对内等长误差2mil。

2、USB差分信号尽量以完整的地平面为参考平面;

3、USB差分信号与其他时钟、高速信号保持至少5W以上间距。

4、USB电源线尽量粗,最好采用铺铜处理,USB2.0为0.5A,USB3.0为1A。并且机壳地与板内地的短接电感两端采用铺铜处理。