文章目录

- Verilog端口文件(仅做示范用)

- 对应的tb文件

- 相应代码

在数字IC设计过程中,根据顶层生成testbench时存在很多重复性工作,因此为了提高工作效率,特地开发此脚本。

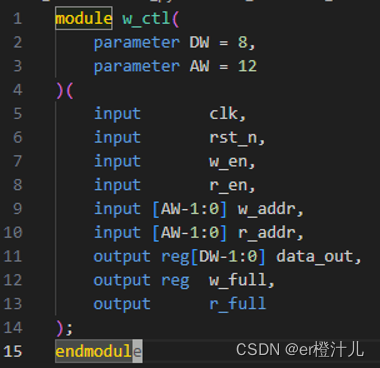

Verilog端口文件(仅做示范用)

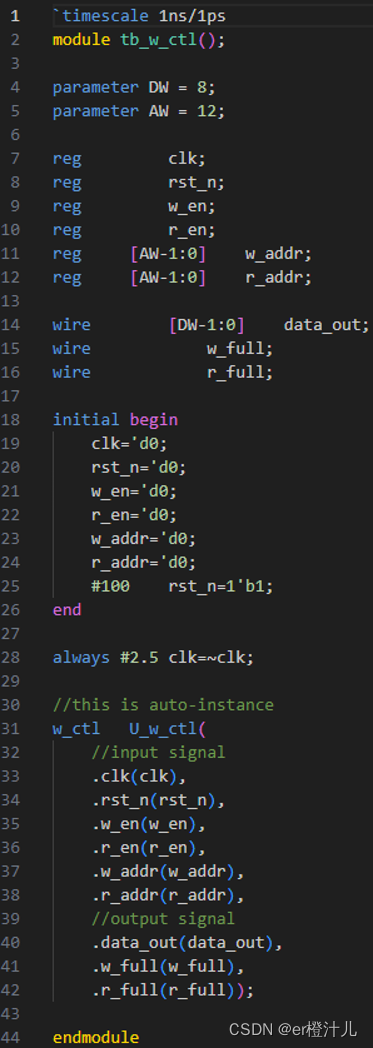

对应的tb文件

相应代码

import re

with open("w_ctl.v","r") as verilog_f:lines=verilog_f.read()

intf_in=re.findall(r"input\s+(?:\[\S+:\d+\])?\s+(\w+)",lines)

intf_in_reg=re.findall(r"input\s+(\[\S+:\d+\])?\s+(\w+)",lines)

intf_ou=re.findall(r"output\s+\S*?(?:\[\S+:\d+\])?\s+(\w+)",lines)

intf_ou_wire=re.findall(r"output\s+\S*?(\[\S+:\d+\])?\s+(\w+)",lines)

mod=re.search(r"module\s+(\w+)",lines)

par=re.findall(r"parameter\s+\w+\s?=\s?\d+",lines)

with open("tb.v","w") as instance_f:instance_f.write("`timescale 1ns/1ps\n")instance_f.write("module tb_"+mod.group(1)+"();\n")instance_f.write("\n")for para in par:instance_f.write(para+";\n")instance_f.write("\n")for match_in_reg in intf_in_reg:instance_f.write("reg\t\t"+match_in_reg[0]+"\t"+match_in_reg[1]+";\n")instance_f.write("\n")for match_ou_wire in intf_ou_wire:instance_f.write("wire\t\t"+match_ou_wire[0]+"\t"+match_ou_wire[1]+";\n")instance_f.write("\n")instance_f.write("initial begin\n")for ini in intf_in:instance_f.write("\t"+ini+"=\'d0;\n")for ini in intf_in:if(ini=="rst_n"):instance_f.write("\t#100\t"+ini+"=1\'b1;\n")instance_f.write("end\n")instance_f.write("\n")for ini in intf_in:if(ini.endswith("clk")):instance_f.write("always #2.5"+"\t"+ini+"=~"+ini+";\n")instance_f.write("\n")instance_f.write("//this is auto-instance\n")instance_f.write(mod.group(1)+"\tU_"+mod.group(1)+"(\n")instance_f.write("\t//input signal\n")for match_in in intf_in:instance_f.write("\t."+match_in+"("+match_in+"),\n")instance_f.write("\t//output signal\n")for match_ou in intf_ou[:-1]:instance_f.write("\t."+match_ou+"("+match_ou+"),\n")instance_f.write("\t."+intf_ou[-1]+"("+intf_ou[-1]+"));\n")instance_f.write("\n")instance_f.write("endmodule")

学习更多IC知识,请关注