一、时序分析的基本概念

1. 时钟

理性的时钟模型是一个占空比为50%且周期固定的方波:

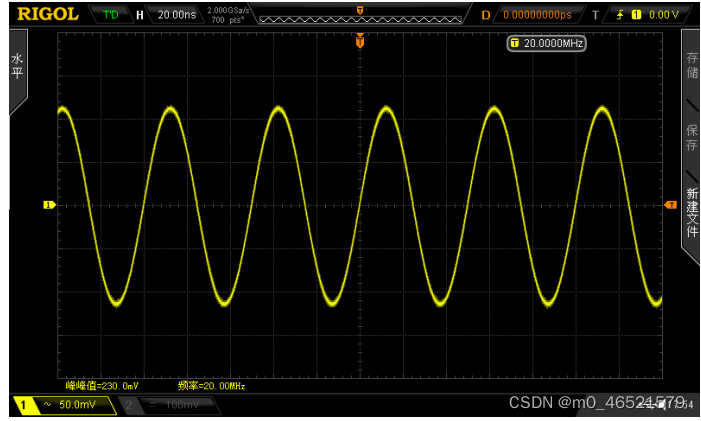

实际电路中输入给FPGA的晶振时钟信号是正弦波:

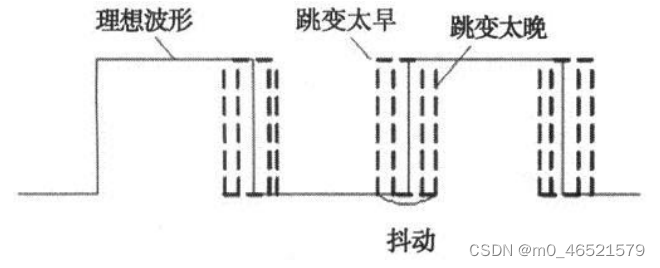

2. 时钟抖动

Clock Jitter,时钟抖动,相对于理想时钟沿,实际时钟存在不随时钟存在积累的、时而超前、时而滞后的偏移。

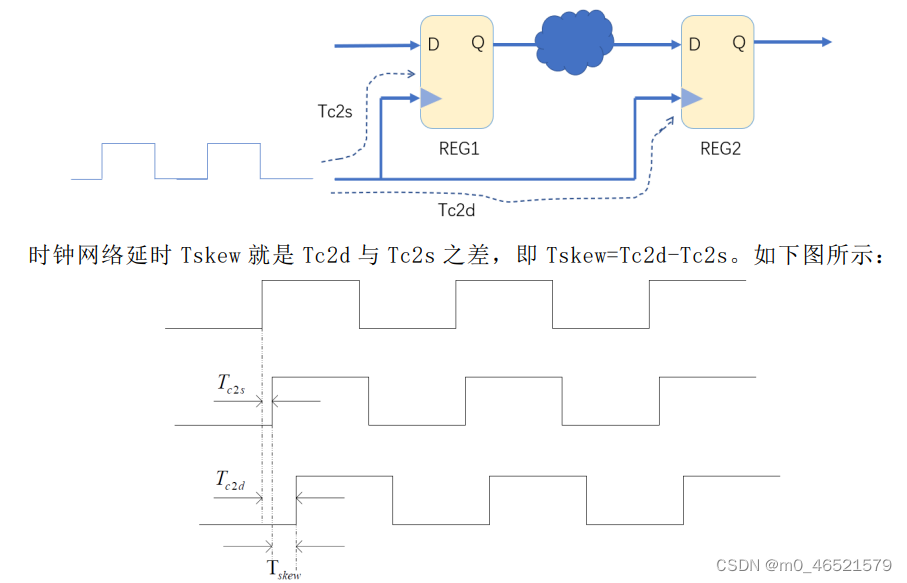

3. 时钟偏差

Clock Skew:时钟偏差,同一个时钟域内的时钟信号到达数字电路各个部分所用时间的差异。

4. 建立时间和保持时间

建立时间,Setup Time,Tsu,时钟上升沿之前数据必须稳定的最短时间。若不满足建立时间,数据无法进入寄存器,寄存器的数据采样会失败。

保持时间,Hold Time,Th,时钟上升沿之后数据必须稳定的最短时间。若不满足保持时间,数据无法进入寄存器,寄存器的数据采样也会失败。

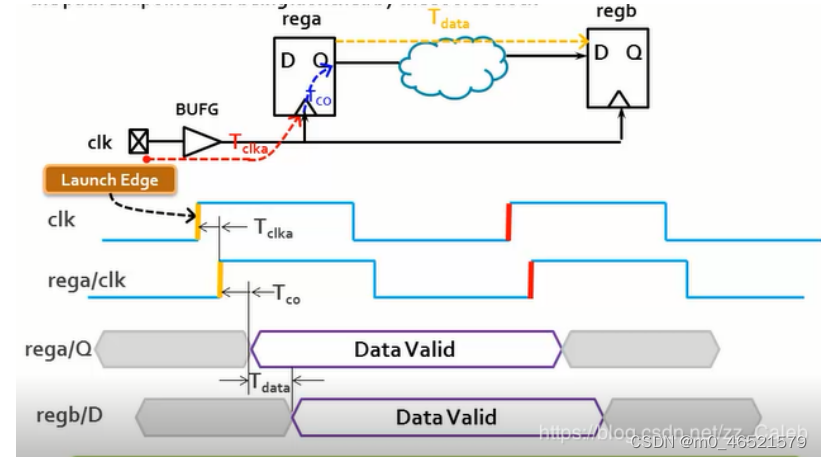

5. 发起沿和采样沿

rega和regb使用同一个时钟信号,rega在Launch Edge发送数据,regb下一个时钟周期的Capture edge采样到rega送入的数据,reag和regb中间可能还有一些组合逻辑。

二、时序分析的基本公式

1. 时序分析的基本路径

时序分析的基本路径包括:

(1)管脚输入和寄存器之间的路径(pin2reg)

(2)寄存器和寄存器之间的路径(reg2reg)

(3)寄存器和管脚输出之间的路径(reg2pin)

(4)管脚输入和管脚输出之间的路径(pin2pin)

2. 数据到达时间和时钟到达时间

(1)数据到达时间(Data Arrival Time)

数据在发送沿发送之后,经过多长时间会到达接收寄存器的数据端口,即到达regb的D端口的时刻。

(a)通常选择launch edge作为零时刻基准点

(b)数据经过Tco时间,到达Q端口。

(c)数据从Q端口,要经过组合逻辑,以及布线的线延时才能到达接收端的D端口。

3. 建立时间的裕量

建立时间的裕量, Setup slack

建立裕量为正值说明两个寄存器有合格的建立关系,建立裕量为负值说明两个寄存器建立关系不满足,会导致采样出错。

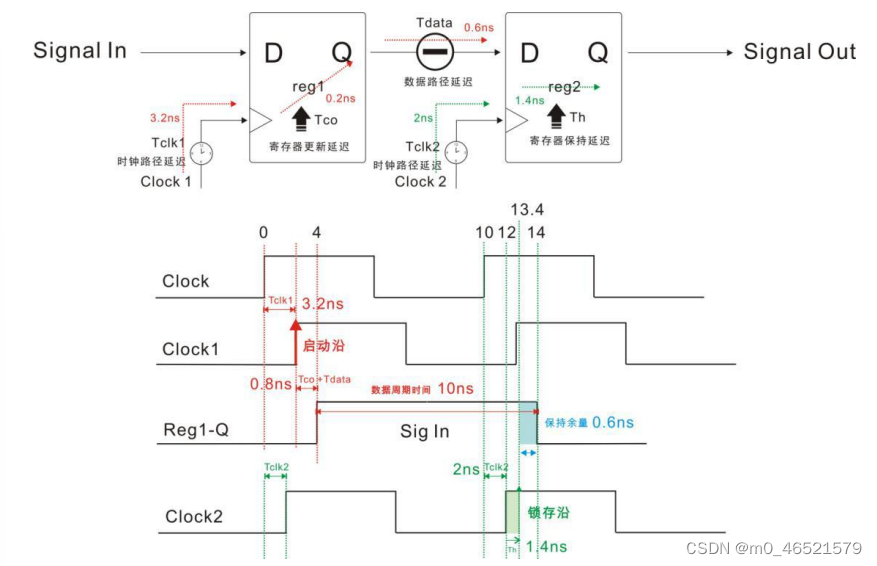

数据到达reg2 D端的时间为:

启动沿时间+Tclk1+Tco+Tdata

= 0 ns + 3.2ns + 0.2ns + 0.6ns

= 4ns

reg2能够保证采样正确,所要求数据到达的时刻

Tclk + Tclk2 - Tsu

= 10ns + 2ns - 1.4ns

= 10.6ns

建立裕量:

Setup Slack = Data Required Time - Time Arrival Time

= 10.6 ns - 4 ns

= 6.6 ns

4. 保持时间的裕量

保持时间的裕量,Hold Slack

保持裕量为正值说明两个寄存器有合格的保持关系,保持裕量为负值说明两个寄存器保持关系不满足,也会导致采样出错。

数据保持时间 Data Hold Time

= 启动沿 + Tclk1 + Tco + Tdata + 数据周期时间

= 0 ns + 3.2 ns + 0.2 ns + 0.6 ns + 10 ns

= 14 ns

数据锁存时间 Data Required Time

= 锁存沿 + Tclk2 + Th

= 10 ns + 2 ns + 1.4 ns

= 13.4 ns

保持裕量 Hold Slack

= 14 ns - 13.4 ns

= 0.6 ns