CLB模块是可配置的逻辑块,和FPGA的CLB有些不同。

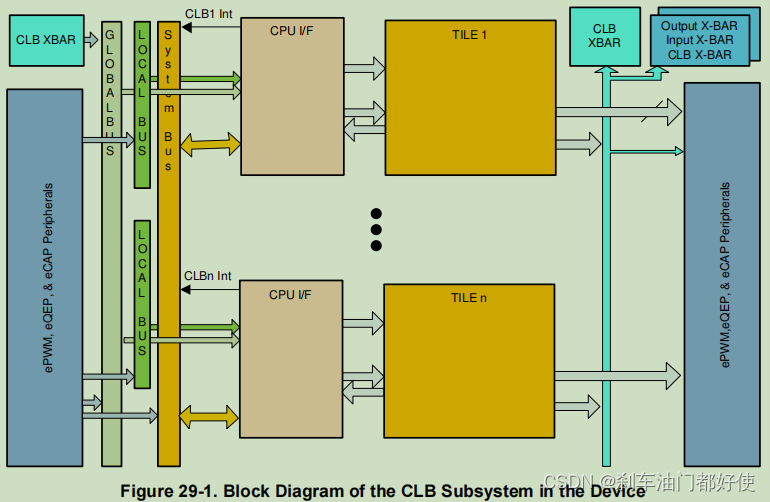

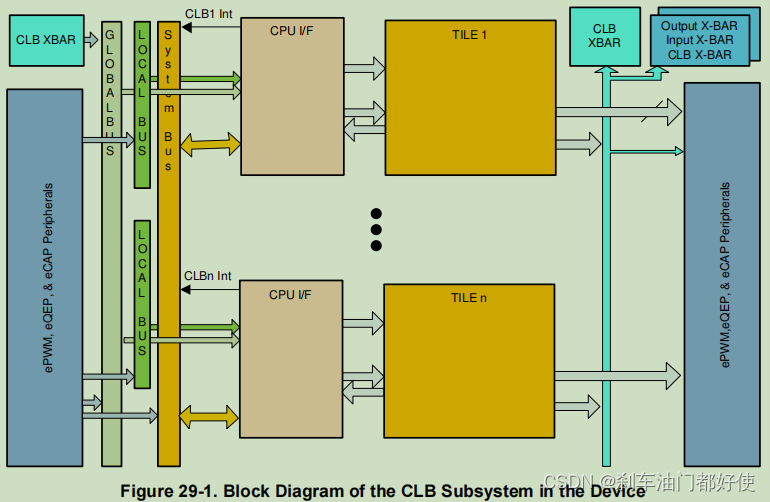

下图是CLB模块在系统中的交互,图中CLB XBAR和TILE是CLB。从049中有4个CLB,也就是TILE1-4。

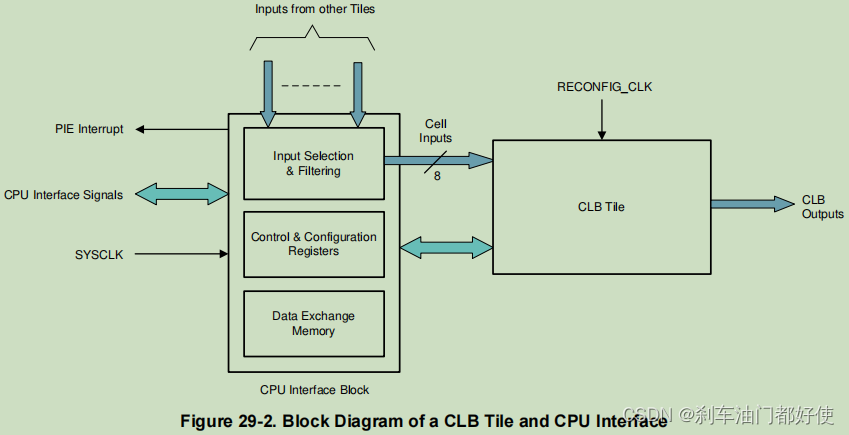

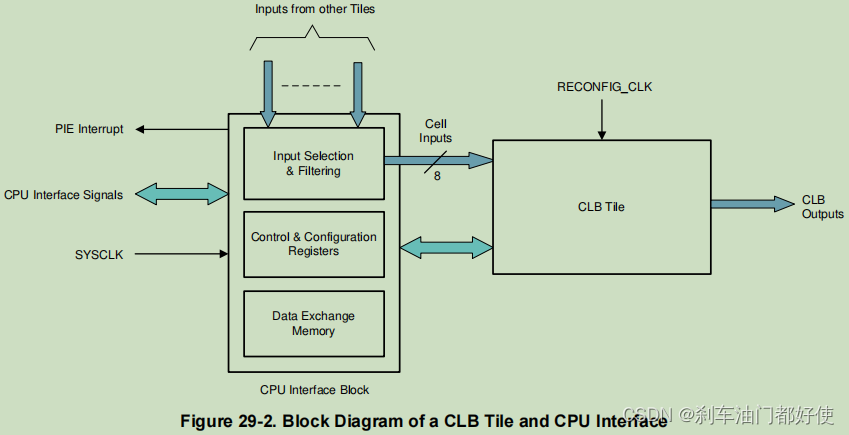

下图是CPU和CLB交互的示意图。

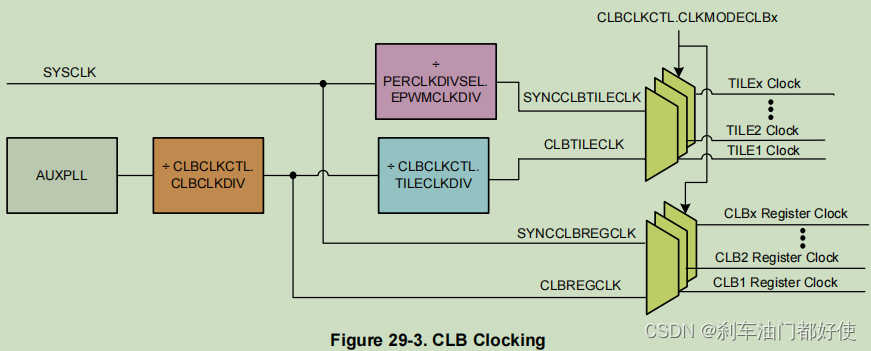

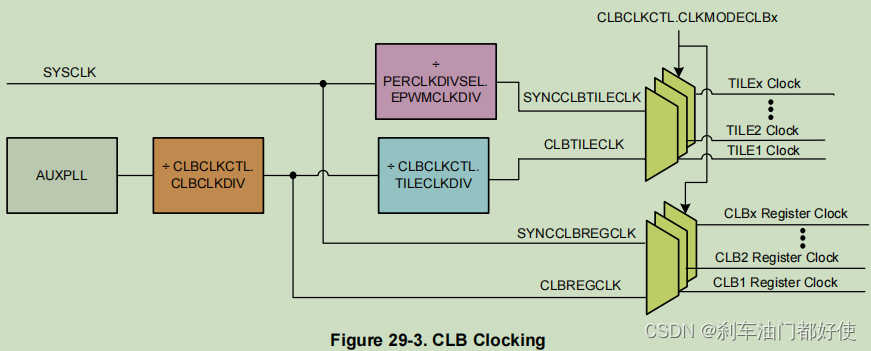

下图是CLB的时钟。

参考文档:

TMS320F28004x Real-Time Microcontrollers Technical Reference Manual (Rev. G)

CLB模块是可配置的逻辑块,和FPGA的CLB有些不同。

下图是CLB模块在系统中的交互,图中CLB XBAR和TILE是CLB。从049中有4个CLB,也就是TILE1-4。

下图是CPU和CLB交互的示意图。

下图是CLB的时钟。

TMS320F28004x Real-Time Microcontrollers Technical Reference Manual (Rev. G)

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.hqwc.cn/news/681697.html

如若内容造成侵权/违法违规/事实不符,请联系编程知识网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!