1,GTX是什么?

GT :Gigabit Transceiver千兆比特收发器;

GTX :Xilinx 7系列FPGA的高速串行收发器,硬核

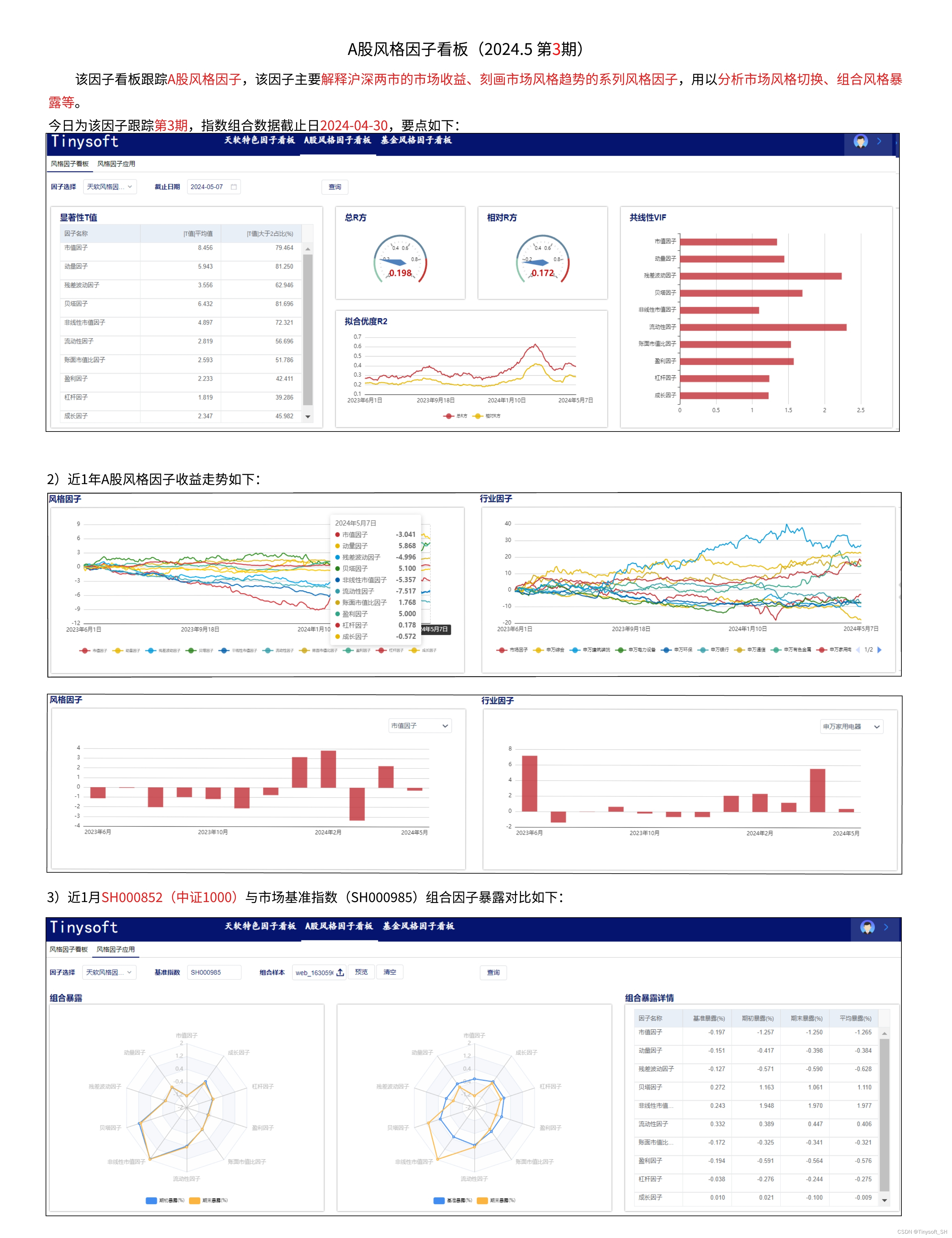

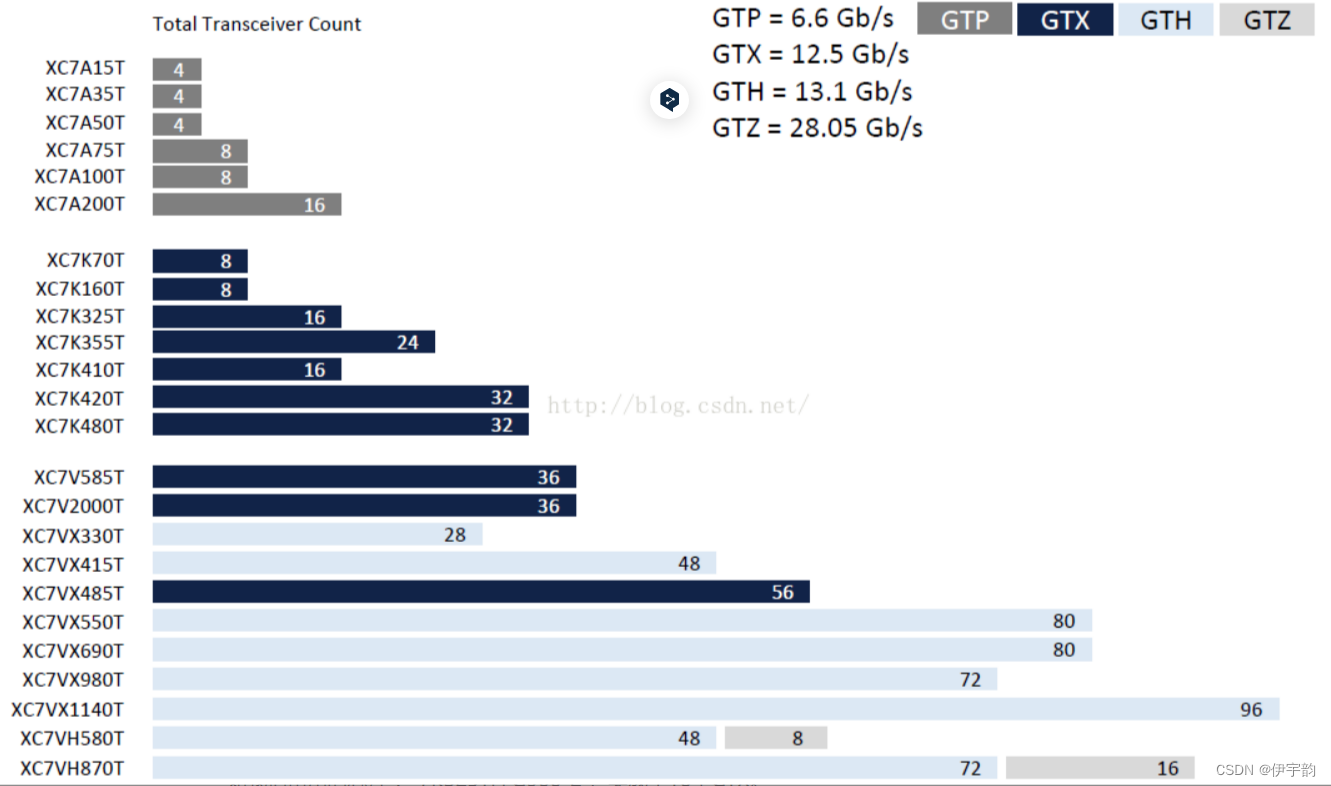

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH、GTZ四种串行高速收发器,可以支持多种协议如PCI Express,SATA,JESD204B等。

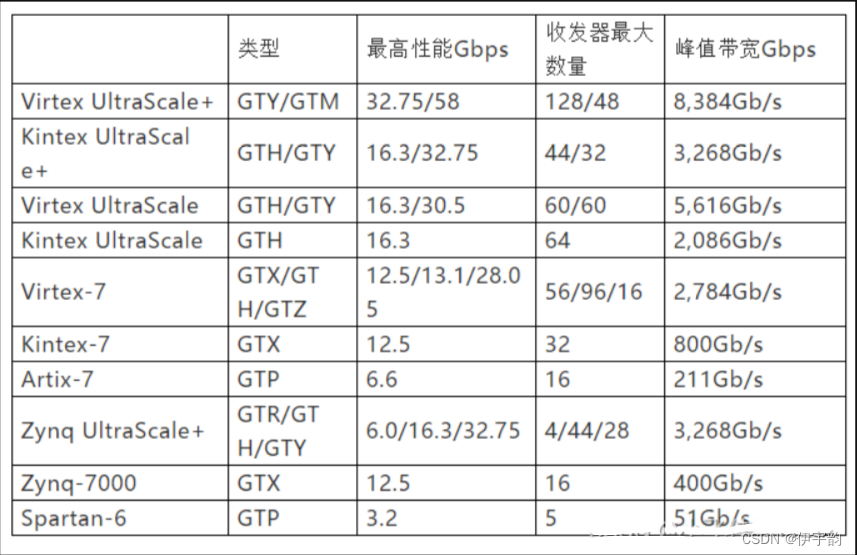

四种收发器主要区别是支持的线速率不同,下图可以说明在7系列里面器件类型和支持的收发器类型以及最大的收发器数量:

下图是各个系列的芯片所包含的GT资源,以及它们的相关性能参数。

首先需要明确的一点是,他们都是高速收发器,只是传输速率不同,速率大小为:

GTP < GPX < GTH < GTZ < GTY < GTM可以看到不同系列收发器个数和传输速度都不一样。

Artix-7 中的收发器类型为GTP;

Kintex-7 中的收发器类型为GTX;

Virtex-7 中的收发器类型为GTX/GTH/GTZ ;

UltraScale 中的GTH、GTY;

UltraScale+ 中的GTR、GTH、GTY;

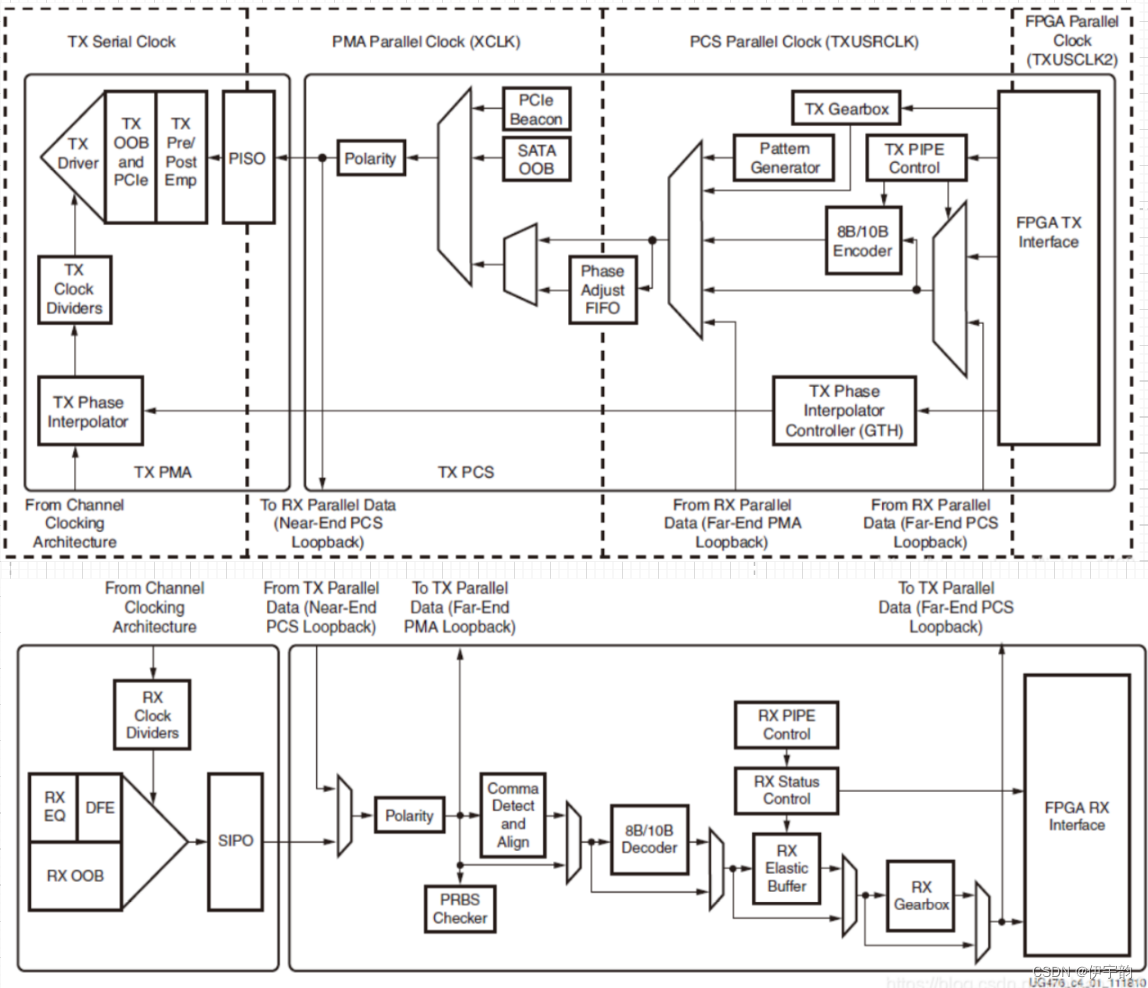

原理图

2,高速收发器的用途

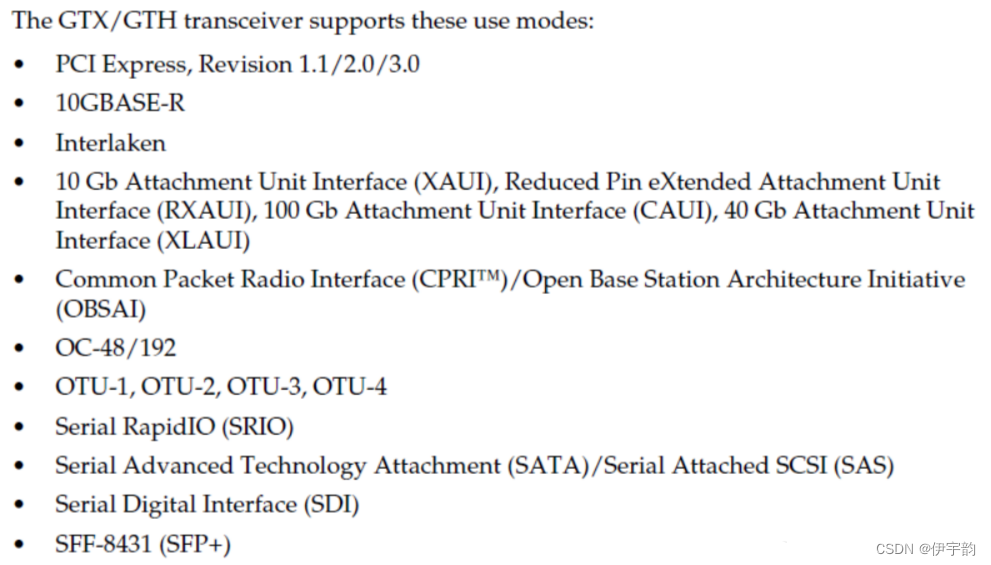

可以把它理解为一个高速串行并行转换器,其串行速率可达几十G。它可以将输入的并行数据转换为串行输出,或者将串行数据转换为并行数据。它既可以作为独立的发送装置或接收装置,也可以同时进行发送和接收。此外,用户可以根据需要自定义协议来实现通信,与其他IP核配合使用,以实现协议通信。例如,用于实现两块板子之间的通信,如Aurora协议,可以与Xilinx提供的Aurora IP核配合使用。GTX主要负责物理层数据的发送和接收,包括串行化和解串行化、编码和解码、时钟恢复等一系列物理层任务。此外,它还支持以下协议(见下图 该图是在数据手册截取的):

3,为什么需要高速收发器

主要是还是速率的问题,特别是在现在对于速率要求越来越高的情况下。在高速串行口之前,当数据速率开始超过1gb /s时,并行I/O方案就会达到物理限制,并且不再能够提供可靠、经济的方式来保持信号同步。

在早期的并行I/O总线中,接口对齐问题阻碍了与外部设备的有效通信。随着更高的速度在数字设计中变得普遍,管理信号延迟成为一个问题。

接口对齐问题是指在并行通信中,由于各个数据位可能在物理线路长度、信号传播速度等方面存在不同,因此它们可能无法在完全相同的时间到达目标设备,导致数据传输过程中发生错误。简单地说,就是各个数据线的信号需要在同一时刻到达目标,对齐就是把这个时刻统一。

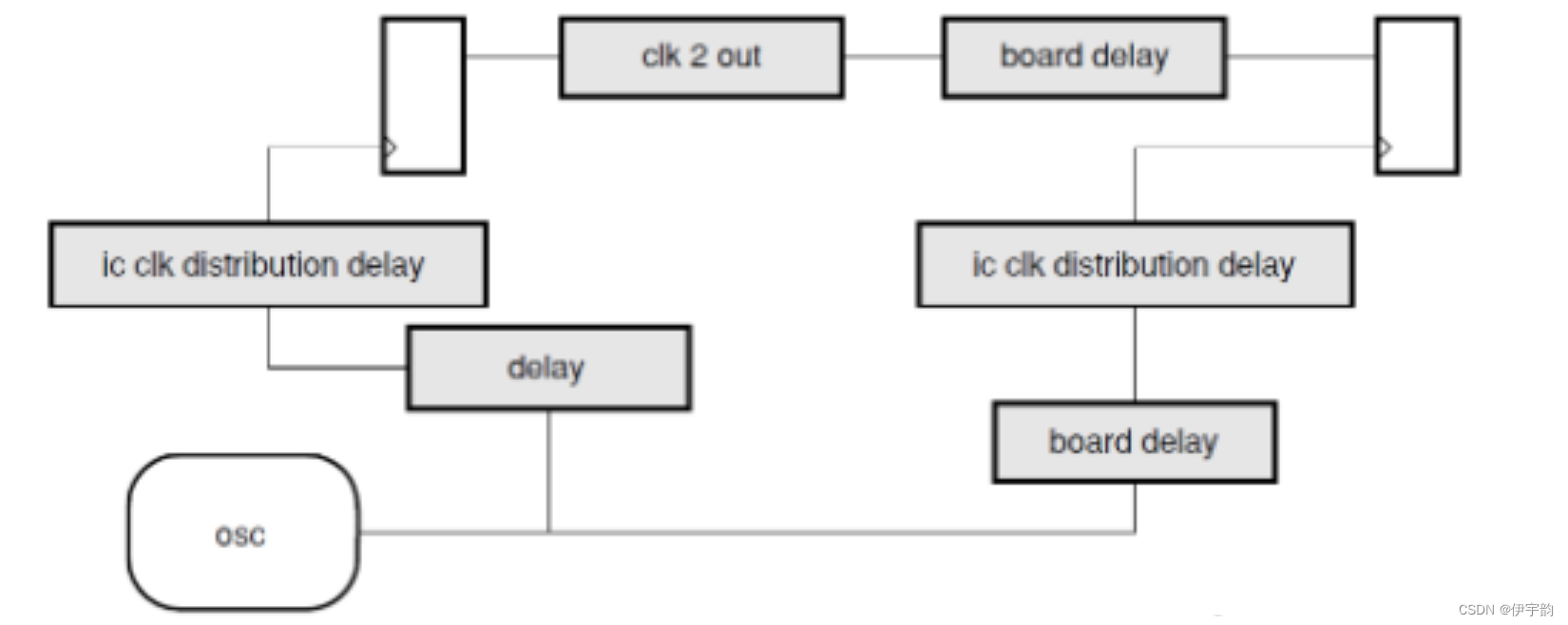

之前也有一些解决方案,比如利用系统时钟来同步:两个ic之间的通信,在两个ic上都应用一个公共时钟,用于数据传输和接收。

看起来好像很容易就解决了时间同步的问题,但实际上的系统是这样的

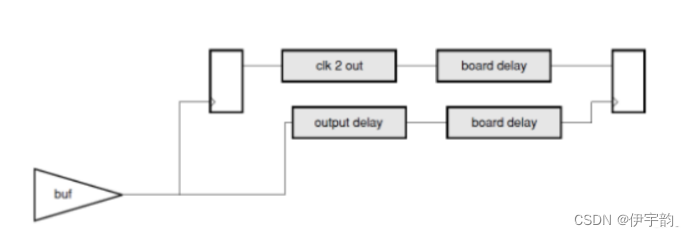

各种延误在速率低的情况下还可以忽略,因为延误相对于有效信号来说非常小。但随着速率的提高,延误的影响越来越大,甚至导致系统上的错误。随之而来的解决方法是,不依靠系统时钟,发送方在发生数据的时候,也发送一个同步的时钟

这样可以消除部分延迟,同时由于两根线是从同一个地方发出,传输距离等也很容易做的一致,所以有些延迟也可以抵消

不过,源同步设计导致时钟域数量的显著增加。这引入了时序约束和分析的复杂性,如现场可编程设备具有有限时钟缓冲的门阵列(FPGA),以及必须定制设计每个时钟树的专用集成电路(ASIC)。这个问题在大型并行总线上更加严重,因为电路板设计的限制常常迫使每个数据总线使用多个转发时钟。因此,32位总线可能需要4个,甚至8个转发时钟。

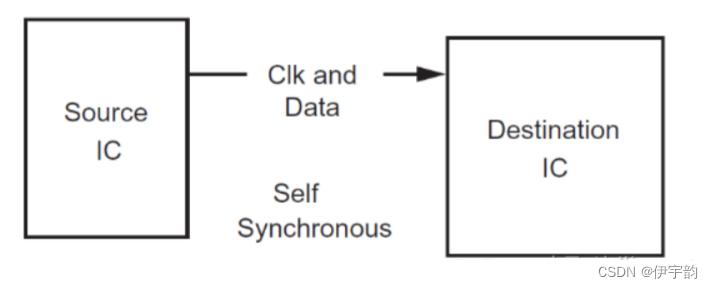

还有一种自同步的模式:

数据线带着时钟,相对自同步来说,它不需要那么多的时钟线了,随之而来的时钟复制也不需要。但比特率变动时需要额外的手段来纠正。如果数据包含相当多的连续零或连续一,那么可能出现失同步的情况。此外,在传输中,噪声或者干扰可能会导致误码。

这些问题,GTX的设计都给出了解决方案。

4,GTX IP核配置

基础知识

GT又称之为Gigabit Transceiver 千兆比特收发器,是嵌入在FPAG芯片里面 的一种硬核。

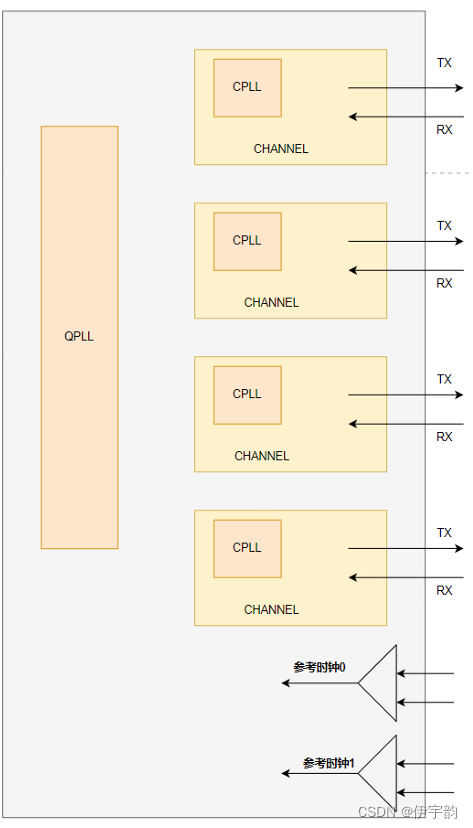

一条lane包含一对tx和rx;

一对tx、rx、加上cpll称之为一条通道channel;

一个bank有4对tx和rx、两对差分时钟,也被称之为quad。

①参考时钟不仅可以驱动当前 bank 的上面的通道,还可以驱动相临近的 bank。 上面的bank的被称之为北North,下面的bank被称之为南South。

②一对外部参考时钟,最多驱动三组相邻的 bank,( quad 不超过不超过三 个),驱动的通道不超过12个。

IP核配置

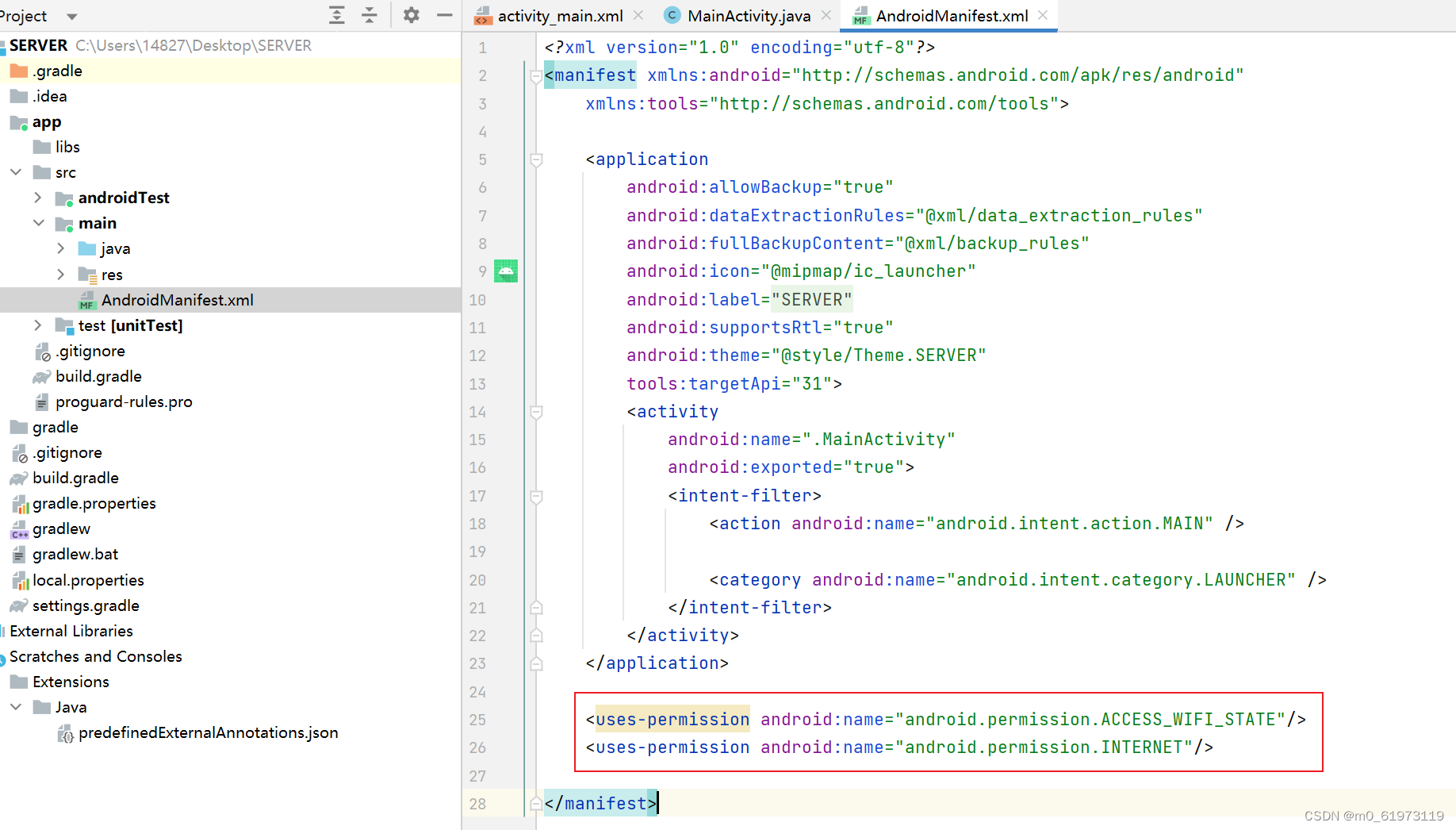

(1)创建工程

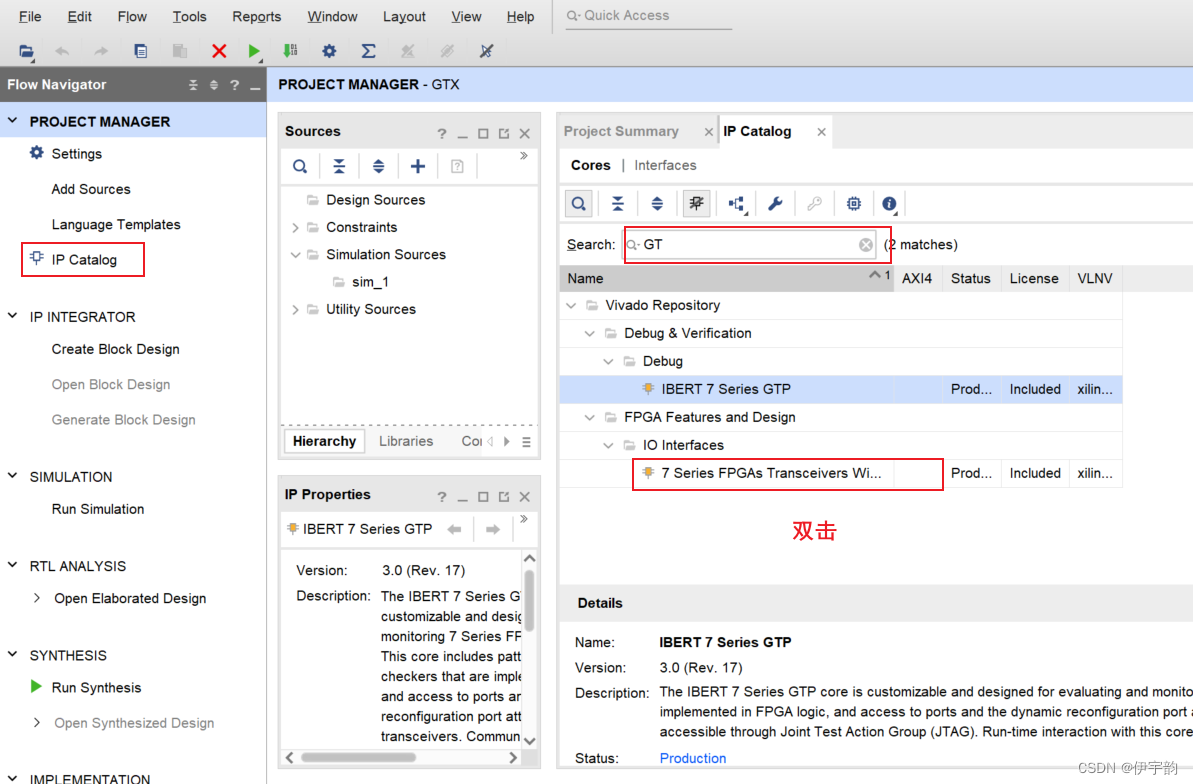

IP Catalog中搜索GT

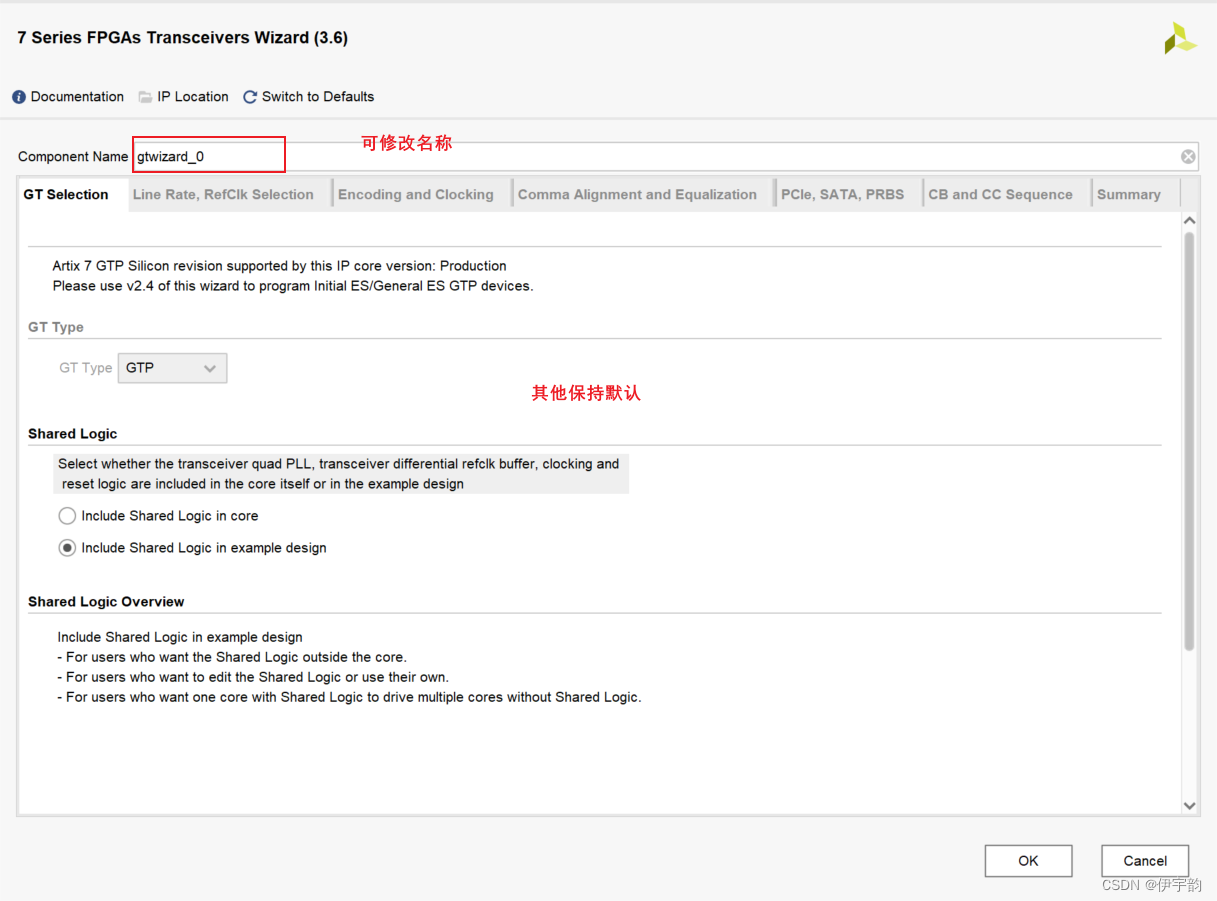

(2)第一页配置

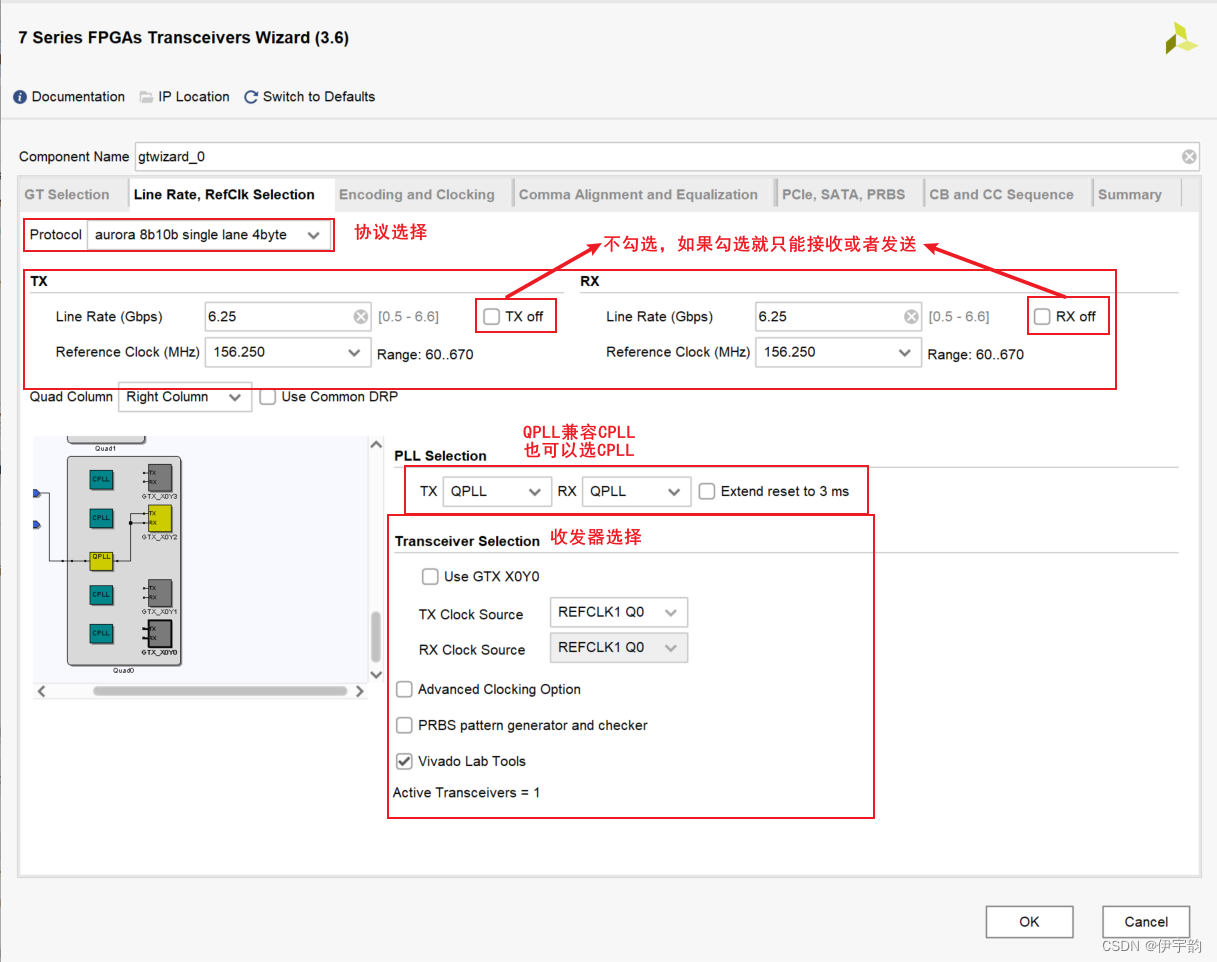

(3)第二页配置

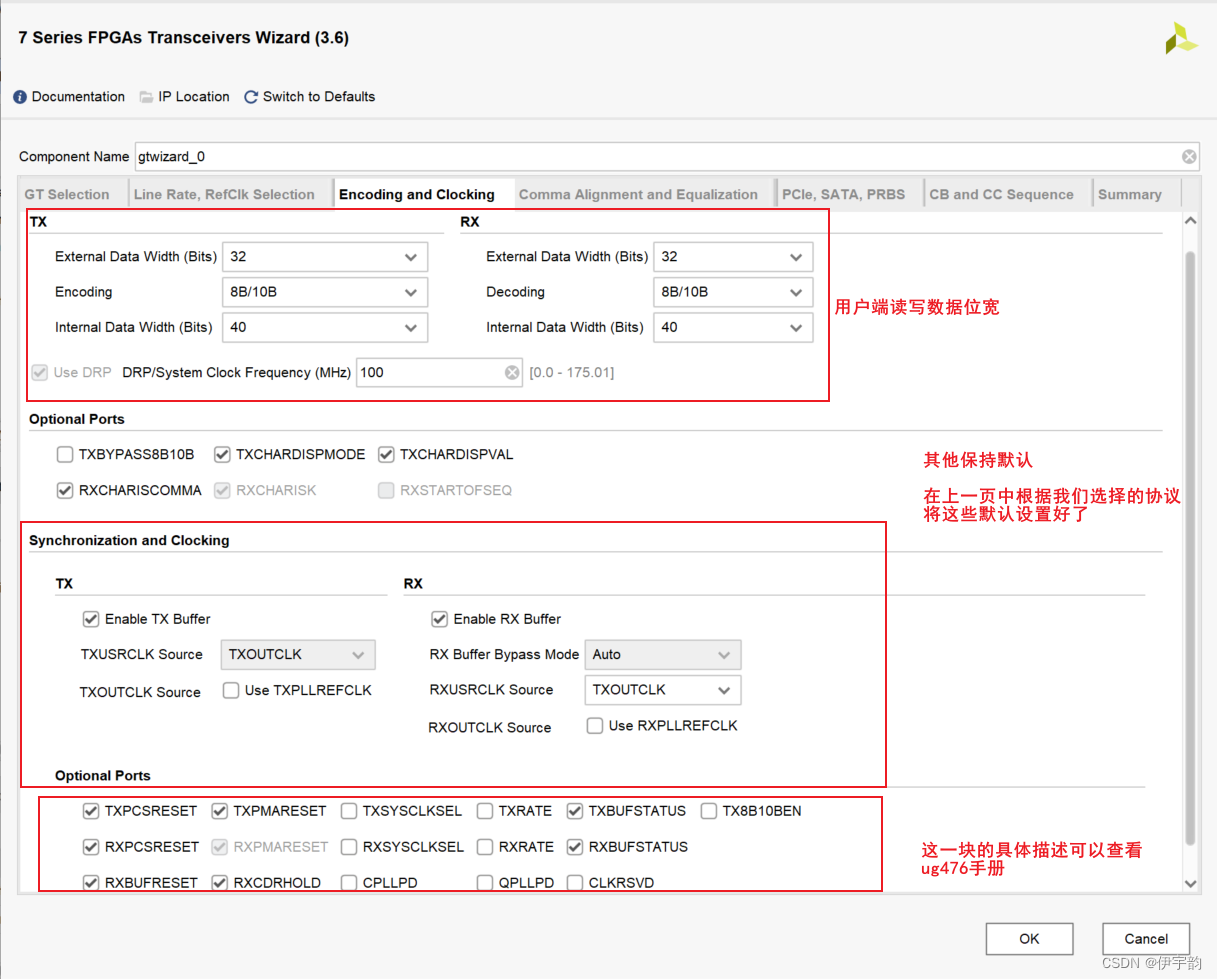

(4)第三页配置

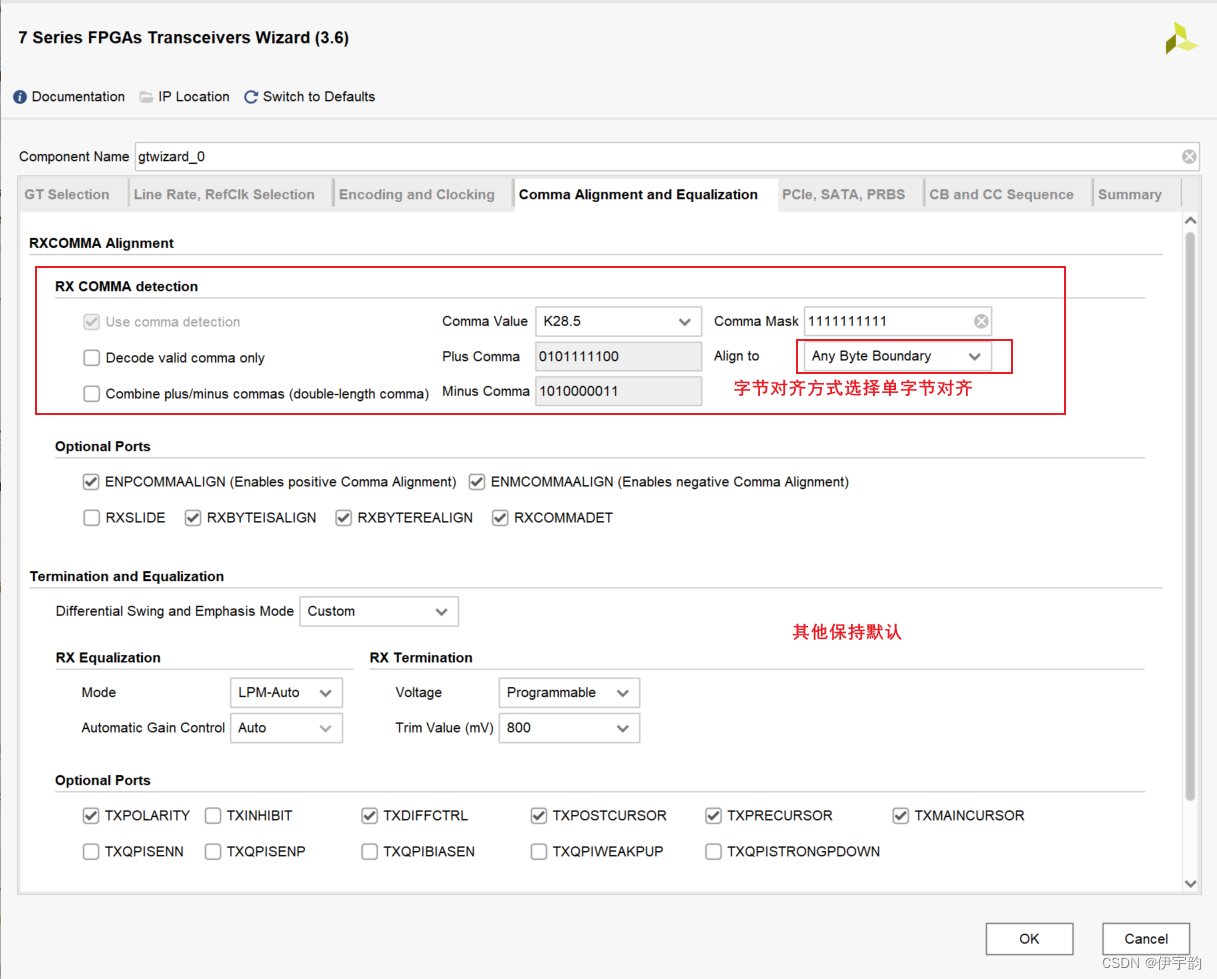

(5)第四页配置

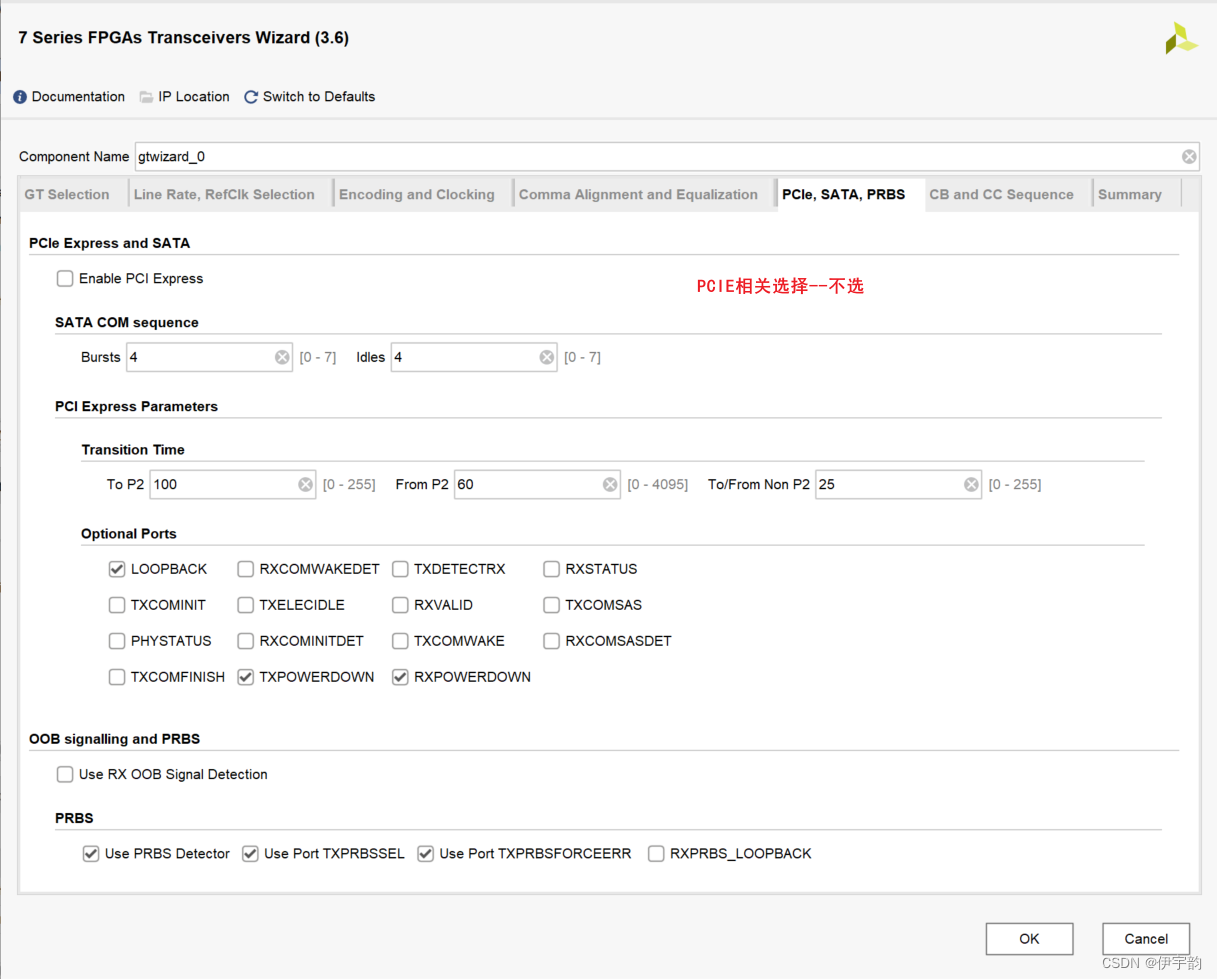

(6)第五页配置

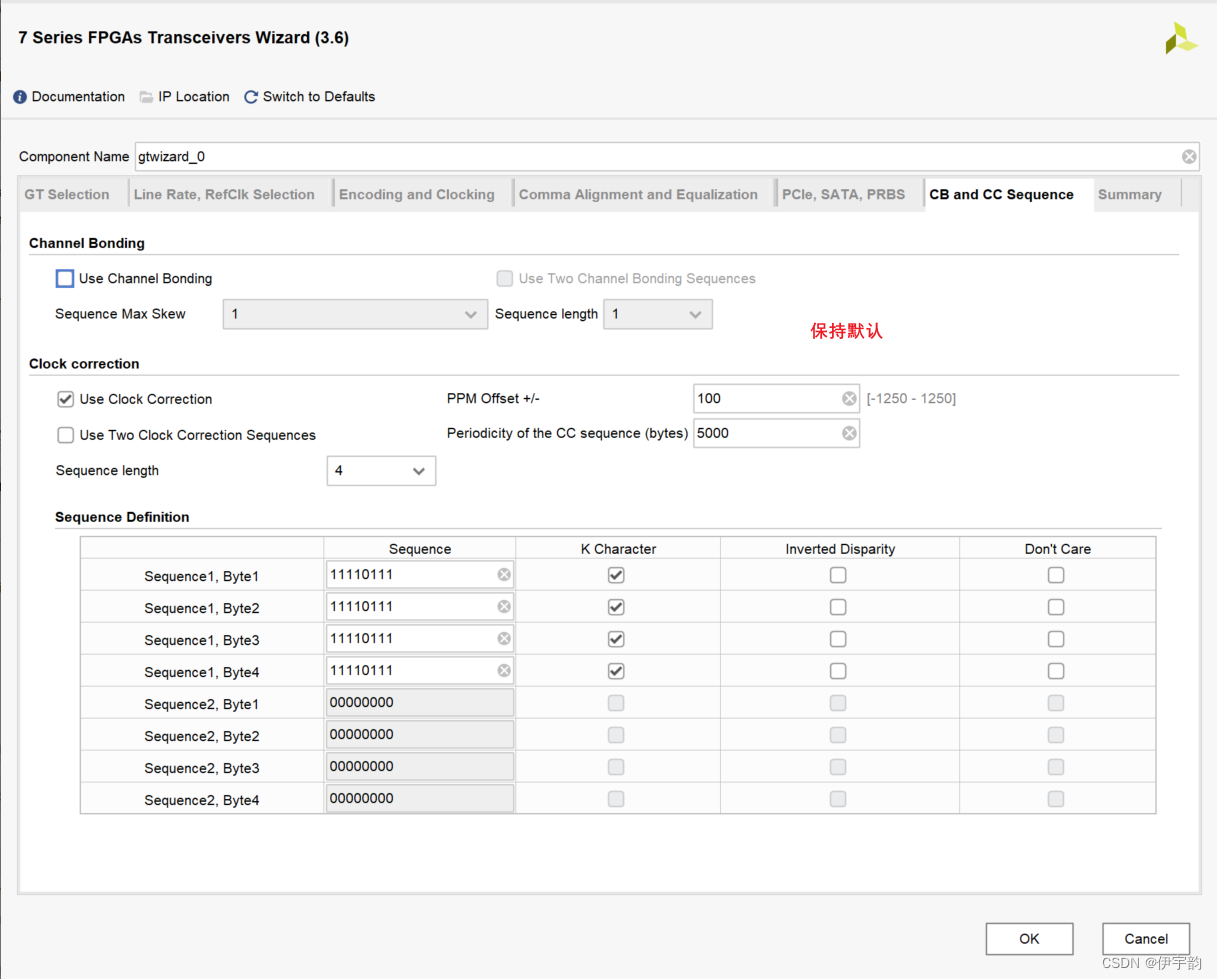

(7)第六页配置

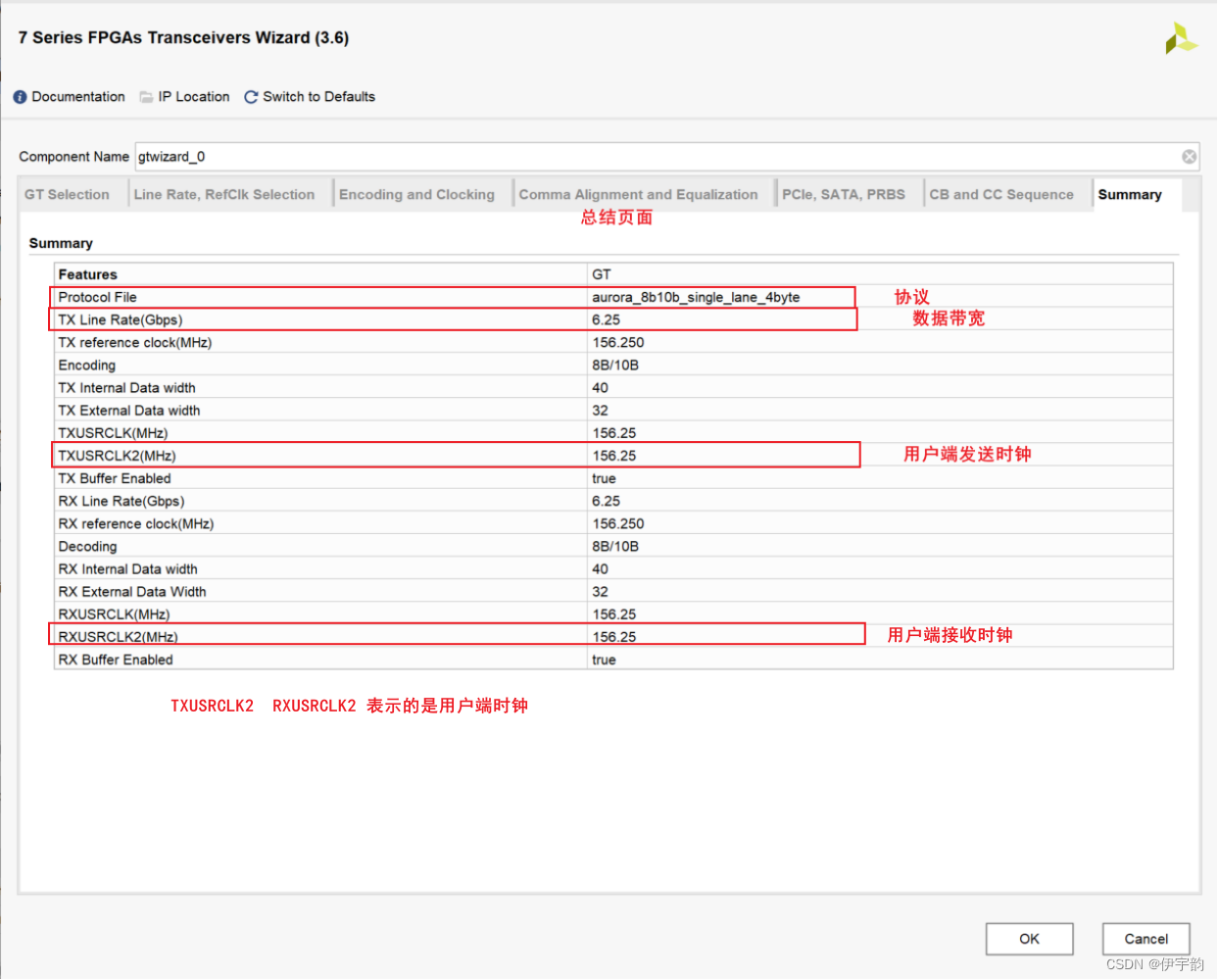

(8)第七页 总结界面

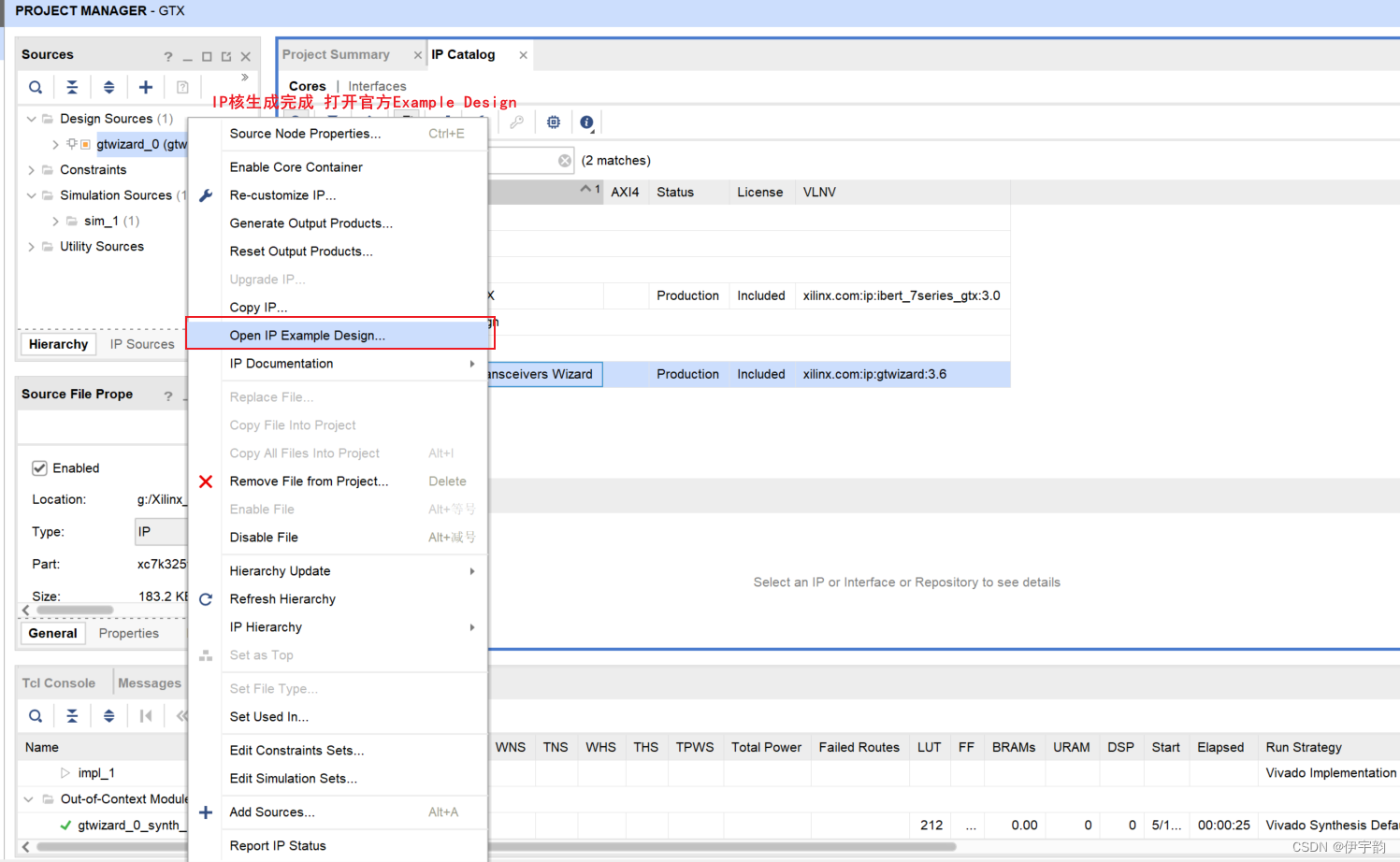

(9)IP核生成完成

打开官方Example Design

代码框架

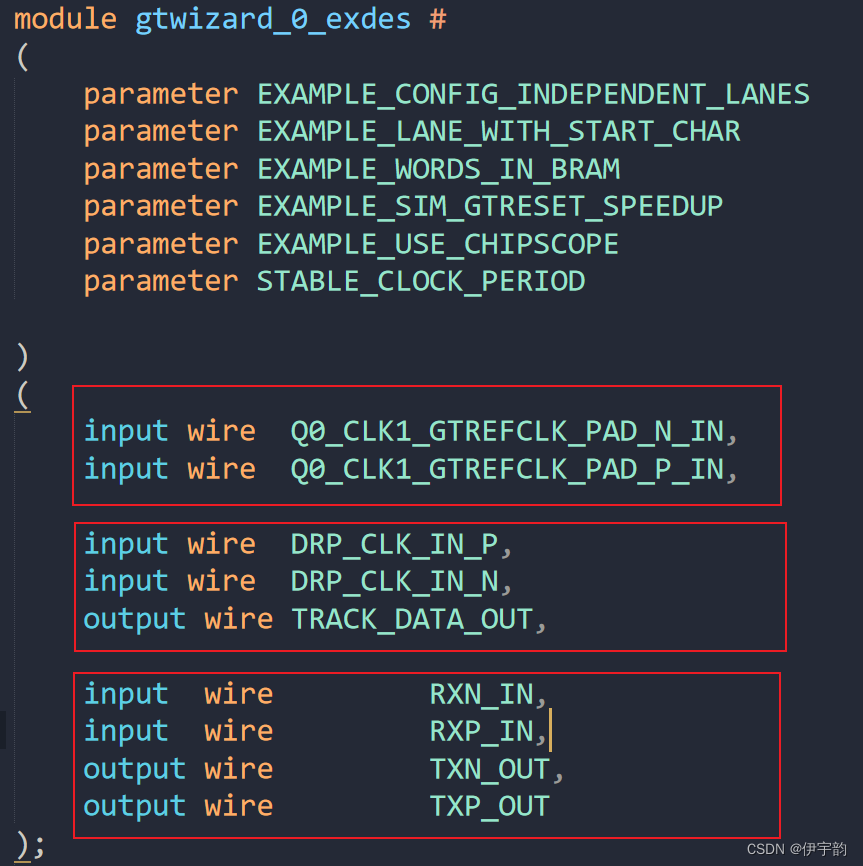

(1)gtwizard_0_exdes.v为整体工程的TOP文件

输入输出端口分别为:

Q0_CLK1_GTREFCLK_PAD_N/P_IN:外部差分输入参考时钟

DRP_CLK_IN_P/N:系统时钟

TXP/N_OUT:发送1bit差分输出

RXP/N_IN:接收1bit差分输入

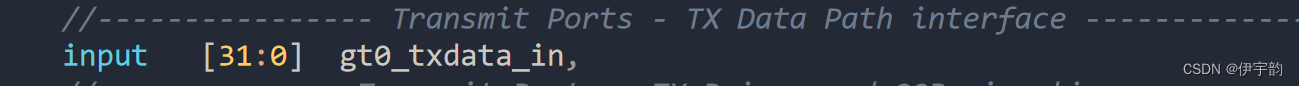

(2)gtwizard_0_support.v

该文件主要例化了GT高速收发器的IP核,并对时钟进行了配置

例如FPGA与GT的接口:32bit的待发送数据gt0_txdata_in:

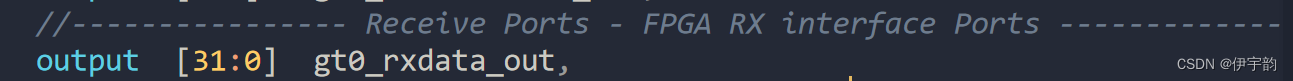

32bit的接收数据gt0_rxdata_out

(3) gtwizard_0_GT_FRAME_GEN.v

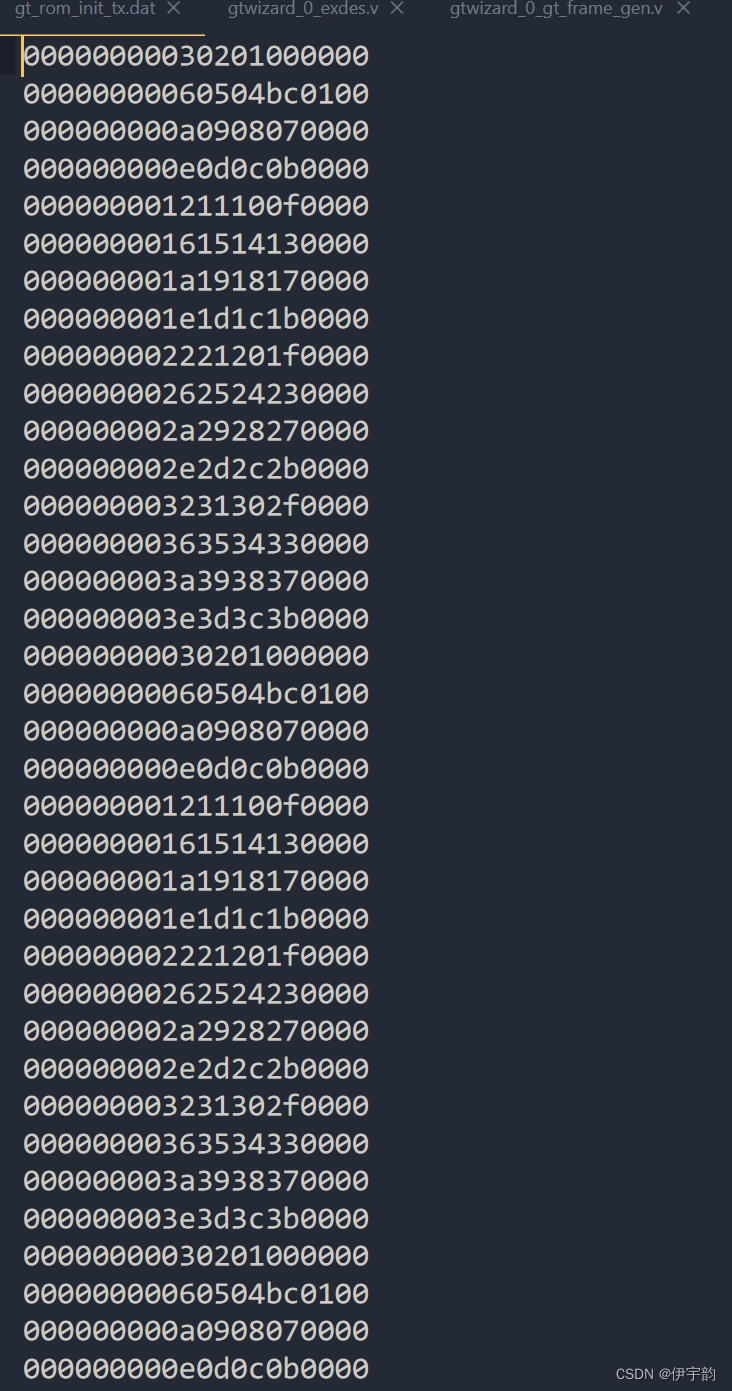

该文件用于产生发送数据的来源,本质上是从ROM中读取数据。

(4)gtwizard_0_GT_FRAME_CHECK.v

该文件用于接收到数据后,与文件中的数据源进行比对,并且记录下错误的数据个数。

(5)gtwizard_0_TB.v

GTX收发的测试文件,在此之前,应该先了解一下LOOPBACK。

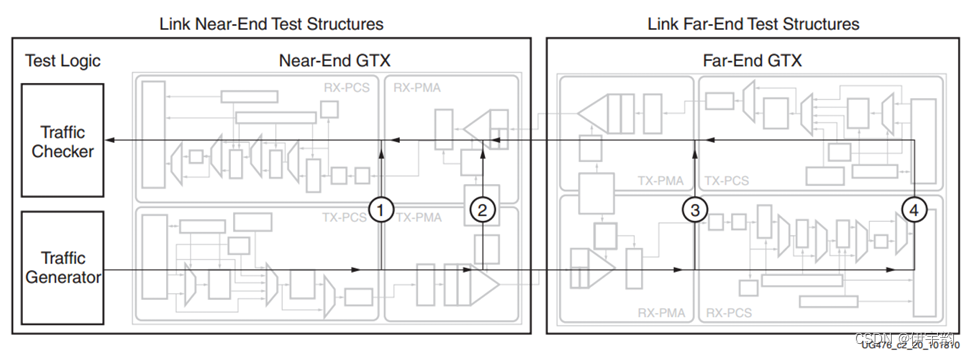

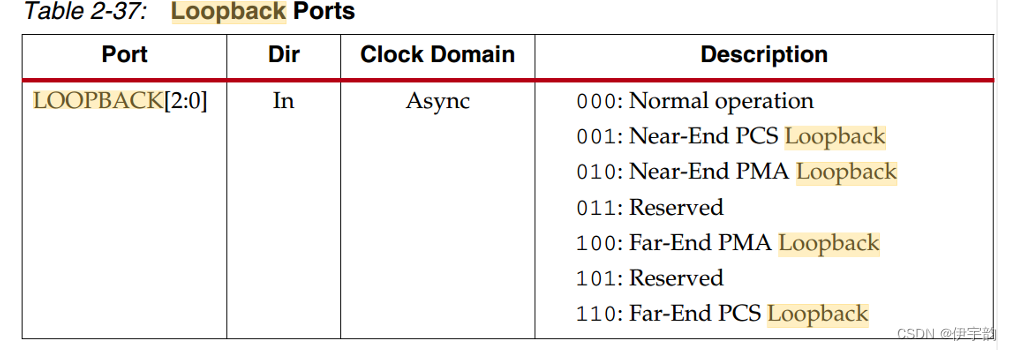

从手册中得知收发器有专门的回环模式进行测试,即进行自发自收,如下图所示有四个通道。

测试的时候选择哪种呢?

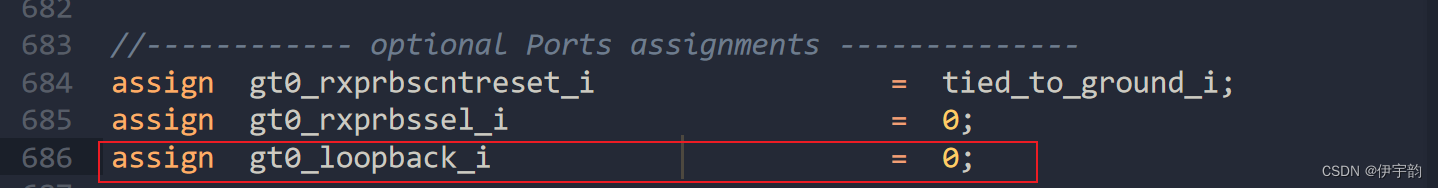

查看top文件,即gtwizard_0_exdes.v文件,LOOPBACL设置的是0,即Normal 模式,并没有进行回环测试,如下图

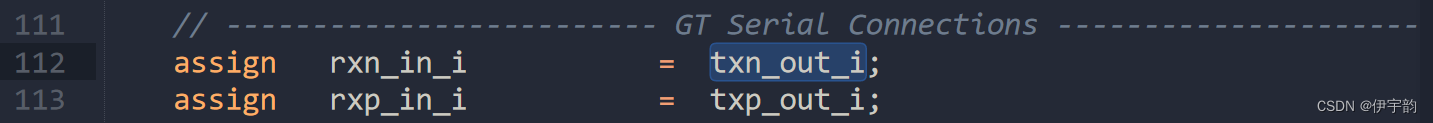

观察TB文件,这里是直接在仿真中把发送端和接收端用线连在一起实现回环测试

仿真波形

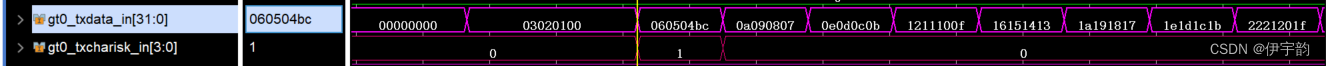

由于此仿真是自收发,因此我们需要关注的信号只有四个,gtwizard_0_support.v中的:

/gtwizard_0_TB/gtwizard_0_exdes_i/gtwizard_0_support_i/gt0_txdata_in

/gtwizard_0_TB/gtwizard_0_exdes_i/gtwizard_0_support_i/gt0_txcharisk_in

/gtwizard_0_TB/gtwizard_0_exdes_i/gtwizard_0_support_i/gt0_rxdata_out

/gtwizard_0_TB/gtwizard_0_exdes_i/gtwizard_0_support_i/gt0_rxcharisk_out

发送端

gt0_txcharisk_in为1时发送数据060504bc,然后gt0_txcharisk_in为0后数据gt0_txdata_in依次为0a090807,0e0d0c0b……

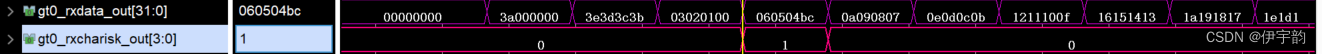

接收端

gt0_txcharisk_in为1时发送数据060504bc,然后gt0_txcharisk_in为0后数据gt0_rxdata_out依次为0a090807,0e0d0c0b……

接受数据和发送端一致,测试正确!

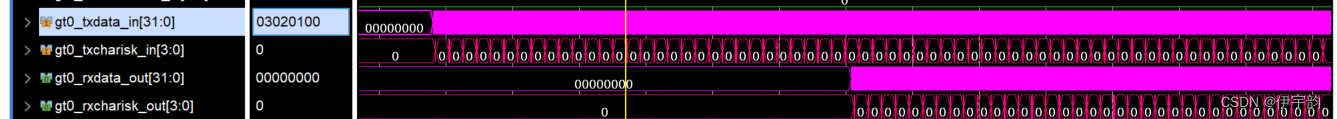

总结:

GT高速收发器的IP Example已经具有相当完备的功能,但是GT IP 核端口信号非常多,乱七八糟的信号也多,可以使用官方的文件封装 一个非常简洁明了、看着非常舒服的用户端信号出来:

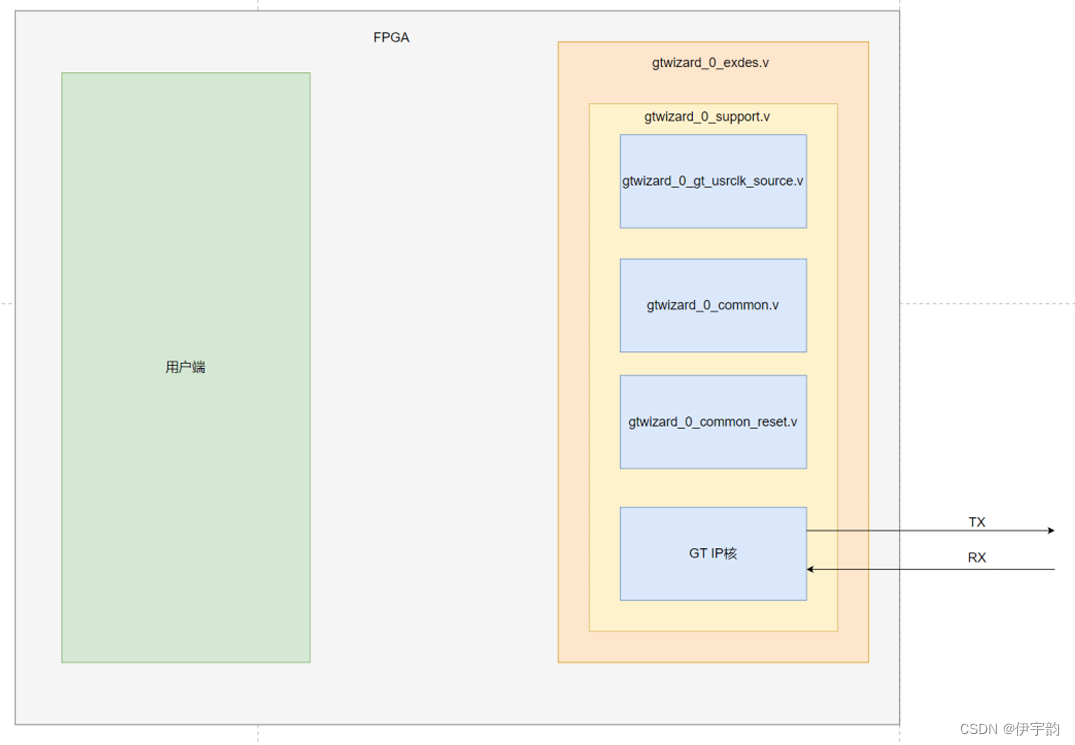

如下图:

修改gtwizard_0_exdes.v文件,加入用户端接受和发送相关信号就实现上述框架!

参考:https://blog.csdn.net/weixin_44253012/article/details/136401477