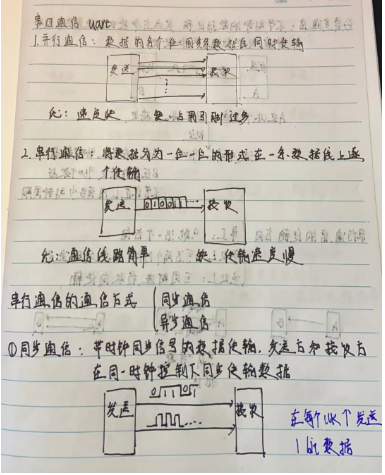

一、uart简介

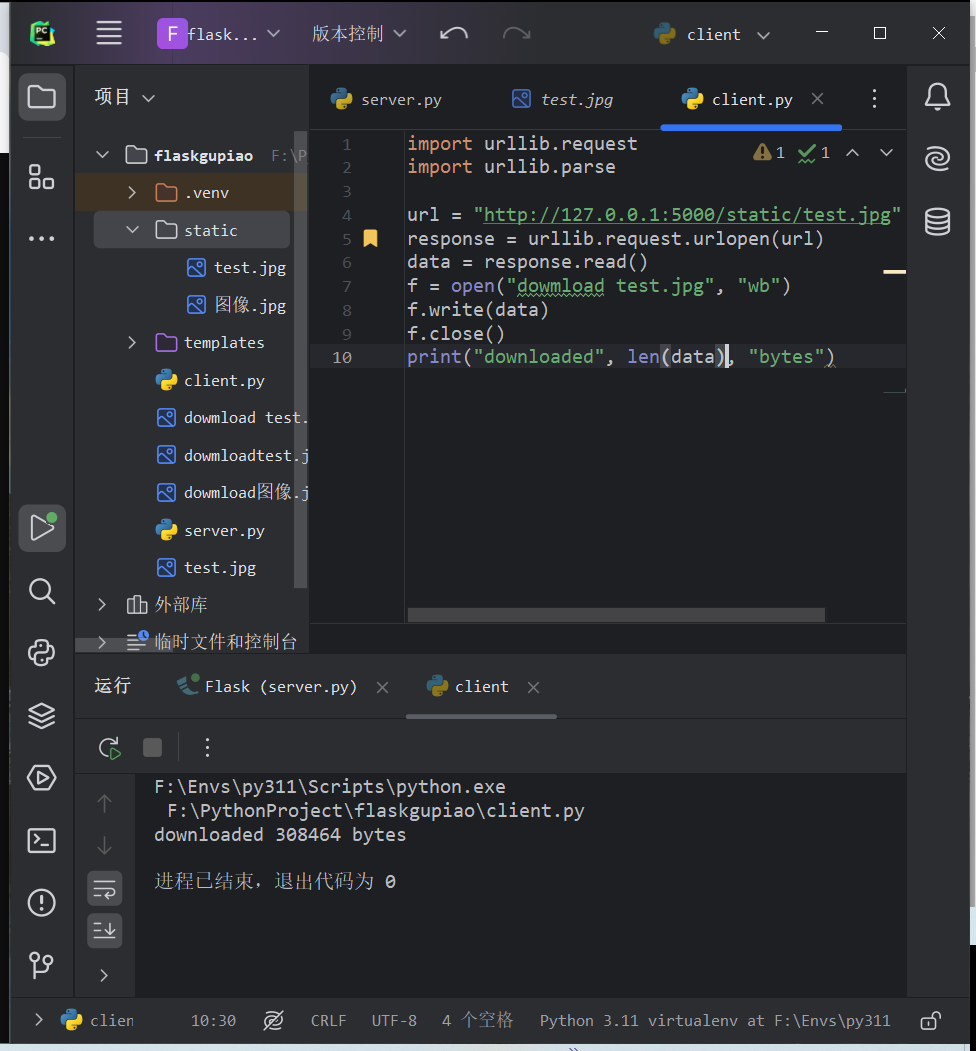

二、uart串口通信实验

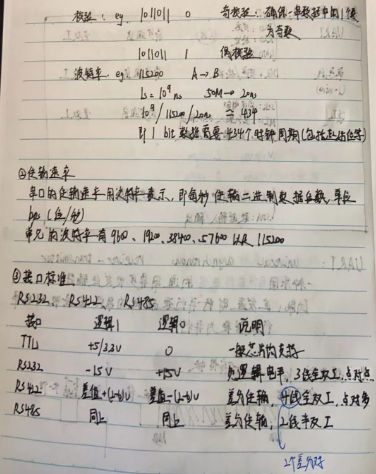

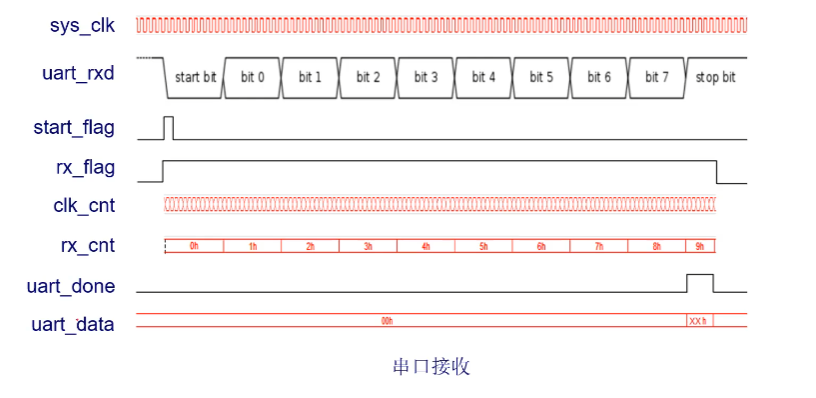

其中:

sys_clk为系统时钟。uart_rxd为串口从上位机接收到的数据,

当检测到uart_rxd出现下降沿(起始位),start_flag产生正向脉冲,rx_flag也被拉高,

clk_cnt为时钟计数器,由0计数到433,rx_cnt为接收数据计数器,当计数到第九位且时钟计数达到波特率的一半时,将rx_flag置低。

在实验中,我们将传入的8bit数据存入一个临时寄存器rx_data(图中未体现),当计数到第九个时,uart_done信号产生正向脉冲,表示一次串口通信结束,此时将临时寄存器rx_data赋值给数据输出uaret_data。

注:为了防止亚稳态的影响,我们将打两拍后的uart_rxd赋值给临时寄存器中

![FPGA笔记[2]-拨码开关控制LED灯](https://img2024.cnblogs.com/blog/1048201/202405/1048201-20240519021504542-983918953.png)