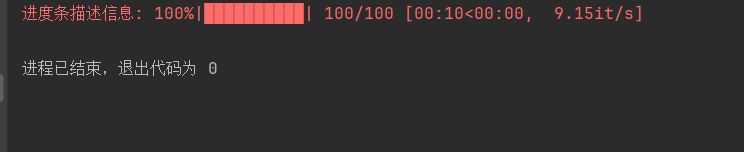

一、环境约束

此外,还有电路内互连线的延时也没有考虑在内

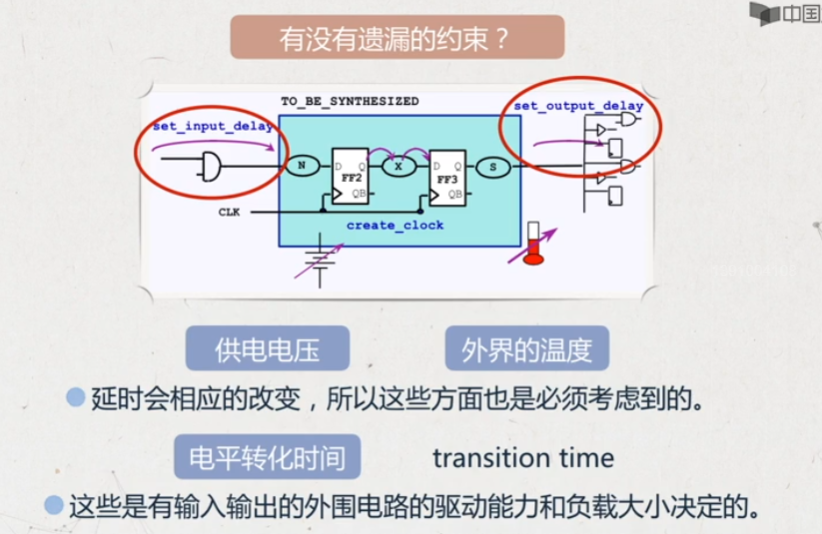

四个环境约束:

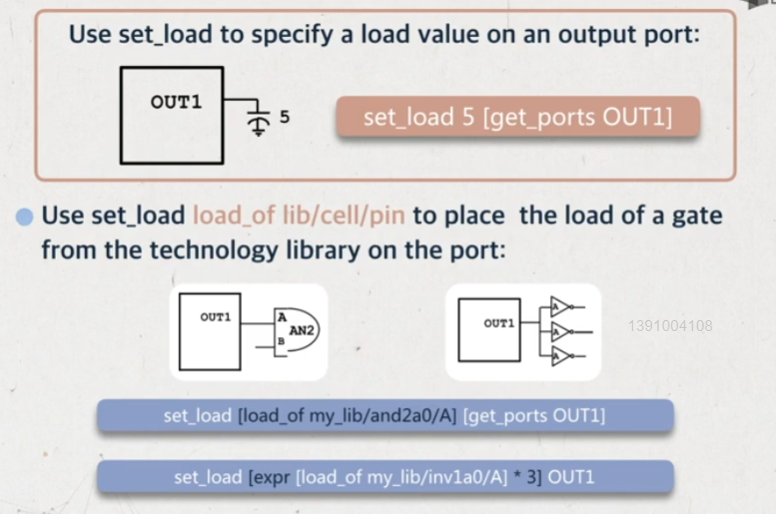

1.输出负载

如果电路的输出负载过大,将会加大电路的transition time,从而影响电路时序

此外,若dc默认输出负载为0,即相当于不接负载,这样综合出来的电路时序显然过于乐观,不能反映实际工作情况

可以设置一个精确的值,也可以使用现有工艺库单元的load值来代替

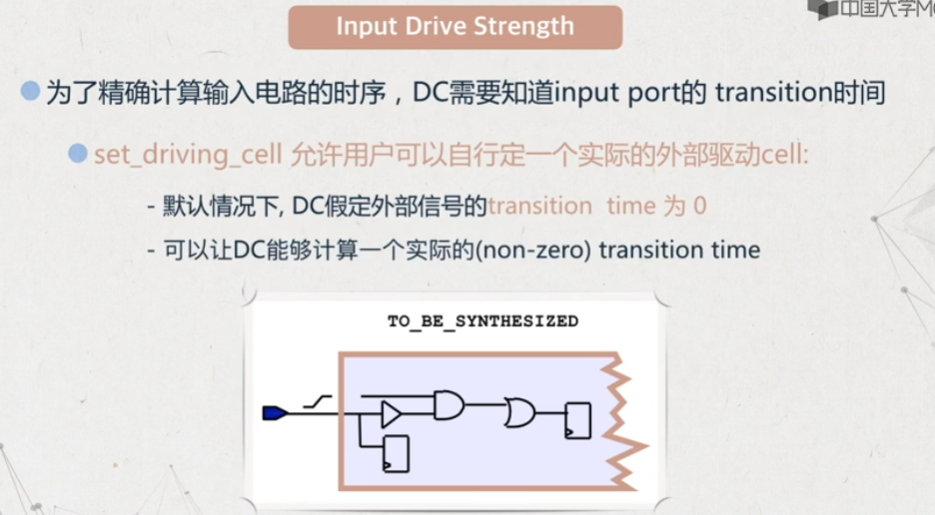

2.输入驱动强度

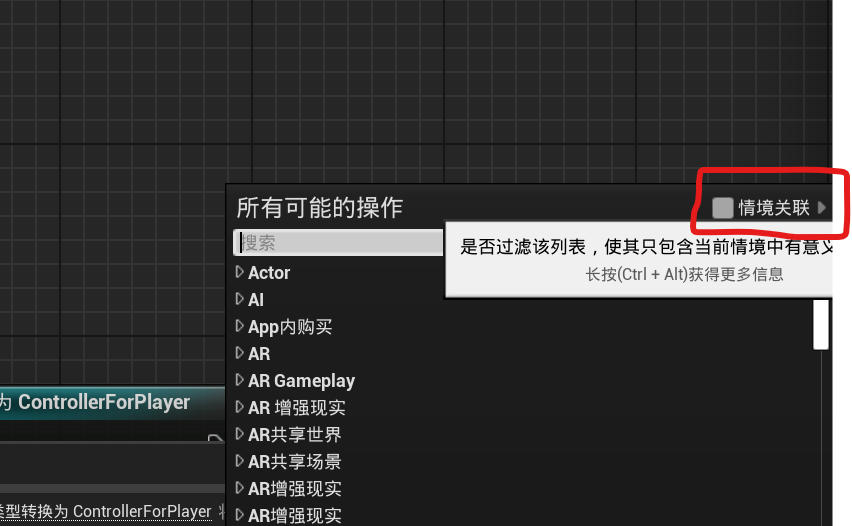

如上图所示,给端口IN1设置了一个逻辑门的driving_cell

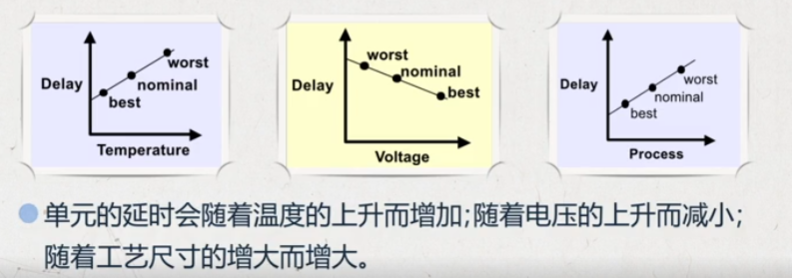

3.环境条件

在晶圆厂提供的工艺库中,各个单元的延迟都是在标准条件下得到的,一旦电路环境发生改变,必然影响到电路的时序特性

温度、电压、工艺对电路时序的影响如下:

因此。工艺库提供了几种工作模型以供设计者选择

/*********************************************************************/

/*********************************************************************/

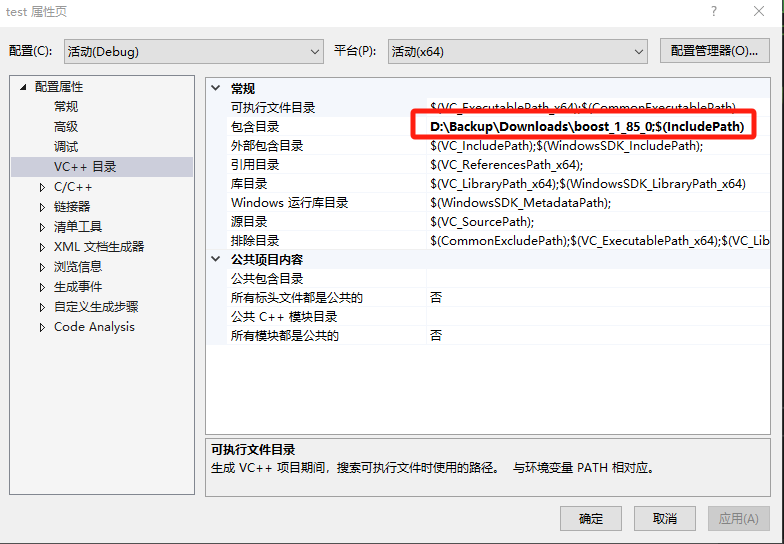

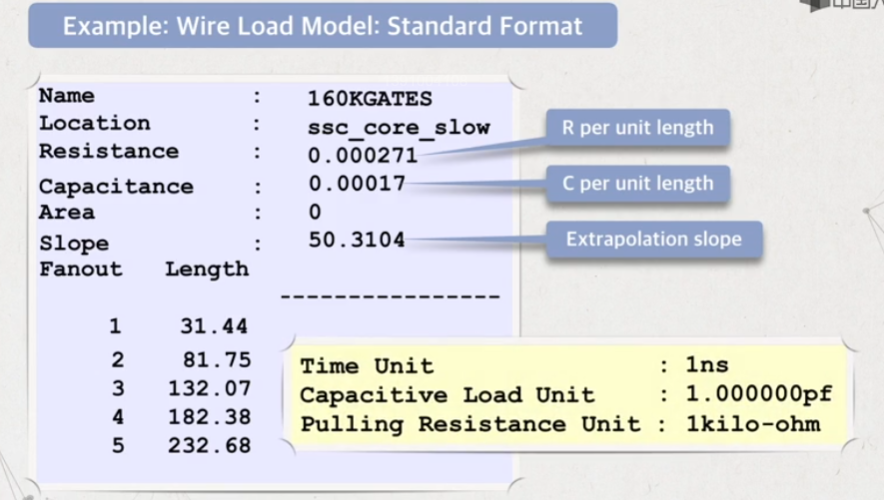

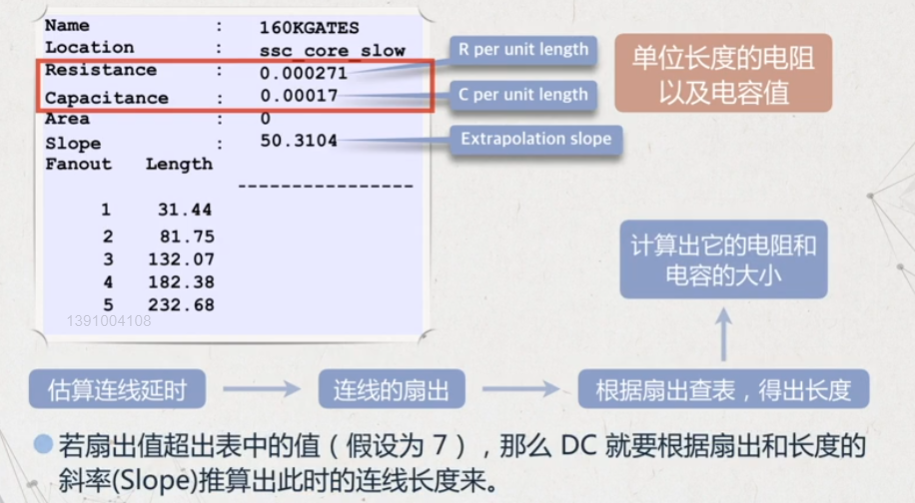

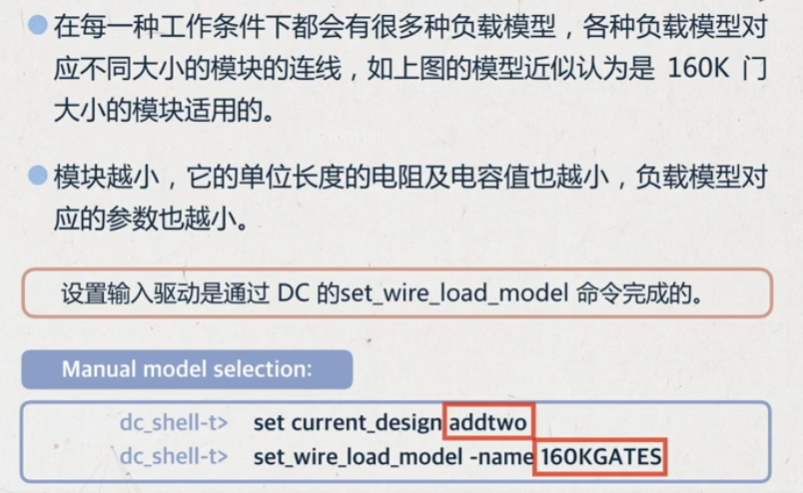

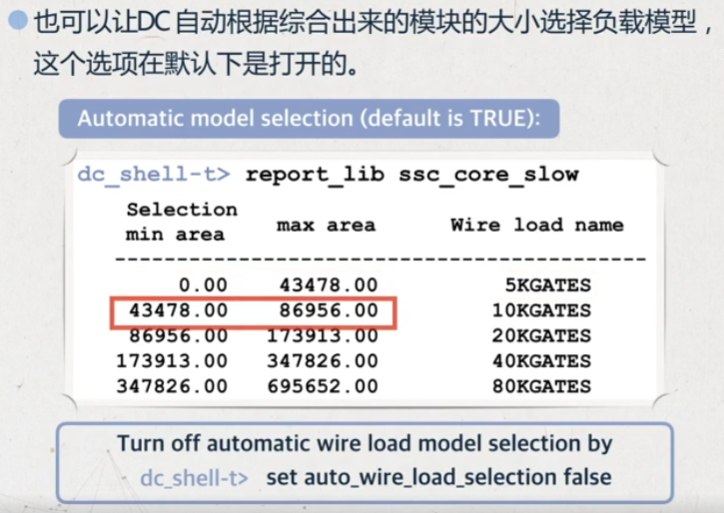

4.连线负载模型

下图给出了工艺库中连线延迟的模型

/*********************************************************************/

/*********************************************************************/

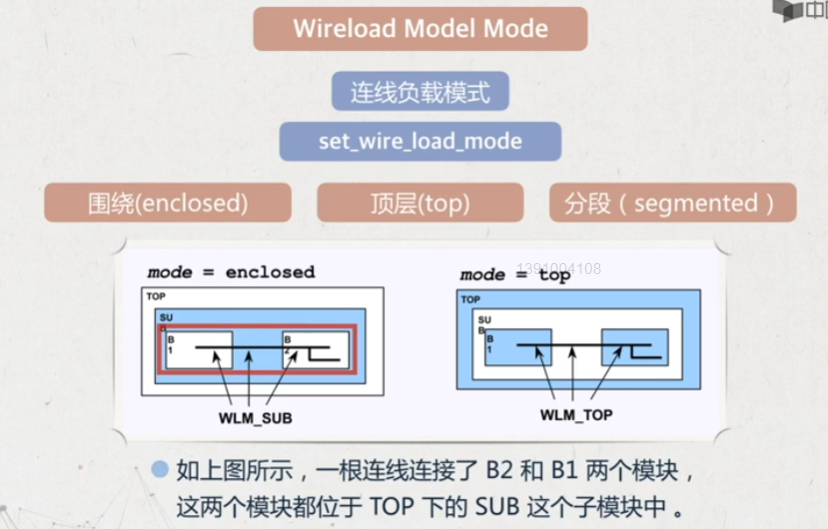

如果连线连接的是不同的模块,那么该如何估计?

围绕:连接B1和B2的连线的负载模型用围绕它们的模块的负载模型代替,即用SUB的负载模型;

顶层:使用顶层模块的负载模型代替;

分段:分别根据穿过的三段模型相加得到

设置方式

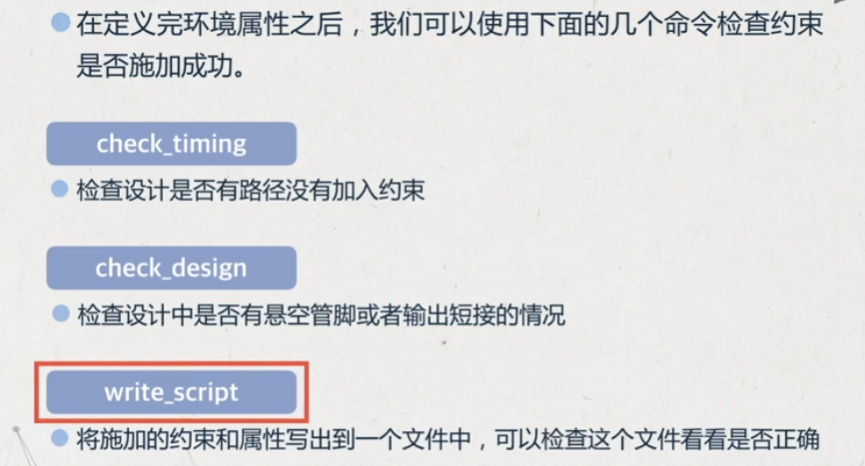

二、约束后检查

![[GIT] 解决:git status时有Untracked files(未跟踪的文件)](https://blog-static.cnblogs.com/files/johnnyzen/cnblogs-qq-group-qrcode.gif?t=1679679148)