D-PHY

1、传输模式

1.LP(Low-Power) 模式:用于传输控制信号,最高速率 10 MHz

HS(High-Speed)模式:用于高速传输数据,速率范围 [80 Mbps, 1Gbps] per Lane 传输的最小单元为 1 个字节,采用小端(低位字节放到内存的低地址端,高位字节放到内存的高地址端)的方式及 LSB first,MSB last(一个芯片的管脚中,对于一个多比特的信号,比如32根的地址线,从低开始按0到31编个号。MSB就是31,LSB就是0。那么如果标记为:ADDR[31:0]就是MSB first的方式,如果标记为ADDR[0:31]就是LSB first的方式)

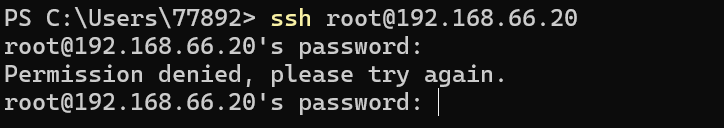

2、Lane States

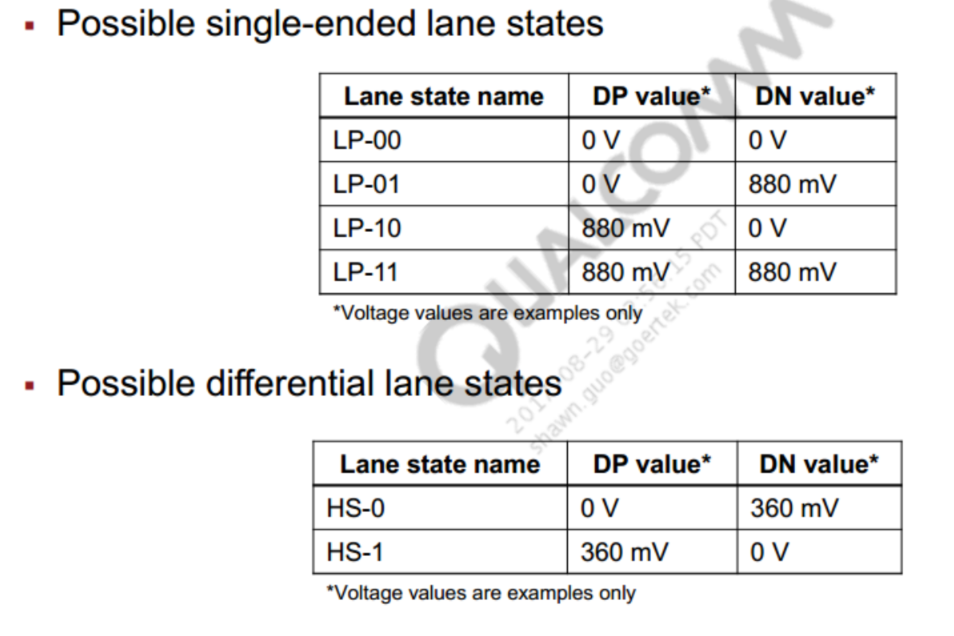

LP mode 有 4 种状态: LP00、LP01(0)、LP10(1)、LP11 (Dp、Dn)

HS mode 有 2 种状态: HS-0、HS-1

各状态对应的Dp,Dn定义如下:

3、Lane Levels

LP: 0 ~ 1.2V

HS: 100 ~ 300mV,HS common level = 200mV,swing = 200 mv

高通平台,高通文档把各个状态对应的high,low具体到了电压值:

其中Single-ended land states即LP模式,differential lane states即HS模式

4、操作模式

在数据线上有 3 种可能的操作模式:Escape mode, High-Speed (Burst) mode and Control mode,下面是从停止状态进入相应模式需要的时序:

Escape mode、

-

Escape mode 需要发送 8-bit entry command 表明请求的动作,比如要进行低速数据传输则需要发送 cmd: 0x87,进入超低功耗模式则发送 cmd: 0x78。在 DSI 中 LP 通讯只用 Data Lane 0。

-

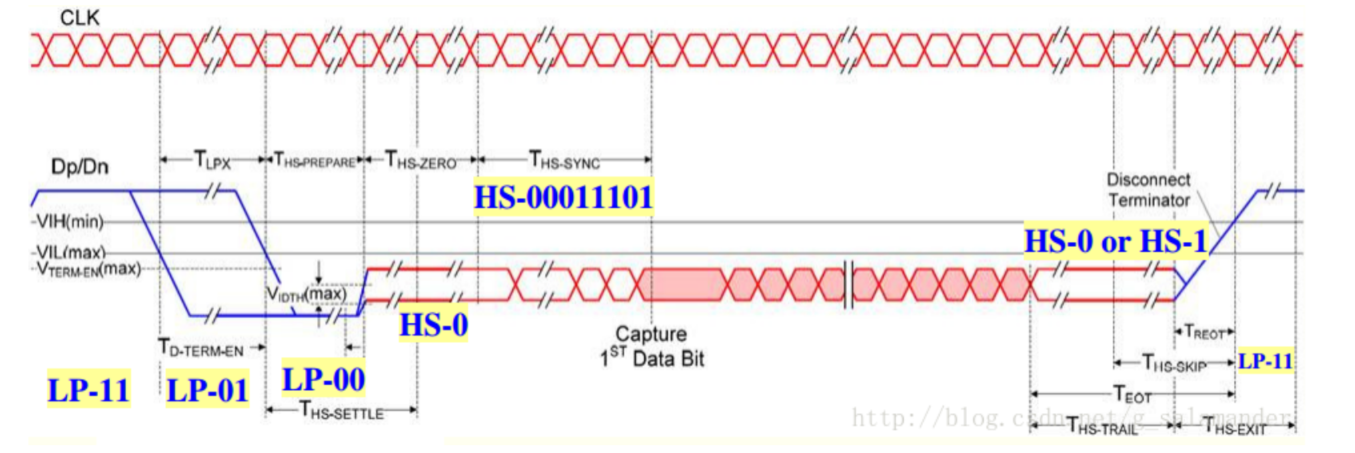

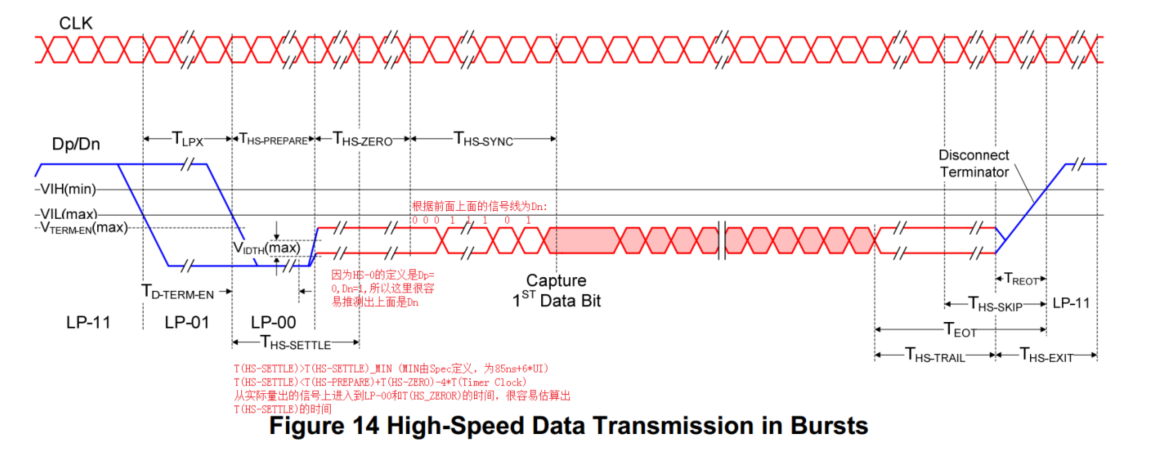

High-Speed mode 进入时序:LP11→LP01→LP00→SoT(0001_1101),退出时序:EoT→LP11,时序图如下:

- Turnaround 进入时序:LP11→LP10→LP00→LP10→LP00,退出时序:LP00→LP10→LP11

这是开启 BTA 的时序,一般用于从 slave 返回数据如 ACK: 0x84。

5、时序要求

在调试 DSI 或者 CSI 的时候, HS mode 下的几个时序非常重要:T_LPX,T_HS-SETTLE ≈ T_HS-PREPARE + T_HS-ZERO,T_HS-TRAIL,一般遵循的原则为:Host 端的 T_HS-SETTLE > Slave 端的 T_HS-SETTLE。

5、数据包类型

短包:4 bytes,由 3 部分组成:

- Data Identifier (DI) * 1byte: Contains the Virtual Channel[7:6] and Data Type[5:0].

- Packet Data * 2byte:Length is fixed at two bytes

- Error Correction Code (ECC) * 1byte:allows single-bit errors to be corrected and 2-bit errors to be detected.

长包:6 ~ 65541 bytes,同样由 3 部分组成:

- Packet Header(4 bytes) - 包头

Data Identifier (DI) * 1byte:Contains the Virtual Channel[7:6] and Data Type[5:0].

Word Count (WC) * 2byte:defines the number of bytes in the Data Payload.

Error Correction Code (ECC) * 1byte:allows single-bit errors to be corrected and 2-bit errors to be detected. - Data Payload(0~65535 bytes) - 有效数据

Length = WC × bytes - Packet Footer(2 bytes):Checksum - 包尾

If the payload has length 0, then the Checksum calculation results in FFFFh

If the Checksum isn’t calculated, the Checksum value is 0000h

MIPI规定,传输过程中,包内是200mV、包间以及包启动和包结束时是1.2V,两种不同的电压摆幅,需要两组不同的LVDS驱动电路在轮流切换工作;为了传输过程中各数据包之间的安全可靠过渡,从启动到数据开始传输,MIPI定义了比较长的可靠过渡时间,加起来最少也有600多ns;而且规定各个时间参数是可调的,所以需要一定等待时间,需要缓存,我们用寄存器代替FIFO,每通道128Byte。

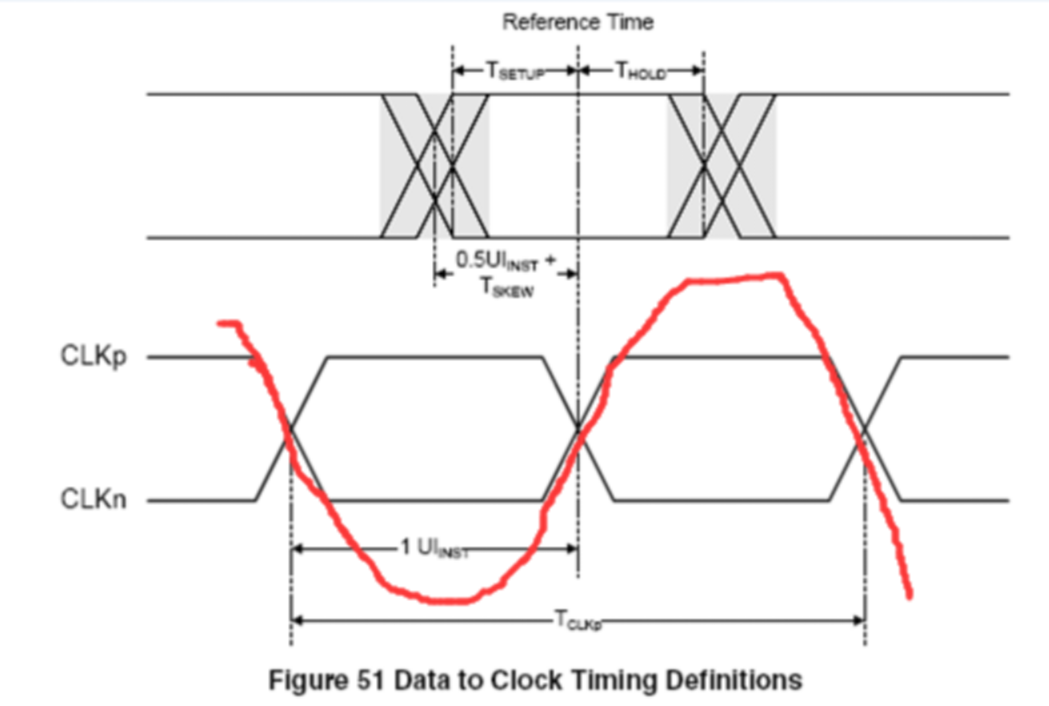

数据与时钟的相位关系:

CLKp是高电平,CLKn是低电平的时候,差分信号表现为高电平。

CLKn是高电平, CLKp是低电平的时候,差分信号表现为低电平。

所以结果就可以等效成红线描述的正弦。

从正弦可以看出,data在clk的高电平和低电平都有传输数据。

数据通道进入和退出SLM(即睡眠模式)的控制: