前言

在之前用到的仿真工具只有vivado与modelsim,vivado的笨重不用多说,可能你搭建一个工程的时间比你看波形的时间还要长,modelsim倒是稍微轻一些,但步骤也较为繁琐,虽然我在之前也意外收获了modelsim的仿真脚本模板且屡试不爽,但还是觉得稍微有些麻烦,正好之前在学习tinyrv时安装了iverilog与gtkwave,且在网上看到有搭建verilog仿真环境的教程,遂抽出一早上时间搭建该环境

注意

本文所实现的案例是一个非常简单的例子,如有更复杂的场景(如需要用到xinilx、altera等厂商的器件库),请参考我如下列出的文章

参考文章

https://developer.aliyun.com/article/1077579#:~:text=Icarus%20Ver

https://zonepg.github.io/posts/programming/ca/2021-03-25-iverilog-gtkwave/#:~:text=%E6%89%80%E4%BB%A5%E5%9C%A8%E7%BD%91%E4%B8%8A%E6%89%BE%E4%BA%86%E4%B8%80%E4%BA%9B%E8%BD%BB

https://www.cnblogs.com/quantoublog/articles/18089793#:~:text=iVerilog%E7%9A%84%E5%AE%89

环境搭建

1.下载iverilog与gtkwave

安装:https://bleyer.org/icarus/

应该是同时将二者安装好的,详细的安装步骤不再赘述

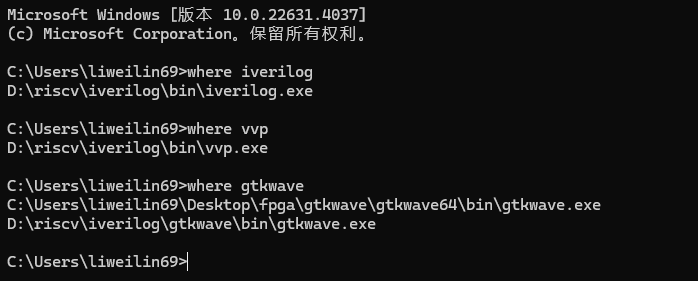

打开cmd使用以下命令可查看安装路径(注意一定得是cmd,不能随便打开某个目录的终端!):

where iverilog

where vvp

where gtkwave

如下所示:

三者的功能:

iverilog:用于编译verilog和vhdl文件,进行语法检查,生成可执行文件

vvp:根据可执行文件,生成仿真波形文件

gtkwave:用于打开仿真波形文件,图形化显示波形

2.准备工作

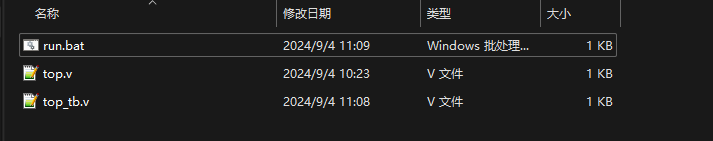

我这里是以一个简单的例子实现,在工程文件夹下准备如下文件:

其中:

top.v是一个简单的c程序

点击查看代码

module top(clk,a,b,y,x);

input a,clk;

input b;

output reg [2:0] y = 0;

output reg [2:0] x = 0;

always @(posedge clk)beginy = a + b;x = y + a;end

endmodule

点击查看代码

`timescale 1ns/1ps

module top_tb();reg a,b,clk;

wire [2:0] y;

wire [2:0] x;

always #10 clk = ~clk;initial begina = 0;b = 1;clk = 0;#210a = 1;#200b = 0;#20000$stop;

end/*iverilog */

initial

begin $dumpfile("wave.vcd"); //生成的vcd文件名称$dumpvars(0, top_tb); //tb模块名称

end

/*iverilog */top u_top(.a(a),.b(b),.clk(clk),.y(y),.x(x);

endmodule

点击查看代码

% Start compiling %

iverilog -o wave %*

% Generating wave file %

vvp -n wave -lxt2

% Opening wave file %

gtkwave wave.vcd

点击查看代码

/*iverilog */

initial

begin $dumpfile("wave.vcd"); //生成的vcd文件名称$dumpvars(0, top_tb); //tb模块名称

end

/*iverilog */

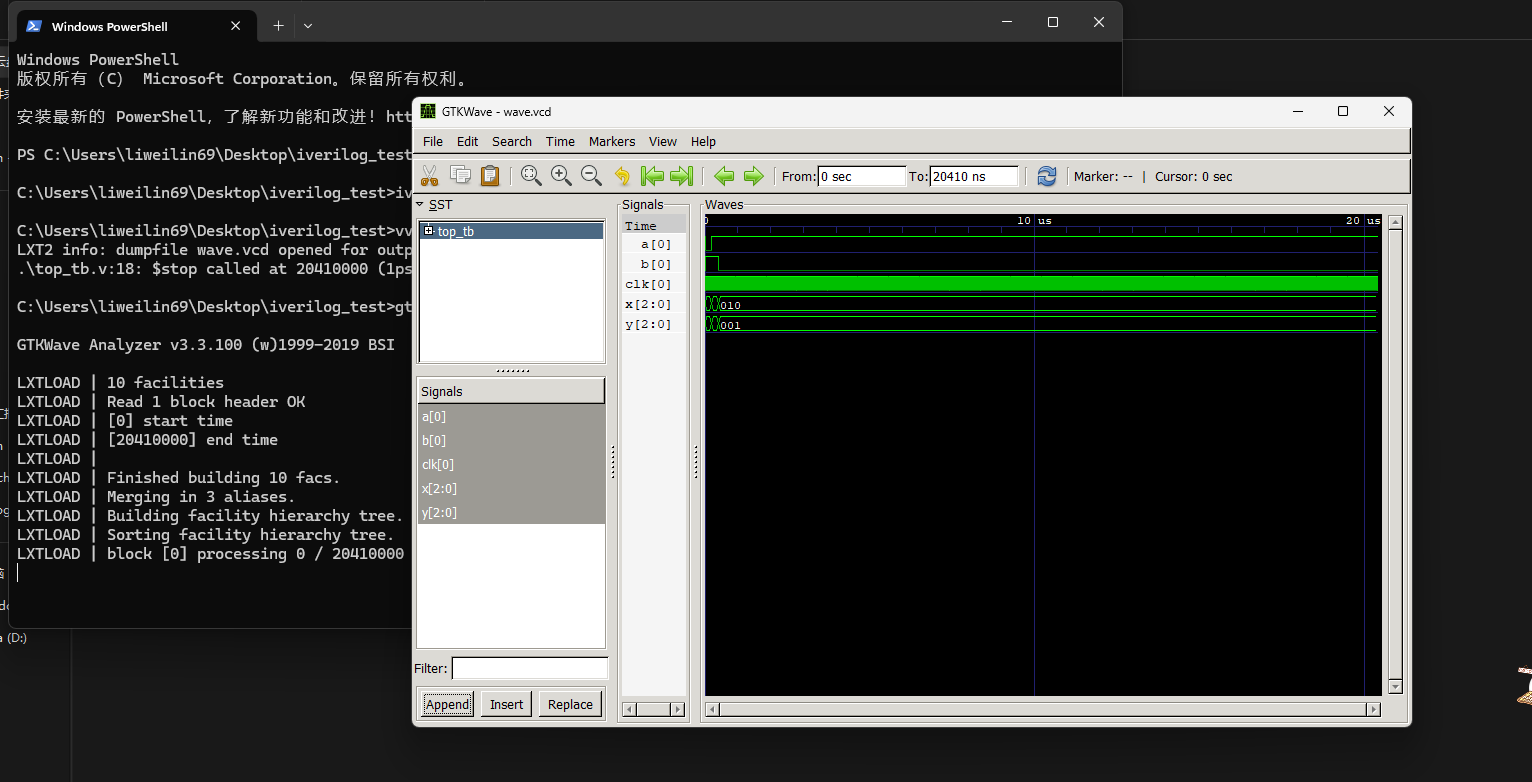

3.仿真波形

打开该目录的终端,运行如下命令:

.\run.bat .\top.v .\top_tb.v

就是执行脚本文件与本案例的两个文件

运行后直接回打开gtkwave并读入vcd,接着选中信号append进去就好了