推理引擎流程

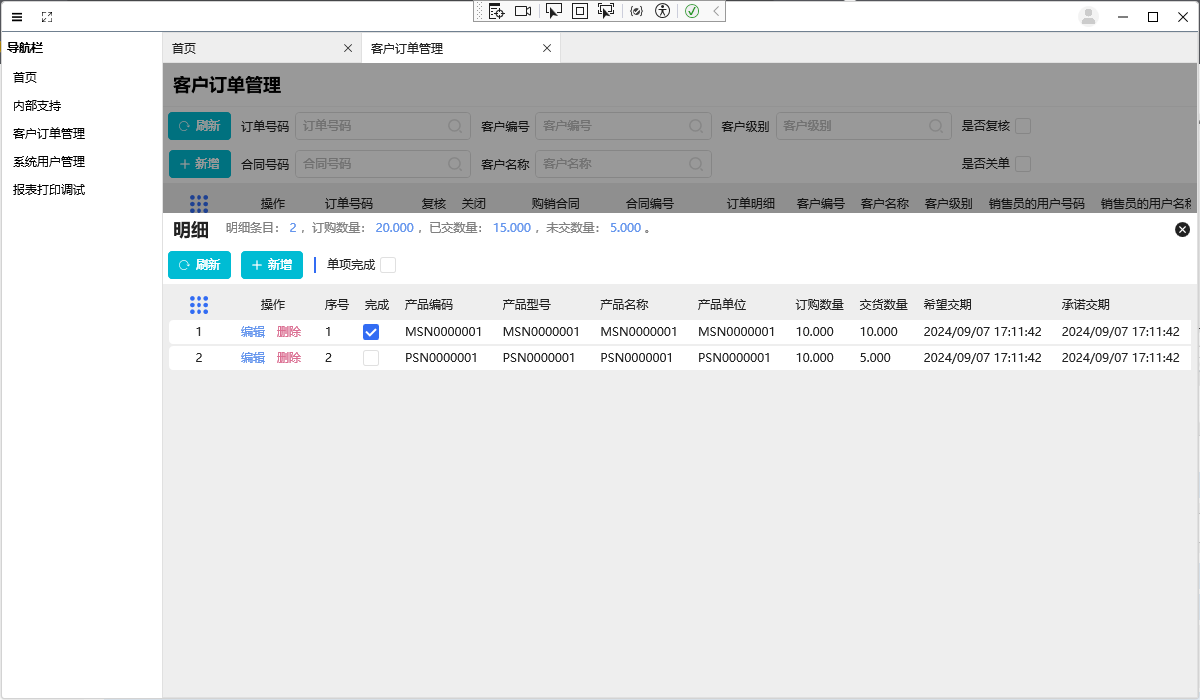

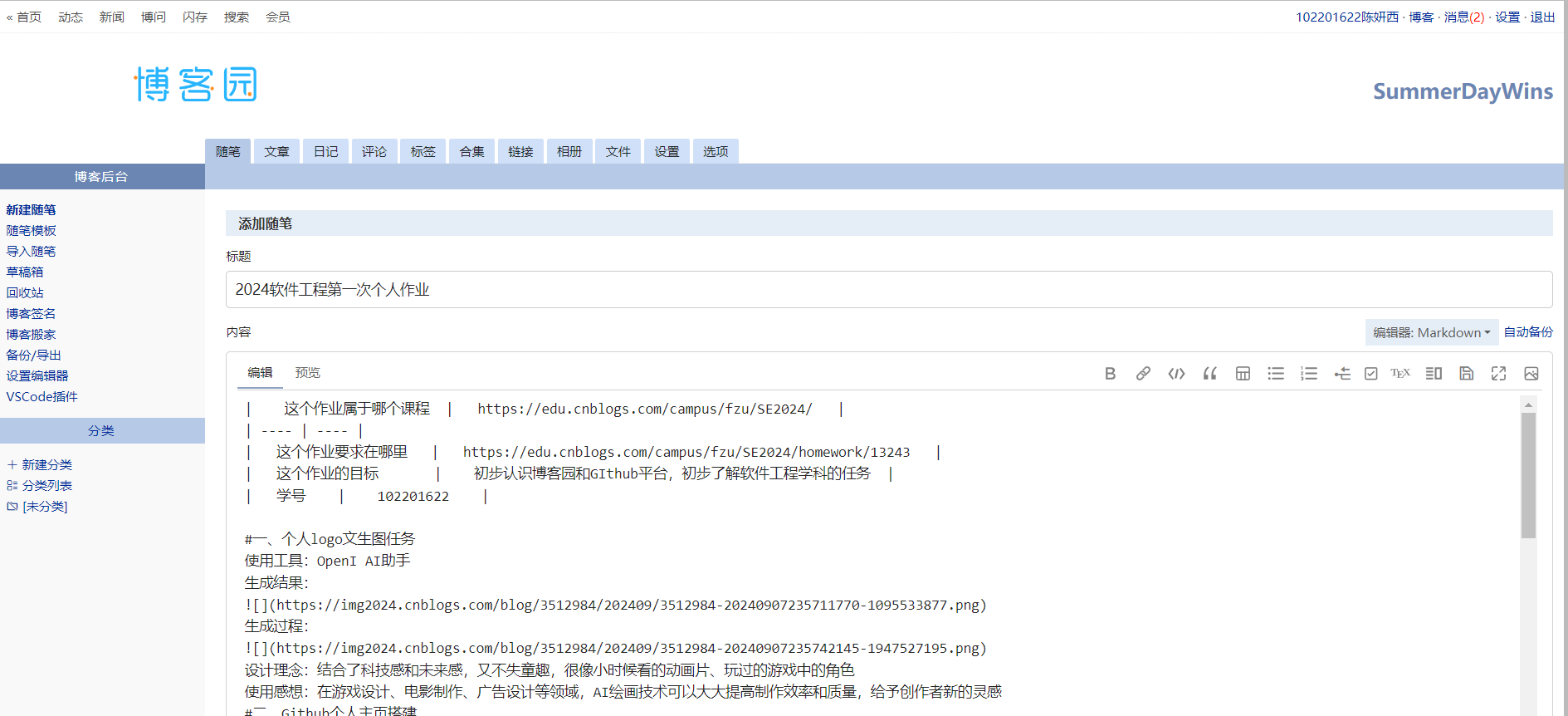

总结一下推理引擎(IE)调用FPGA设备的流程。开发人员通过IE通用API进行推理调用,IE调用FPGA插件,这调用了运行OpenCL运行时的DLA(英特尔深度学习加速器)。最终发送到实现基元(如卷积、ReLU等)的DLA FPGA IP。如图11-28所示。

图11-28 推理引擎(IE)调用FPGA设备的流程

位流

深度学习部署工具包(DLDT)随附许多位流,用于各种板卡、推理中使用的数据类型和DL模型。

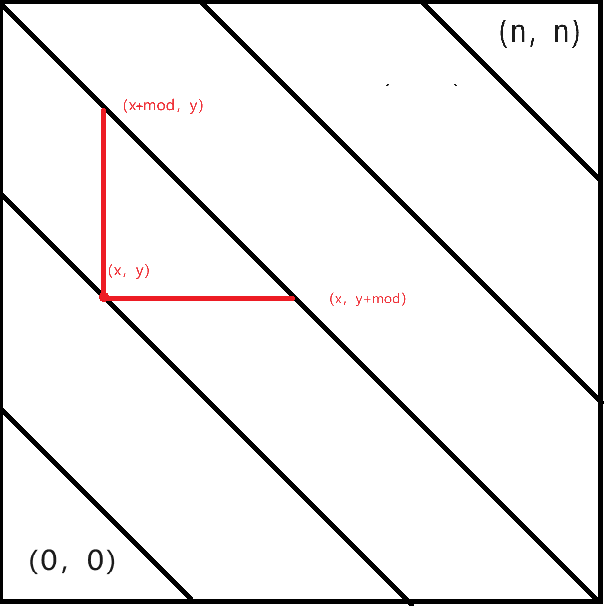

这些FPGA块可以通过垂直和水平线连接在一起。

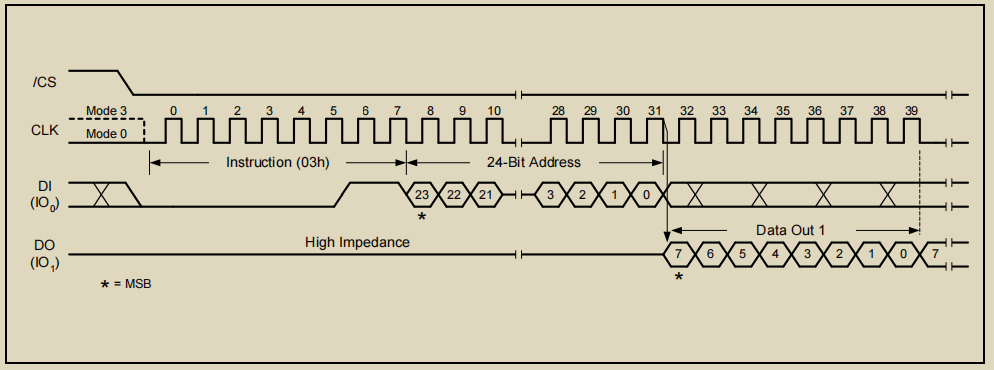

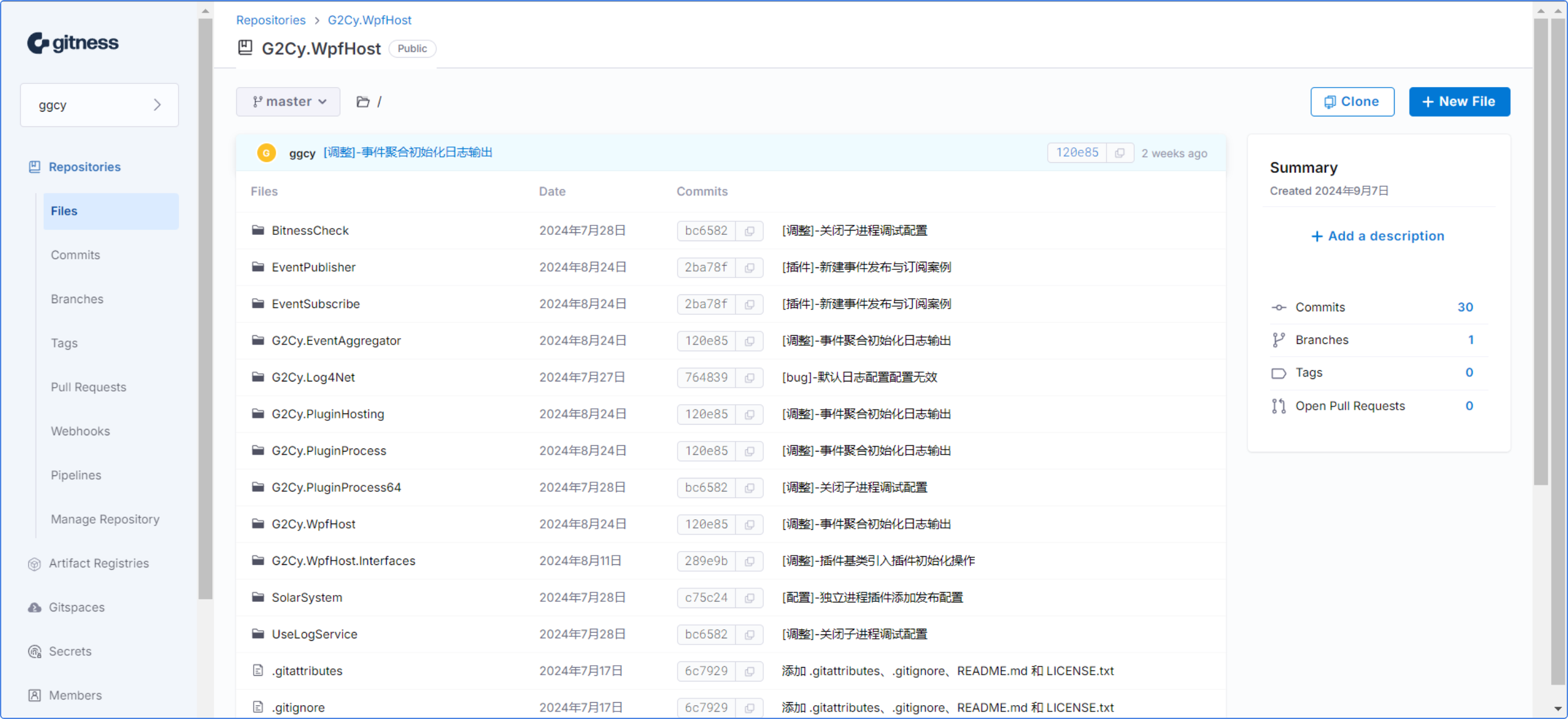

如何利用这个信息似乎并不明显。但是Winograd在40多年前解决了一个类似的问题。假设有两种预处理方法,将4×4数据和3×3滤波器分别转换为两个4×4矩阵(左侧下面的前两行),如图11-29所示。

图11-29 将4×4数据和3×3滤波器分别转换为两个4×4矩阵

然后将卷积应用于这两个转换矩阵。由于两者大小相同,卷积只需要进行16次乘法。最后,执行后处理转换,将其转换回2×2矩阵。结果表明,产生相同的卷积结果存在这样的预处理和后处理转换。更好的消息是,这些转换只涉及简单的加减运算,而不涉及乘法。因此,新的Winograd变换可以节省大量计算。

用1-D数据和滤波器来来证明这个想法。

(11-1)

其中

(11-2)

数据⊗滤波器的原始卷积方法涉及6次乘法。将合并预处理、卷积、后处理步骤,并展示它可以从上面计算m₁、m₂、m₃和m₄中推导出来。使用这个Winograd变换,只需要进行4次乘法。

为了完整起见,这里列出了所需的数学变换。可以使用简单的算术运算来完成预处理变换Gg、Bᵀ和后处理变换Aᵀ。

(11-3)

其中,

(11-4)

在FPGA中,可以在硬件中应用Winograd变换来加速卷积,如图11-30所示。

图11-30 可以在硬件中应用Winograd变换来加速卷积