英特尔FPGA深度学习加速(DLA)套件

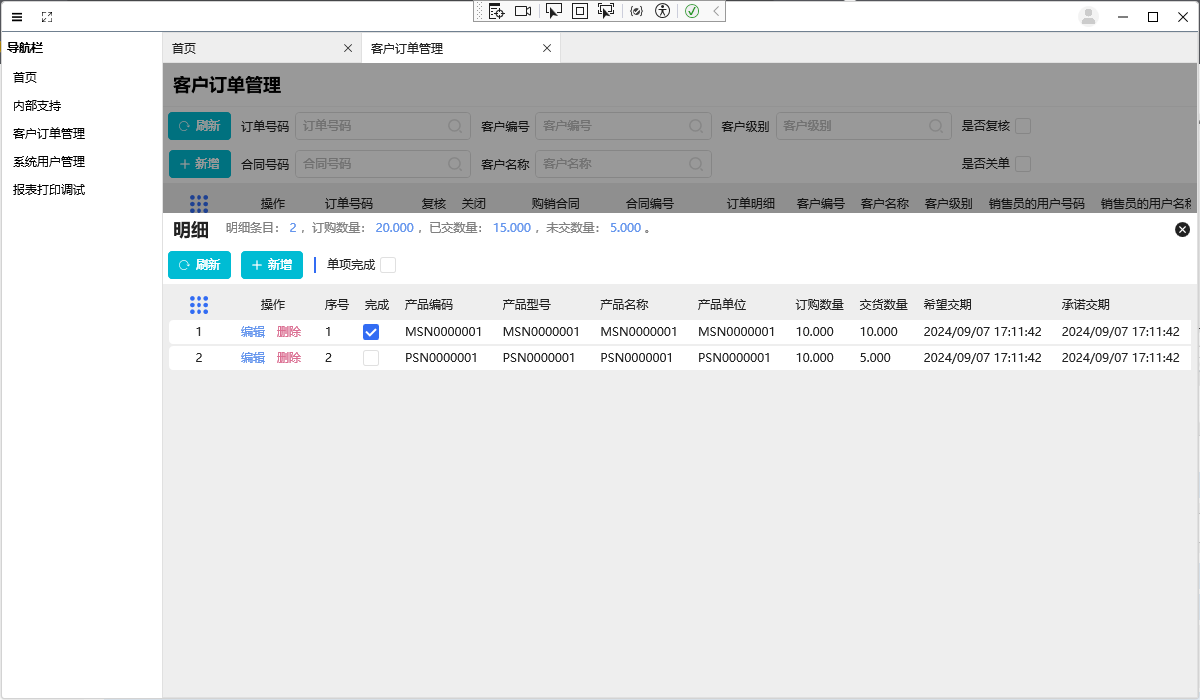

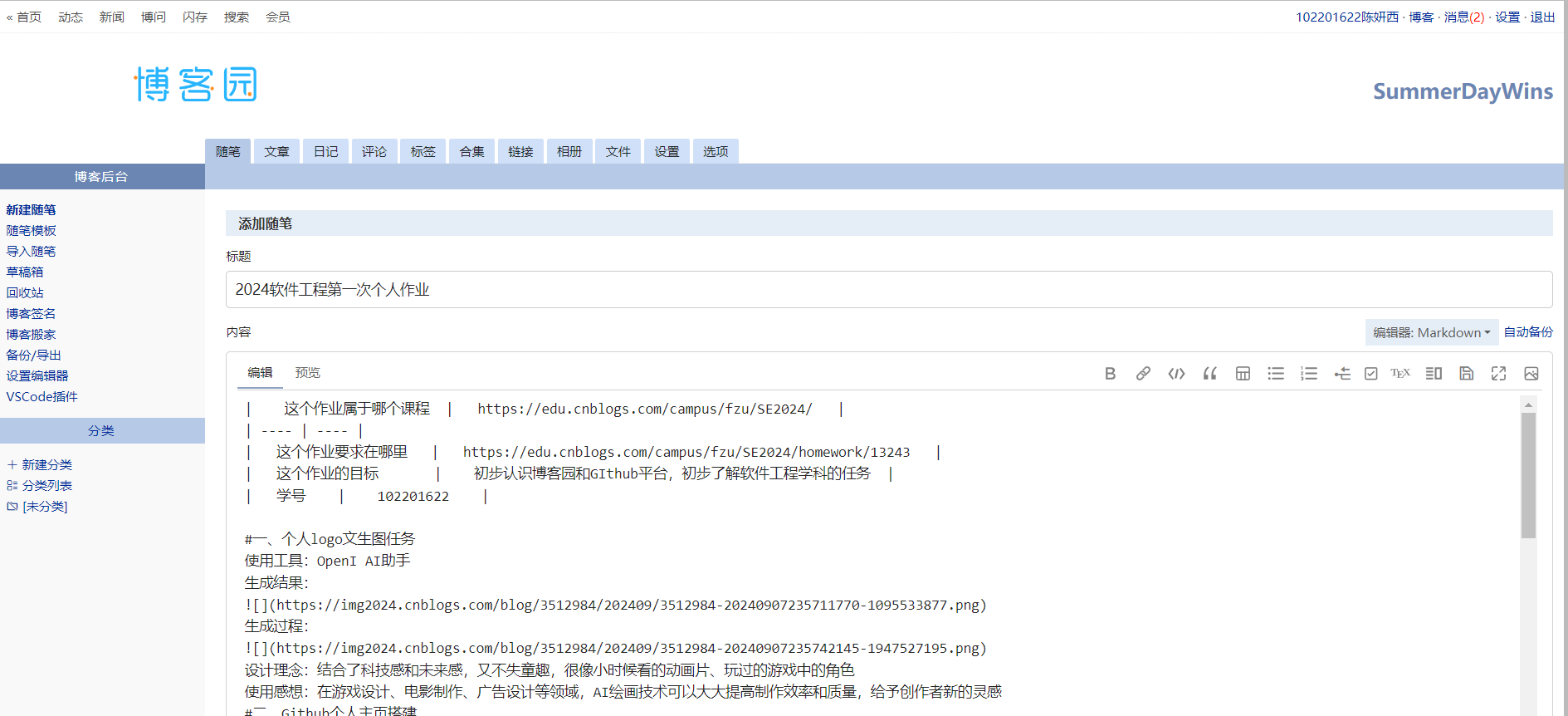

英特尔FPGA的DLA加速套件,如图11-17所示。

图11-17 英特尔FPGA的DLA加速套件

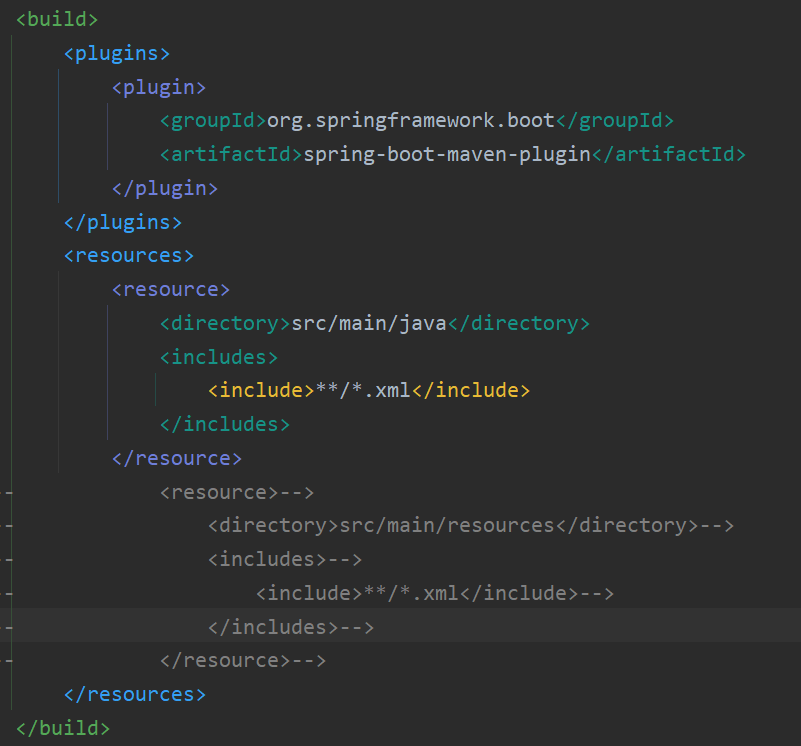

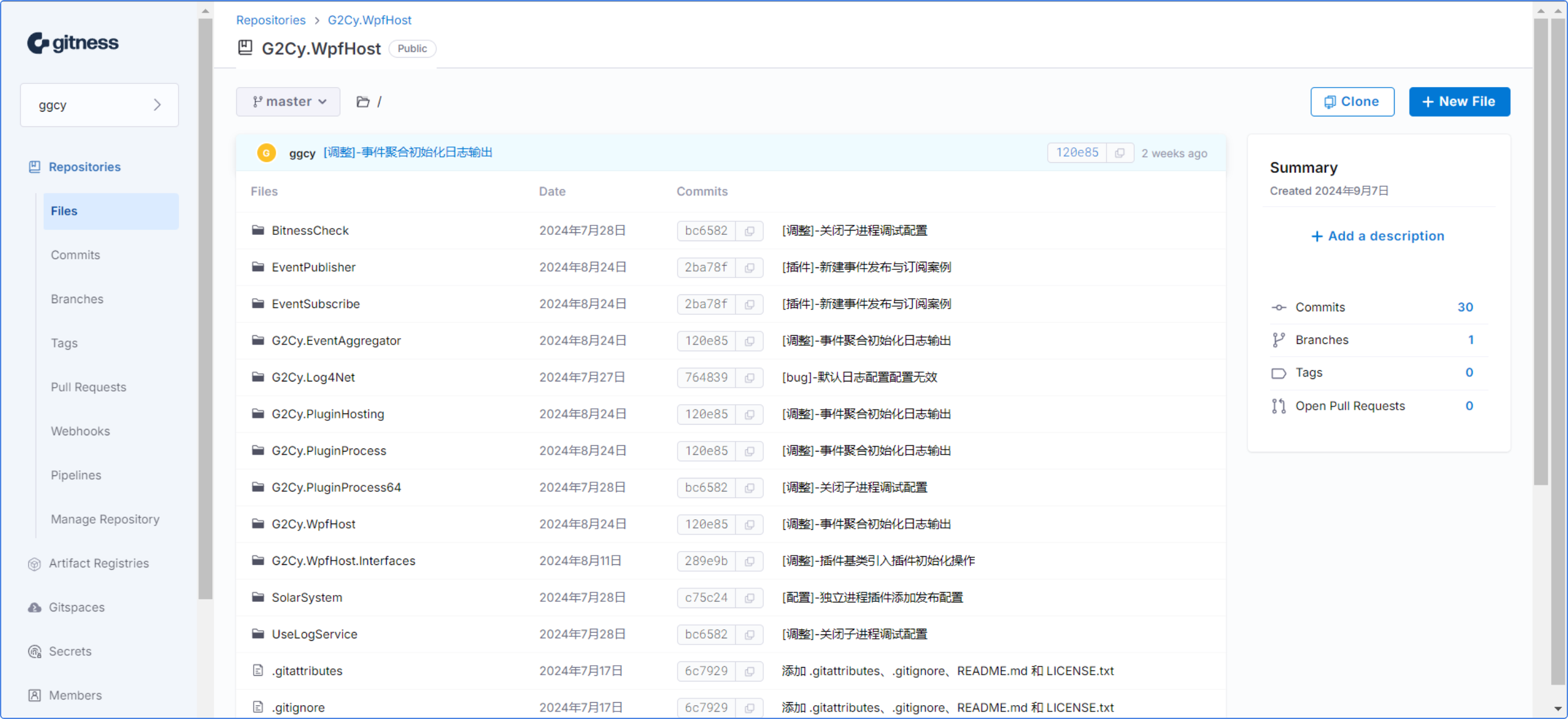

深度学习部署工具包(DLDT)中的推理引擎,提供了一个高级的设备无关API来编程推理。这是一些示例代码,如图11-18所示。

图11-18 深度学习部署工具包(DLDT)中的推理引擎示例代码

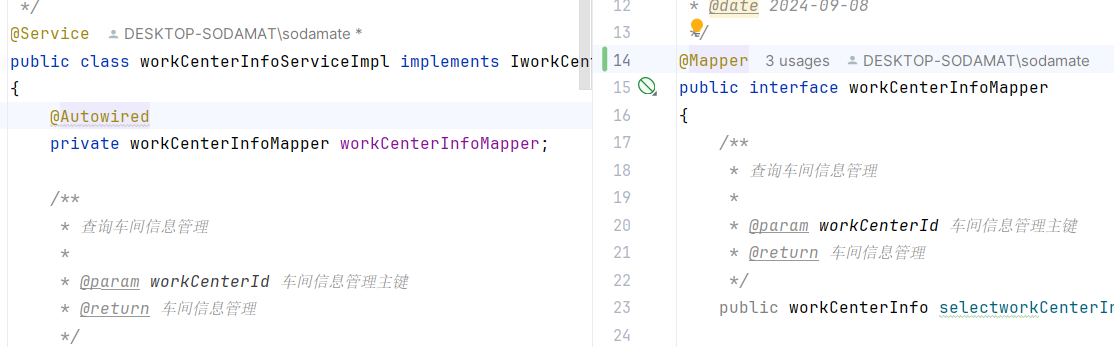

推理引擎加载用户提供的IR并调用相应的插件来处理特定设备的推理,如图11-19所示。

图11-19 推理引擎加载用户提供的IR并调用相应的插件来处理特定设备的推理

对于FPGA,它调用了DLA(深度学习加速)运行时引擎,如图11-20所示。

图11-20 FPGA调用了DLA(深度学习加速)运行时引擎

如图11-21,驱动加速器中DL模型的执行。

图11-21 驱动加速器中DL模型的执行

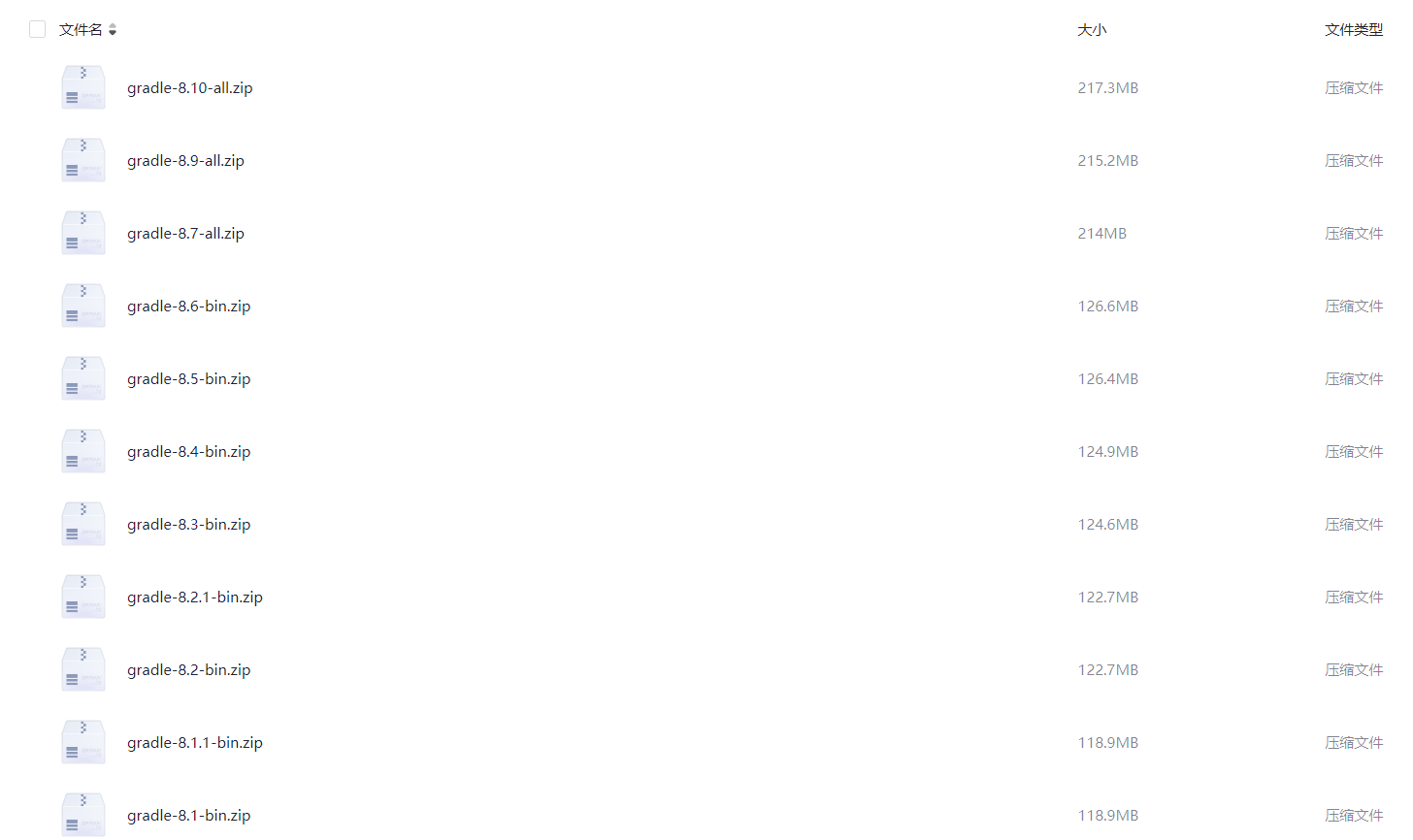

部署DNN模型是一个软件过程。FPGA已经预先编程了一个为DLA运行DL模型而设计的比特流。不需要FPGA编译。如图11-22所示。

图11-22 FPGA已经预先编程了一个为DLA运行DL模型而设计的比特流

这里是DLA 运行时用于运行DL模型的DLA架构。该架构包含卷积PE(处理元素)阵列、用于存储特征图和 DL 中常用的层(组件)的缓存,如图11-23所示。

图11-23 DLA 运行时用于运行DL模型的DLA架构

将DNN模型映射到这个加速引擎架构中。许多DL模型,如AlexNet,包含高度相似的层序列组,例如卷积层后跟ReLU、归一化和最大池化。如图11-24所示。

图11-24 将DNN模型映射到这个加速引擎架构中

在FPGA内部DL层是由配置的互连链接的块实现的,如图11-25所示。

图11-25 在FPGA内部DL层是由配置的互连链接的块实现的

要运行一组层,创建一个数据流并通过负责特定类型DL层的块传递它。要执行整个模型,重复流式循环以处理下一组,直到所有DNN层都被处理。如图11-26所示。

图11-26 创建一个数据流并通过负责特定类型DL层的块传递

这些块在运行时高度可重构且可绕过。这使得深度学习层(DL)的不同设计参数(如CNN步幅)或跳过不需要的层成为可能。如图11-27所示。

图11-27 在运行时高度可重构且可绕过

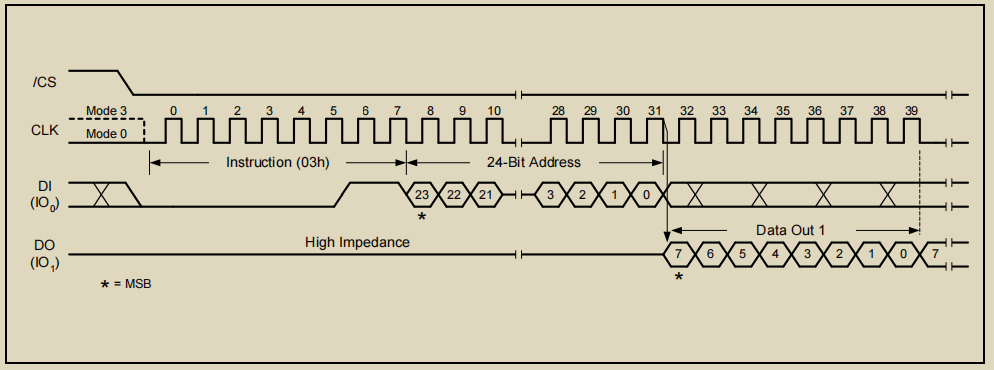

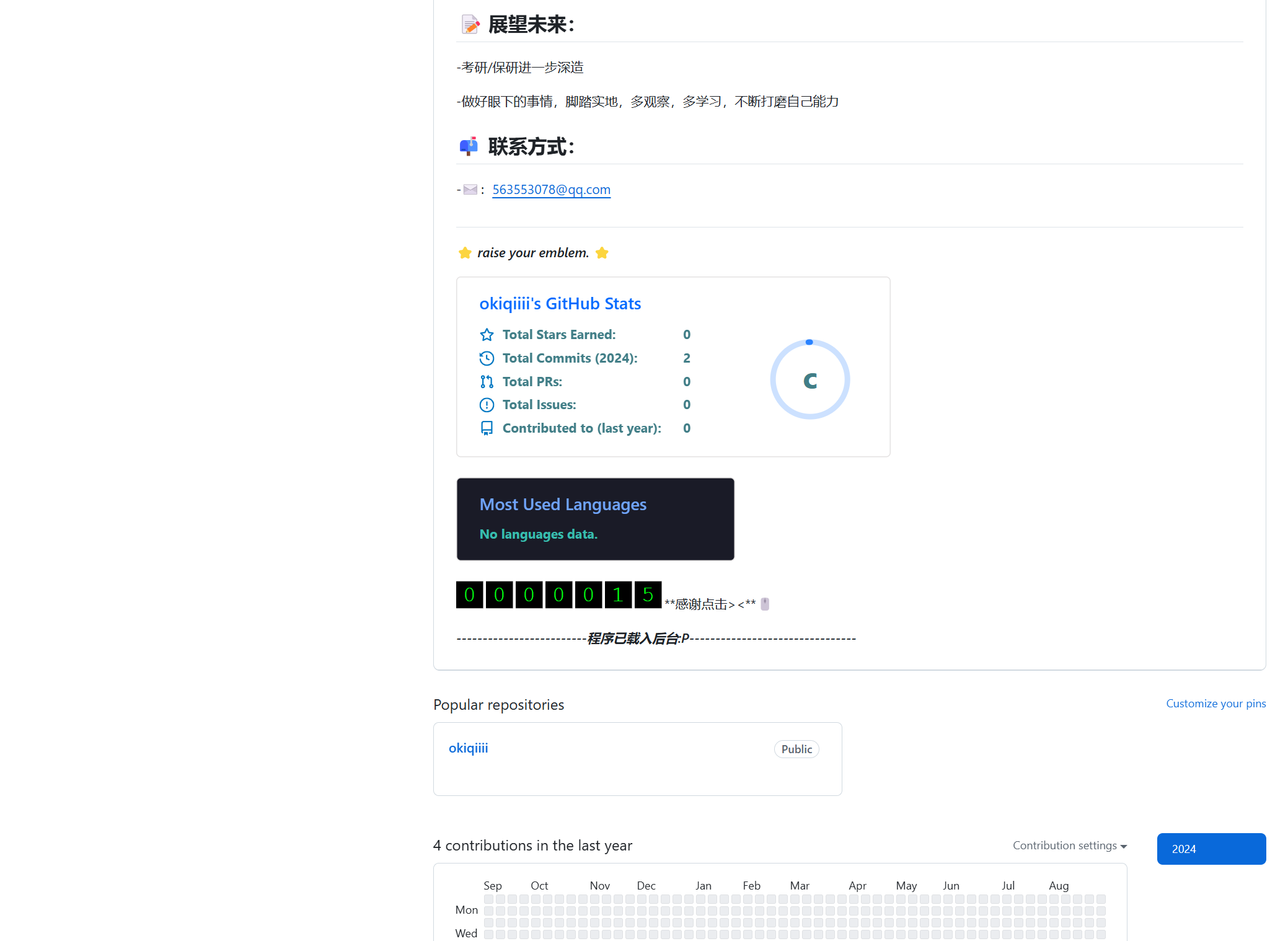

首先,视频数据从DDR(双数据率)通道到达,如图11-28所示。

图11-28 视频数据从DDR(双数据率)通道到达

如果视频数据太大而无法存储在芯片上的流缓存中,则将其切片并在多个流水线迭代中逐个传递。在每个迭代中,数据从缓存中提取并通过卷积PE阵列(PE-处理元素)和激活块进行处理。然后通过交叉开关(XBAR)传递给其他块,例如标准化和最大池化。然后将数据反馈到流缓存中,以供下一组层使用。一旦整个模型处理完毕,就会将其写回内存并继续处理下一片数据。以图11-28表总结了深度学习加速器(DAL)引擎用于执行DL模型的图循环架构。