目录

5.1 Primary test access port

5.1.1 Specifications

5.1.2 Description

5.2 Primary test access port controller

5.2.1 Specifications

5.2.2 Description

5.3 Secondary test access port (STAP)

5.3.1 Specifications

5.3.2 Description

5.4 Secondary test access port control logic

5.4.1 Specifications

5.4.2 Description

5.5 Registers

5.5.1 Secondary test access port configuration register (3DCR)

5.5.2 Die wrapper register (DWR)

5.5.3 Flexible parallel port configuration register

5.5.4 ECID register

5.5.5 Bypass register

5.5.6 Instruction register and instructions

最近在学习1838协议的内容,本文翻译的内容来自DeepSeek和博主的个人理解,因为博主也在学习过程中,所以水平有限。如有理解错误,欢迎在评论区指正。

附上1838协议原文链接:1838-2019 - IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits | IEEE Standard | IEEE Xplore

5. Serial test access ports

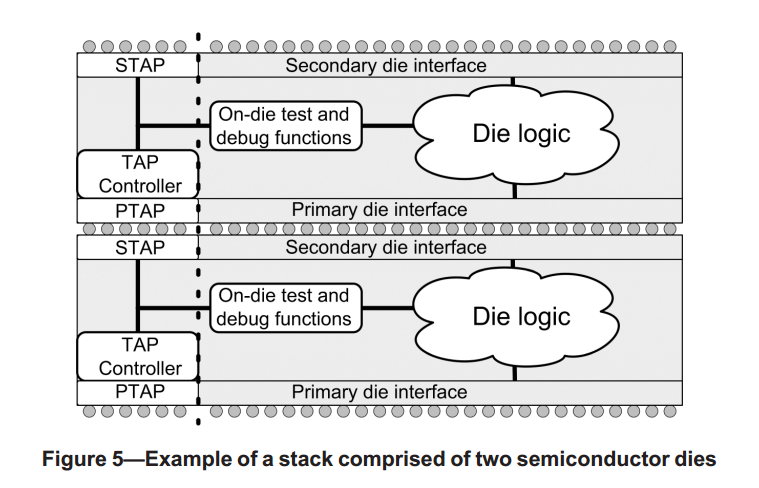

如图5所示,Primary Interface的一个子集应为primary test access port(PTAP),其中包含与Primary Interface相关的信号和内部芯片逻辑连接;而secondary interface的一个子集应为一个或多个secondary test access ports(STAPs),其中包含与secondary interface相关的信号和内部芯片逻辑连接。需要注意的是,Primary Interface和secondary interface还可能包括一个可选的flexible parallel port(FPP),这一部分将在第7条中进一步讨论。

5.1 Primary test access port

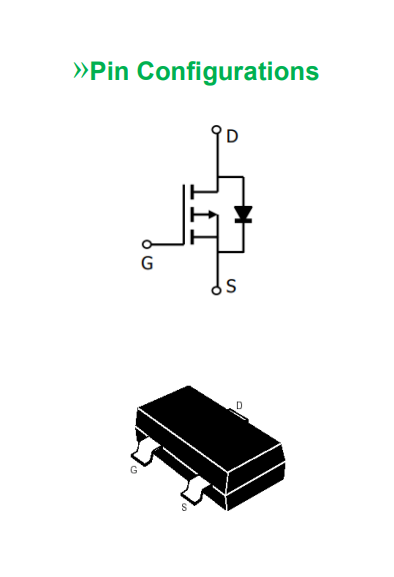

串行PTAP是强制支持的。PTAP(Primary test access port)与最接近电路板连接或封装接口的表面相关,并有五个接口:TCK、TMS、TDI、TDO 和 TRSTN。

5.1.1 Specifications

规则如下:

a) 每个符合标准的芯片都应在其primary Interface中包含一个串行测试访问端口(PTAP)。

b) PTAP应由五个信号组成,分别为TCK、TMS、TDI、TDO和TRSTN。(译注:TRSTN在1149中是可选的,在这里是强制的)

c) TCK信号应为时钟输入信号,用于同步测试架构操作和寄存器。

d) 在TMS(测试模式选择)接口上的信号应在TCK的上升沿被采样到测试逻辑中。

e) 在TDI(测试数据输入)接口上的信号应在TCK的上升沿被采样到测试逻辑中。

f) 通过TDO(测试数据输出)驱动的信号状态变化仅应在TCK的下降沿或复位(Reset*)信号激活时发生。

g) TRSTN(测试复位)信号应为异步的低电平有效控制输入信号,为该标准定义的测试寄存器提供异步复位功能。

h) TCK、TMS和TDI信号应由专用接口驱动。

i) TDO信号应驱动一个专用接口。

j) 第一个芯片的TRSTN信号应由专用接口或提供上电复位(POR)功能的逻辑驱动。

k) 对于非第一个芯片,TRSTN信号应从专用接口驱动。

建议如下:

l) 第一个芯片的TRSTN信号应由专用接口驱动。

5.1.2 Description

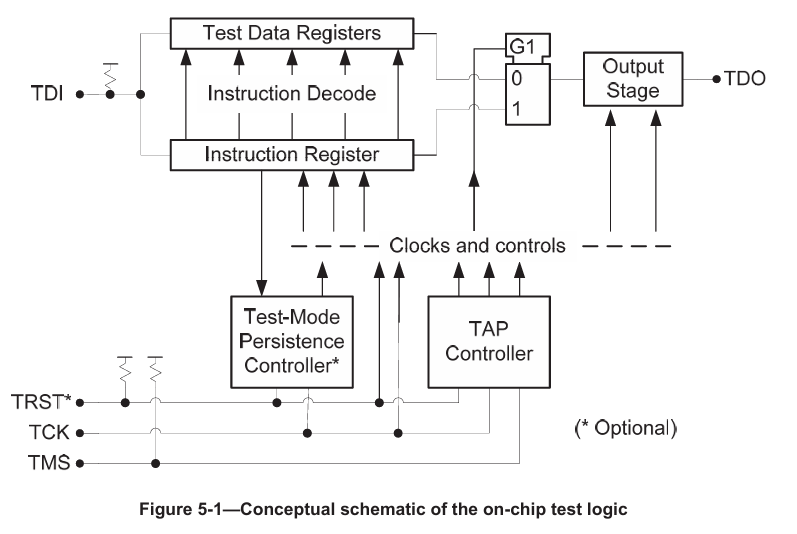

这五个芯片接口代表了通常与符合IEEE 1149.1接口相关的信号——在IEEE 1838芯片用作第一个芯片(即最靠近板连接的芯片)的情况下,这五个接口实际上可能代表IEEE 1149.1 TAP接口到板连接,如果需要IEEE 1149.1合规性要求(请注意,IEEE 1838合规性并不要求IEEE 1149.1合规性——只有当最终组件有单独的IEEE 1149.1合规性要求时,才需要IEEE 1149.1合规性)。这五个信号是:

输入测试时钟(TCK):同步所有测试架构寄存器的时钟信号。

测试模式选择(TMS):提供输入控制信号到测试控制器有限状态机(FSM),生成所有测试架构寄存器的操作协议。

低电平有效测试复位(TRSTN):提供输入异步复位信号,可用于将所有测试架构寄存器置于已知的默认状态。

串行测试数据输入(TDI):允许在测试控制器FSM处于其中一个移位状态时,在TCK时钟的上升沿将串行数据传递到测试架构数据寄存器。

串行测试数据输出(TDO):允许在测试控制器FSM处于其中一个移位状态时,在TCK时钟的下降沿将测试架构数据寄存器的串行数据呈现到芯片接口。

5.2 Primary test access port controller

PTAP信号驱动PTAP控制器,这是一个符合IEEE 1149.1标准的TAP控制器。与PTAP控制器相关的寄存器架构包括支持IEEE Std 1838中所需或可选的3D特性的寄存器。

5.2.1 Specifications

规则如下:

a) PTAP信号应连接到PTAP控制器和相关的寄存器架构。

b) PTAP控制器应按照IEEE 1149.1 TAP控制器有限状态机(FSM)定义的操作序列进行操作,该操作序列基于TMS输入控制信号,并由TCK输入时钟信号进行同步(见IEEE Std 1149.1-2013第6.1节)。

5.2.2 Description

像IEEE 1149.1 TAP一样,PTAP可以访问堆叠中任何数量的芯片内部寄存器。然而,PTAP控制器寄存器架构至少应包含旁路寄存器、一个或多个芯片包装寄存器(DWR)段、3D配置寄存器(3DCR)以及支持这些寄存器的所有必要指令。

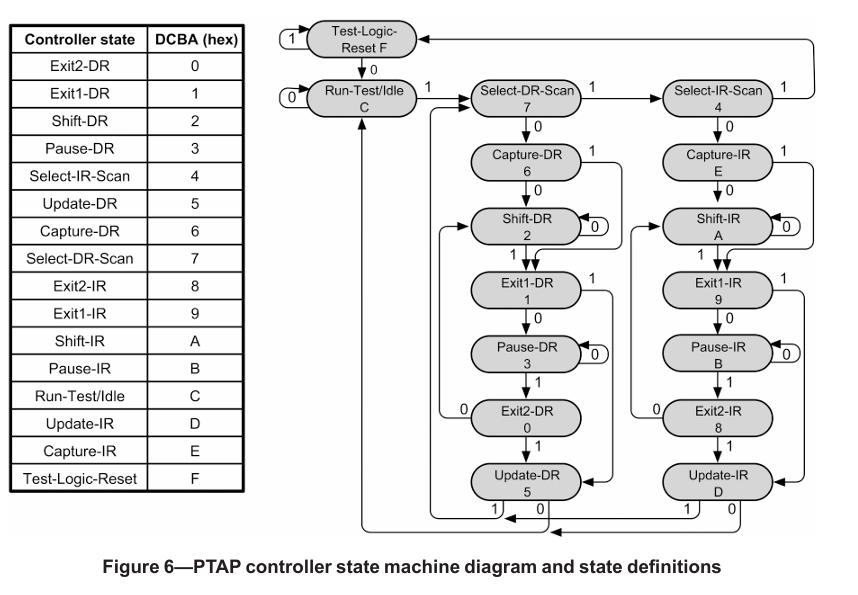

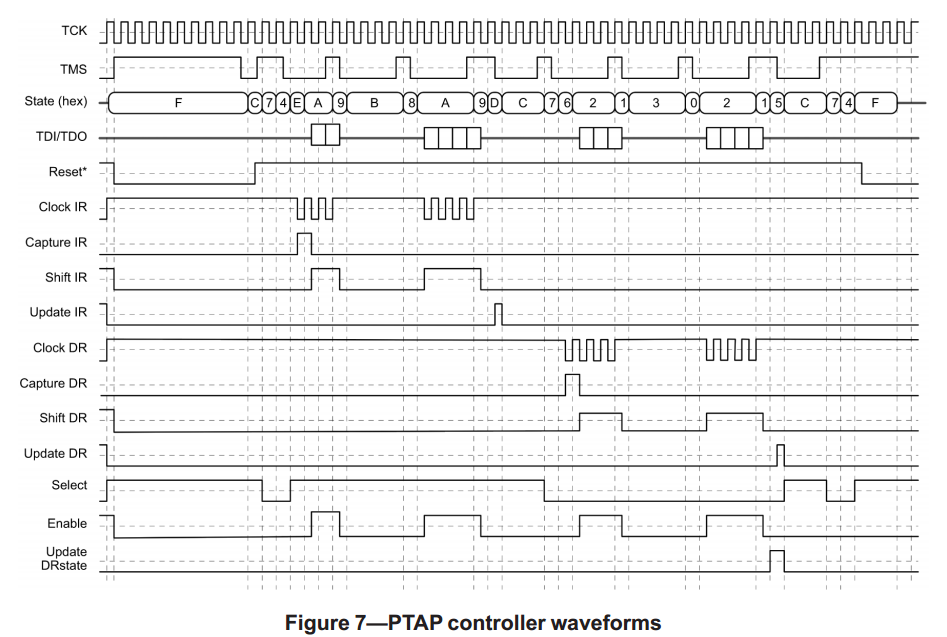

PTAP控制器的操作方式与IEEE Std 1149.1 TAP控制器在IEEE Std 1149.1-2013第6.1节中描述的方式相同。图6展示了PTAP控制器的状态图,并用十六进制编号标注状态,与图7中显示的PTAP控制器波形一致。

注:这里显示的PTAP控制器的十六进制状态编号仅用于说明目的。PTAP控制器的实际状态编号由设计者决定

(译注:图7的行为依次是:Shift-IR Pause-IR Shift-IR Update-IR Shift-DR Pause-DR Shift-DR Update-DR。Enable信号在shift的时候有效,用于TDO输出的三态控制。Select用于Test Data Register和Instruction register二选一MUX的控制。)

(译注:图源:IEEE 1149.1协议)

5.3 Secondary test access port (STAP)

通过对IEEE 1149.1架构添加STAP(Secondary Test Access Port,次级测试访问端口)及其相关的选择和配置控制逻辑,扩展出次级接口。该控制逻辑由STAP本身以及来自主TAP控制器的三个维度配置寄存器(3DCR,参见5.5.1节)的控制组成。次级接口可能支持多个STAP,每个STAP都有一个强制的五针测试接口,使其能够插入下一个芯片的PTAP(Primary Test Access Port,主测试访问端口)。

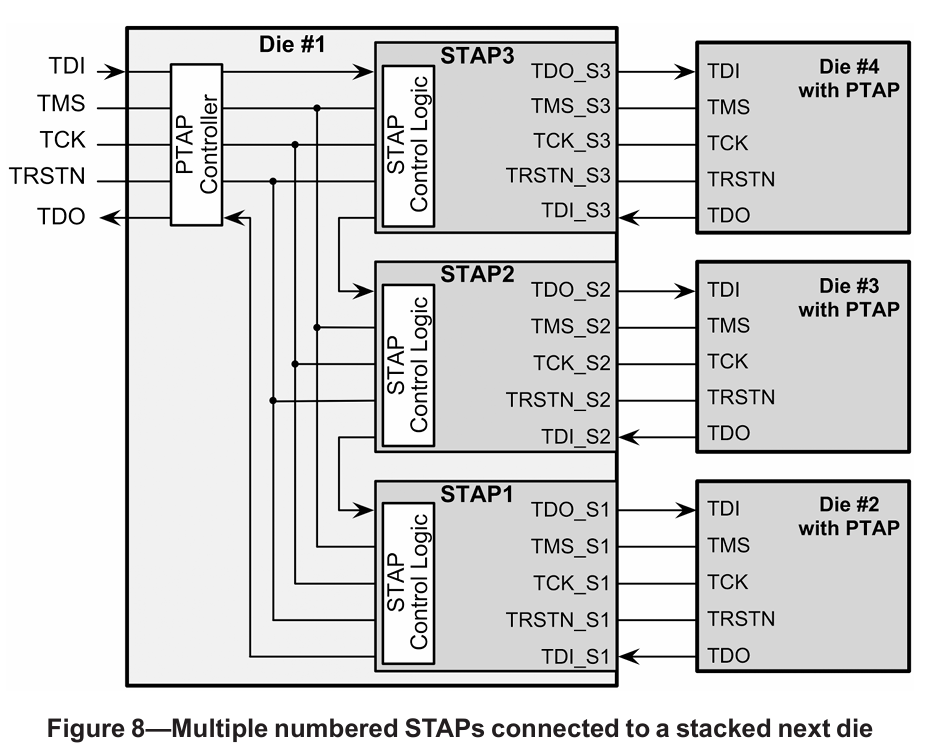

STAP将从1到n进行编号,从TDO PTAP信号开始,沿着串行扫描链回溯到TDI PTAP的起始点。

在本标准中,STAP应称为STAPn,其中n从1开始。如图8所示,STAP将从PTAP的TDO信号开始编号,从1到n,并沿串行扫描链回溯到TDI PTAP的起始点。如果存在多个STAP,则编号将按扫描路径顺序从PTAP的TDO端口向PTAP的TDI端口递增。因此,命名为STAP1的STAP将按扫描路径顺序最接近PTAP的TDO端口。

5.3.1 Specifications

规则如下:

a) 每个芯片应具有N个可选择的STAP,每个STAP直接一个芯片。

注——如果芯片不支持任何堆叠的下一个芯片,N可能为零。

b) 每个STAP应包括命名为TDI_Sn、TDO_Sn、TMS_Sn、TCK_Sn和TRSTN_Sn的端口,其中n表示STAP编号,0 < n ≤ N。

c) TCK_Sn输出端口应直接从PTAP的TCK端口驱动,不添加任何寄存器或组合门控逻辑。

d) TRSTN_Sn输出端口应直接从PTAP TRSTN信号驱动,不添加任何寄存器或组合门控逻辑。

e) TMS_Sn输出端口,当由PTAP的TMS端口驱动时,应直接驱动,不添加任何在线寄存器。

f) TDI_Sn输入端口应在TCK的上升沿采样数据。

G) TDO_Sn输出端口应在TCK的下降沿更新数据。

许可如下:

h)允许对驱动TCK_Sn、TMS_Sn和TRSTN_Sn端口的信号进行缓冲以增强驱动强度。

5.3.2 Description

TCK和TRSTN信号直接传递到STAP,除了一些缓冲(但不允许添加任何寄存器)。无论STAP是否被选中,它们都应始终传输到下一个芯片。

TMS、TDI和TDO信号仅在STAP被选中时才传输到下一个芯片或从下一个芯片传输来。这些信号中的每一个在处理过程中至少有一个多路复用器或逻辑门,以实现选择和取消选择。

STAP端口驱动当前芯片的次级接口端口,然后连接到下一个芯片的相关PTAP端口。TCK_Sn、TMS_Sn和TRSTN_Sn输出分别驱动下一个芯片的相关PTAP端口:TCK、TMS和TRSTN。STAP串行数据端口TDO_Sn输出和TDI_Sn输入,分别用于驱动和接收下一个芯片的PTAP端口对应端口:TDI输入和TDO输出。

TDI_Sn和TDO_Sn也需要寄存器,因为它们在TCK_Sn的上升沿或下降沿触发。TDI_Sn应在TCK_Sn的上升沿采样数据,TDO_Sn应在TCK_Sn的下降沿更新数据。

5.4 Secondary test access port control logic

STAP控制逻辑(简称STAP)由两个子组件组成:selector 和 retiming elements(译注:也即是MUX和寄存器)

5.4.1 Specifications

规则如下:

a) 每个STAP应使用3DCR中的相应Select_Sn信号进行选择。

b) 当Select_Sn信号被置1时, STAP选择下一个芯片的关联PTAP(介于TDO_Sn和TDI_Sn之间)。

c) 第一个STAP(编号为k)应在TCK的下降沿从PTAP的TDI_Sk_int获得TDO_Sk。(参考图8中的STAP编号。)

d) STAPn(n < k)应从STAPn+1的TDO_Sn+1_int源出TDI_Sn_int。(译注:STAP之间是串联的。)

e) 如果任何STAP被选中(至少有一个Select_Sn被置1),PTAP应从STAP1的TDO_S1_int源出TDO。

f) 最后一个STAP(编号为1)应将TDO_S1_int连接到PTAP TDO的触发器(由TCK的下降沿触发)之前的点。

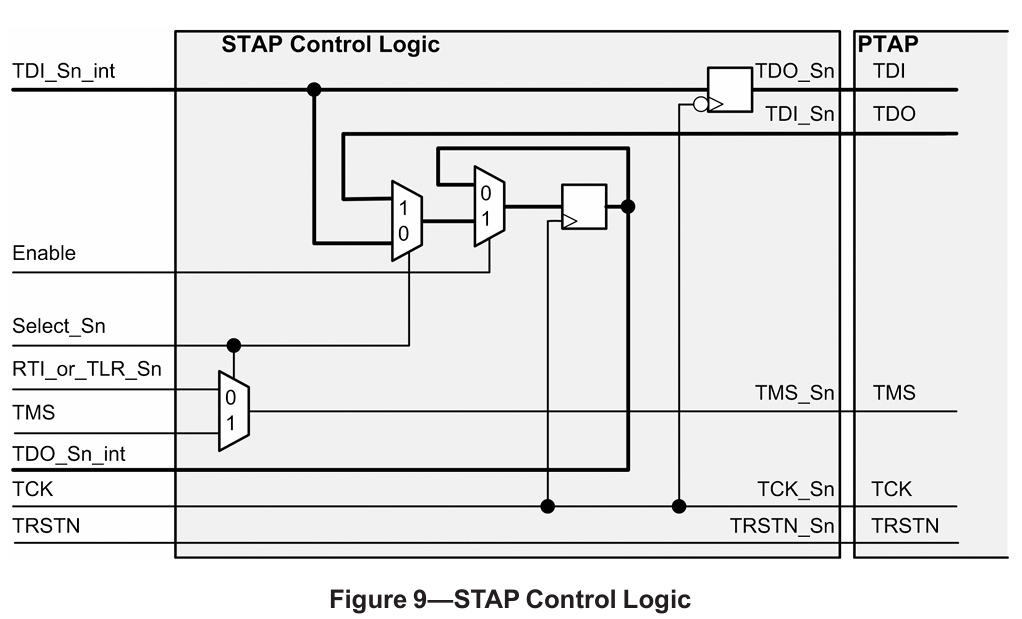

g)TDO_Sn_int应由一个寄存器元素驱动(在ShiftDR和ShiftIR状态下由TCK的上升沿触发),数据由TDI_Sn或TDI_Sn_int驱动,具体取决于Select_Sn的值。

注意——ShiftDR和ShiftIR在图9中由Enable信号表示。Enable信号是Shift_IR和Shift_DR信号的逻辑或(参见图7)。

h) TDO_Sn应由一个触发器驱动(例如,由TCK的下降沿触发),数据由TDI_Sn_int驱动。

i) 当STAP_Sn未被选中(Select_Sn为0)时,TMS_Sn应由RTI_or_TLR_Sn驱动(参见5.5.1)。

j) 当STAP_Sn被选中(Select_Sn为1)时,TMS_Sn应由TMS驱动。

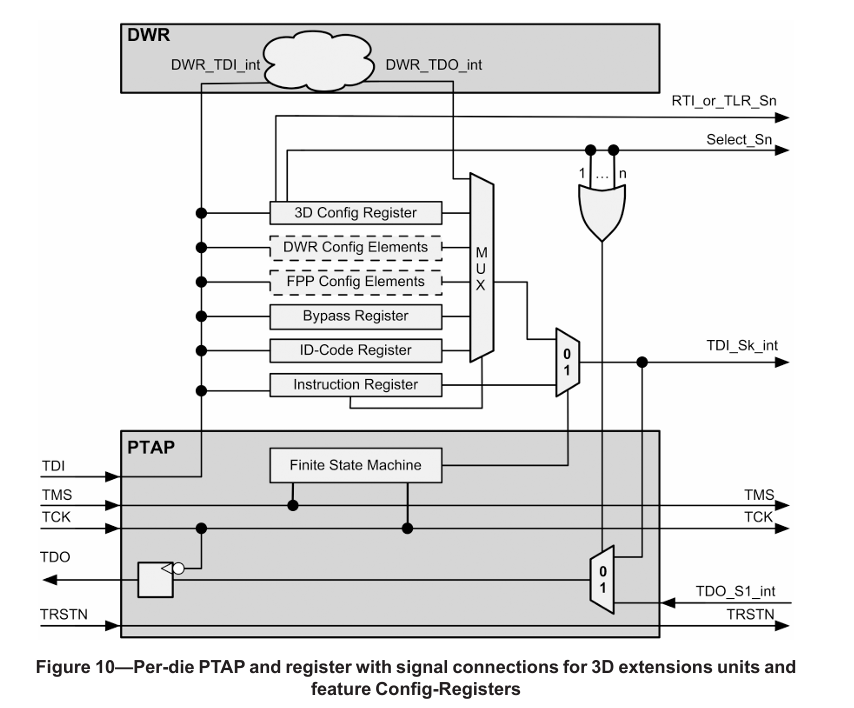

k) 如果没有STAP被选中(所有Select_Sn信号都为0),并且所有配置元素都位于PTAP控制器中,PTAP应从TDI_Sk_int源出TDO(参见图10和图11),否则PTAP应从TDO_S1_int源出TDO。(译注:也就是没有STAP被select的时候,TDI_Sk_int的数据直接送到TDO的寄存器,不考虑STAP相关的信号。)

l) 串行数据路径中的移位寄存器元素应由TCK的上升沿触发,并在除ShiftDR和ShiftIR状态外的所有状态下保持状态。

注意——移位寄存器元素由建议m)和n)以及权限o)支持。

建议如下:

m) 如果需要,应在PTAP TDI_Sk_int输出和STAP_Sk TDI_Sk_int输入之间的串行数据路径中添加额外的移位寄存器元素。

n) 如果需要,应在STAP_S1 TDO_S1_int输出和PTAP TDO_S1_int输入之间的串行数据路径中添加额外的移位寄存器元素。

权限如下:

o) 如果需要,可以在每个STAP内的串行数据路径中添加额外的移位寄存器元素。

5.4.2 Description

在上电时,STAP处于未选中状态。在选中并激活之前,每个STAP应处于一种配置状态,使其关联的下一个芯片的PTAP控制器保持在空闲状态,从而不处理任何捕获、移位或更新操作。默认的停放状态是Test-Logic-Reset (TLR)状态;然而,STAP配置寄存器(3DCR)允许选择Run-Test-Idle (RTI)状态。

要激活一个STAP,需要访问关联的STAP的3DCR段。然后可以配置3DCR位,并在PTAP控制器处于Update-DR状态时,在TCK的下降沿(译注:根据TAP,UpdateDR在下降沿改变)断言其新配置。停用需要类似的操作。

在STAP控制逻辑块内,沿每个STAP的串行扫描路径需要寄存。用负边沿TCK寄存器将串行数据呈现给TDO_Sn,用正边沿的TCK寄存器,采样从芯片外呈现给TDI_Sn端子的串行数据。这些仅用于调整(重新同步)数据位的移位寄存器用于扫描数据路径,以帮助确保移位数据的完整性得以保持。

任何STAP都可以处于活动状态并包含在活动扫描路径中;或者可以被取消选择并绕过,不成为活动扫描路径的一部分。

当STAP被选中为活动状态时,其控制端子的行为应遵循PTAP的端口操作,并与PTAP的操作同步。然而,当未被选中时,每个STAP可以配置为使关联的下一个芯片的PTAP保持在停放状态:Run-Test-Idle (RTI) 或 Test-Logic-Reset (TLR) 。所选的停放状态取决于STAP配置寄存器中该编号STAP的RTI_or_TLR_Sn配置位的状态。通过管理TMS信号从当前芯片的PTAP接口传递到同一芯片的STAP接口来实现选择和停放要求(参见图9中的示例)。

当STAP被选中时,PTAP的TMS信号未经修改或寄存直接传递到STAP的TMS_Sn。当STAP未被选中时,TMS_Sn应驱动为逻辑0,以使关联的下一个芯片的TAP FSM保持在停放的Run-Test-Idle (RTI)状态,或者如果希望关联的下一个芯片的TAP FSM的停放状态为Test-Logic-Reset (TLR),则驱动为逻辑1。注意,选择(取消停放)一个STAP需要遵循以下协议序列:取消停放要求直接从UpdateDR状态退出到RTI状态。

STAP相对于彼此的物理位置可能会导致较大的物理分离,以至于与各个TDI_Sn和TDO_Sn连接相关的实际端子可能通过长线路径连接。由于这些可能对移位数据时序产生影响,正时序调整寄存器不应仅限于从连接芯片返回的次级TDI_Sn端口,而应存在于次级串行测试访问端口之间的主扫描路径中。图9展示了一种优选配置,其中时序调整寄存器无论次级串行测试访问端口是否被选中,都保持在活动扫描路径中。

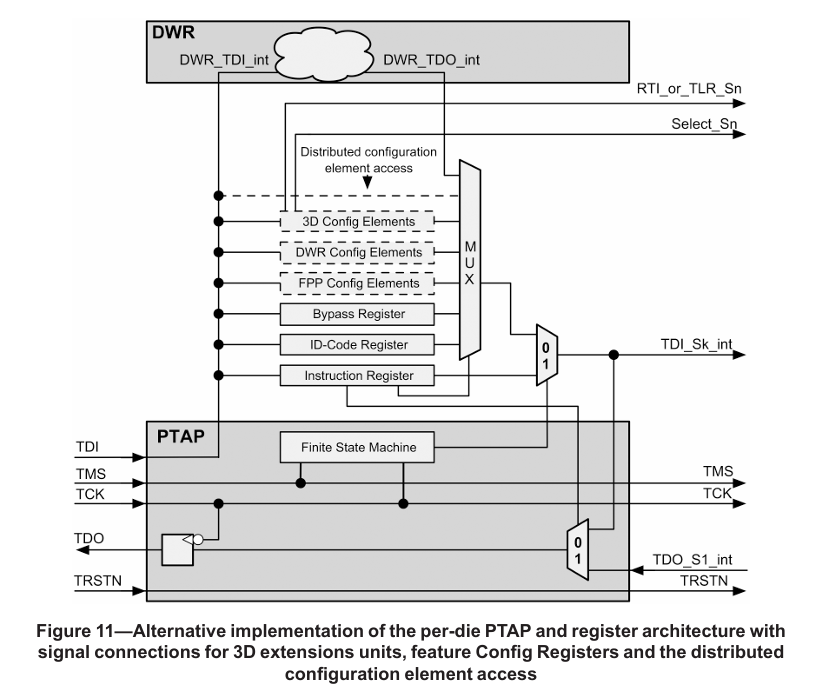

STAP应从芯片内的IEEE Std 1838 PTAP控制器和寄存器架构中进行选择和配置,并且PTAP控制器应保持在活动串行扫描路径中,要求扫描路径到STAP TDO信号(TDO_S1_int)的源必须放置在PTAP寄存器架构的寄存器架构之后(参见图11中为TDI_Sk_int提供源的mux的输出)。

如果使用图10中的Select3DCR指令访问3DCR,则难以保持IEEE 1149.1的合规性。(译注:没看懂?)例如,BYPASS指令数据路径将包括旁路寄存器和STAP寄存,即使在未选择任何STAP时也是如此。因此,在电源上电或TRSTN引脚置位时,启用了一条短路径。这条短路径简单地绕过了STAP路径。这条快捷路径在用户决定启用STAP路径之前一直启用。因此,其他指令(例如,除了BYPASS之外的指令)也将启用这条短路径。实际上,在用户启用STAP之前,堆栈将实际上类似于符合IEEE 1149.1的芯片。一旦并且只要启用了STAP,就不再使用短路径,并且STAP寄存将添加到串行数据路径中。图10显示了通过OR门解 码Select_Sn信号,在未选择任何STAP时选择堆栈旁路路径。(译注:图10和图11的区别在于,用来实现规则k的2选1MUX的选择信号从哪里来。所以应该从哪里来?)

还应注意的是,一些芯片可能被定位为堆栈的最后一个或终止芯片,因此不需要次级接口——出于这个原因,STAP的支持被指定为可选的。要求是次级接口可能支持0到n个STAP。

5.5 Registers

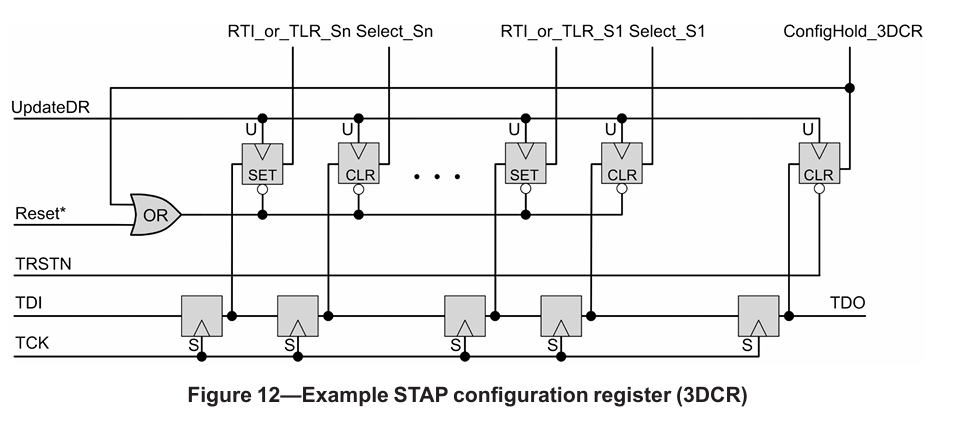

5.5.1 Secondary test access port configuration register (3DCR)

5.5.1.1 Specifications

3DCR是三个信号的来源:

— 3DCR Config-Hold signal(强制的),该信号复位为逻辑0,使3DCR输出的信号在PTAP控制器的状态机为Test-Logic-Reset时复位;

— Select_Sn信号,该信号复位为逻辑0,选择并激活某个STAP_Sn;

— RTI_or_TLR_Sn停放状态定义信号,该信号复位为逻辑1状态(对应于TLR状态),定义TMS_Sn信号的停放状态。

所有这些信号都由3DCR中更新位的独热编码(逻辑1等于断言)生成,这些更新位与3DCR中的移位位一一对应,并具有从LSB到MSB的指定顺序。这些信号的置0/1的操作在PTAP控制器的Update DR状态中在TCK的下降沿发生。

规则如下:

a) 任何包含一个或多个STAP的芯片应有一个3DCR。

b) 3DCR应按照IEEE Std 1149.1-2013第9条中描述的捕获更新测试数据寄存器(TDR)进行设计。

c) 每个3DCR移位寄存器元素应有一个关联的update元素。

d) 3DCR寄存器输出(由更新元素驱动)应在更新DR状态中在TCK的下降沿改变。

e) 3DCR应从芯片内的IEEE 1838 PTAP控制器和寄存器架构中进行选择和配置。

f) 3DCR应为每个STAP有一个选择位(即Select_Sn)。

g) 3DCR应为每个STAP有一个TMS保持位(即RTI_or_TLR_Sn)。

h) 在电源上电复位(POR)后,或在TRSTN被断言时,或在持久性禁用时进入TLR状态后,所有STAP应被取消选择,RTI_or_TLR_Sn信号配置为驱动逻辑1。

i) 在电源上电复位(POR)后,或在TRSTN被断言时,或在持久性禁用时进入TLR状态后,所有STAP应被取消选择,Select_Sn信号配置为驱动逻辑0。

j) 3DCR选择配置位(Select_Sn)应以逻辑1值断言。

k) 设置STAP_Sn的RTI_or_TLR_Sn位为逻辑0应在STAP_Sn未被选中时驱动STAP_Sn端子TMS_Sn为逻辑0。

l) 设置STAP_Sn的RTI_or_TLR_Sn位为逻辑1应在STAP_Sn未被选中时驱动STAP_Sn端子TMS_Sn为逻辑1。

m) 3DCR应为每个STAP有一个Config-Hold_Sn。

n) 每个3DCR Config-Hold信号应在电源上电时处于未断言状态(即“不保持”配置)。

o) 每个3DCR Config-Hold信号应在TRSTN为1时复位为0。

p) 当3DCR Config-Hold信号为0,其关联的STAP逻辑和3DCR寄存器位应在PTAP控制器进入Test-Logic-Reset状态时复位。

q) 当3DCR Config-Hold信号为1时,其关联的STAP逻辑和3DCR寄存器位在PTAP控制器进入Test-Logic-Reset状态时不应改变状态。(译注:因此reset和ConfigHold_3DCR是OR的关系,当reset和ConfigHold_3DCR同时为0时才对寄存器进行复位)

r) 当3DCR不是扫描路径中选定的活动数据寄存器时,3DCR应保持其状态。

建议如下:

s) 每个3DCR位的捕获扫描寄存器应在捕获DR状态中捕获关联更新元素的更新寄存器的值。

权限如下:

t) 3DCR配置元素可以与其他任何寄存器串联。

u) 一个芯片可以有多个3DCR段,每个段有一个单独的配置保持位。

5.5.1.2 Description

STAP 3D配置寄存器(3DCR)是一个由放置在PTAP控制器指令寄存器或串行可访问元素中的指令编码选择的寄存器。如果芯片上没有STAP,则不需要3DCR——因此,它是一个依赖选项,仅在芯片至少有一个STAP时才强制要求。最后一个芯片不需要STAP,因此可能没有3DCR。

STAP 3DCR提供了一种选择和配置方法,将与主接口关联的TAP信号传播到次级接口,供堆栈中的下一个芯片使用。此功能代表了数据和控制在上下以及与下一个芯片之间传递的过程。3DCR可以实现为多个寄存器段,例如在芯片有多个塔的情况下。

在本标准的其余部分中,3DCR用于指代配置和保持位集体,即使它们被实现为多个寄存器段。

3DCR应具有复位持久配置(Config-Hold),允许PTAP控制器通过Test-Logic-Reset(TLR)状态而不影响测试功能(译注:当ConfigHold_3DCR信号为1时,即使Reset信号为0,3DCR相关的寄存器也不会被复位)。TRSTN应复位3DCR。定义了特定规则以启用Config-Hold功能。

图12展示了一个符合标准的3DCR示例。STAP配置寄存器的命令位在配置寄存器中从持久性命令位ConfigHold_3DCR开始组织,位于扫描输出端(LSB)。

选择信号:选择位Select_Sn和保持状态位RTI_or_TLR_Sn可以放置在寄存器的其他任何位置。

3DCR是一个数据持久寄存器,当3DCR不是扫描路径中选定的活动数据寄存器时,它将保持其状态。当ConfigHold_3DCR位为1时,3DCR也变为“复位持久”,即持有Select_Sn、RTI_or_TLR_Sn和ConfigHold_3DCR值的更新位在PTAP控制器FSM通过TLR状态时不会恢复到复位状态。TRSTN为1将修改所有3DCR寄存器值,将它们进行复位。

5.5.2 Die wrapper register (DWR)

本标准中需要DWR(Data Write Register,数据写入寄存器),并使逻辑在INTEST和EXTEST模式下对芯片端子的可控性和可观测性成为可能。DWR有多种模式,也可能有多种配置。DWR的规则、建议和权限在第6条中描述。DWR的模式控制和配置使用IEEE Std 1838指令和/或PDL、ICL等语言的描述以及支持硬件如SIB来完成。

5.5.2.1 Specifications

规则如下:

a) 每个芯片应有一个DWR。

注意——DWR在第6条中进一步定义。

5.5.2.2 Description

DWR可以使用不同的结构构建。例如,它可能仅在芯片边界使用IEEE 1838 DWR单元。它可能重用IEEE 1500 WBR的一个或多个段作为DWR的一部分。它可能重用IEEE 1149.1 BSR作为DWR的一部分。它可能在路径中包含SIB以实现本地配置能力。

5.5.3 Flexible parallel port configuration register

IEEE 1149.1二维架构的另一个扩展是添加了灵活并行端口及其相关的灵活并行端口配置元素,这些元素用于选择和配置灵活并行端口。这将在第7条中进一步讨论和定义。

5.5.4 ECID register

5.5.4.1 Specifications

规则如下:

a) 如果按照建议5.2.1实现StackID,则还应实现ECID寄存器及其关联的ECIDCODE指令,如IEEE Std 1149.1-2013第13条和第8.15条所述。

b) 如果包含芯片位置寄存器字段[参见5.5.4.1建议d)],则ECID中应有一个称为StackID的字段。

c) StackID值不应全为1。

建议如下:

d) 应有一个称为StackID的字段,用于描述芯片在堆栈中的位置,通过ECID寄存器及其关联的ECIDCODE指令访问,如IEEE Std 1149.1-2013第13条和第8.15条所述。

注意1——StackID应编程为唯一值,以帮助识别堆栈中的每个芯片。

注意2——应充分考虑此字段的宽度,以容纳堆栈中芯片任何潜在位置的唯一值。

5.5.4.2 描述

StackID编号系统由用户定义。芯片StackID值与实际芯片之间的关联应由堆栈生产者和/或用户维护。芯片提供者应使他们的StackID字段足够宽,以在堆栈中的芯片数量在单个芯片制造时未知的情况下,处理堆栈中芯片集合中的唯一值。