一、故事前传

之前我们讲了对PCIe的一些基础概念作了一个宏观的介绍,了解了PCIe是一种封装分层协议(packet-based layered protocol),主要包括事务层(Transaction layer), 数据链路层(Data link layer)和物理层(Physical layer)。

较为详细解释请见之前的文章:

1. PCIe技术概述;

2.0 PCIe Transaction layer事务层概述;

2.1~2.3 TLP结构及原理解析;

2.4~2.6 Flow control机制重点部分解析;

二、Flow Control的实现过程

前面针对Flow control的基本原理与组成进行了解析了,那么如何实现flow control这个功能呢?

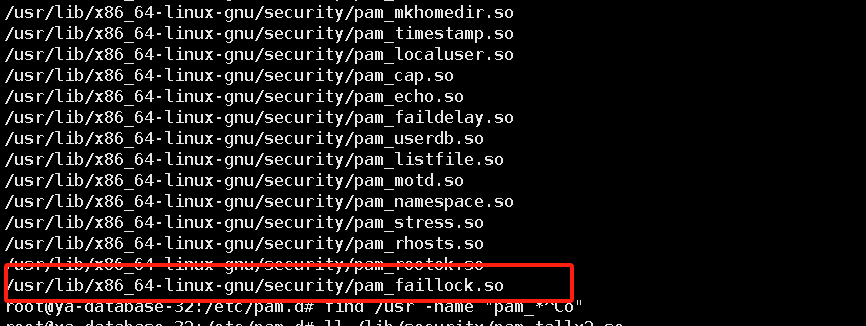

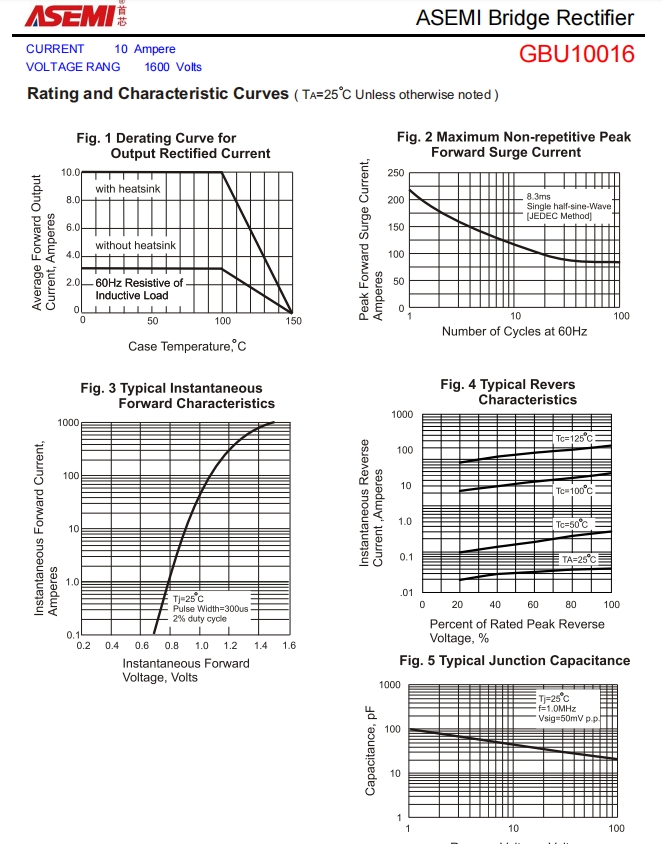

要实现flow control功能,我们需要了解Flow control的控制逻辑单元。在之前的文章介绍中,我们了解了VC buffer有六个部分,每部分对应的Flow控制逻辑单元是一样的,所以,在这里,我们仅以Non-Posted Request Header对应的Flow control控制逻辑单元为例,如下图:

从上图中,我们可以看到Flow control控制逻辑单元主要包括:

发送端:

Transaction Pending Buffer:发送端用于存放正在等待在同一虚拟通道(VC)传输的TLPs.

Credits Consumed Counter:在发送端在VC buffer中所有TLPs的信用单元总和,简称“CC”.

Credit Limit Counter:这部分由接收端的VC buffer的大小决定,简称“CL”。接收端会在TLPs 传输的过程中不断发送FC DLLPs来更新CL的大小.

Flow Control Gating Logic:这个逻辑单元主要根据CC,CL以及待发送的TLPs的数量来判断接收端是否有足够的空间接收下一个TLPs. 判断公式如下:

{CL-(CC+PTLP)} mod 2^[Field Size] <= 2^[Field Size]/2

注释: Header Field Size=8, Data Field Size=12.

PTLP= Pending TLP,待发送TLP.

接收端:

Flow Control Buffer:存储传进来的Data和Header数据.

Credits Allocated:接送端VC buffer已经分配的存储空间记录.

Credit Received Counter:这部分主要记录接收端接收的所有TLPs对应的信用单位总和。

我们看一个例子看一下Flow control具体过程:

1. 初始状态下 Flow control控制逻辑单元:

在这里例子中,我们假设VC buffer大小为2KB,之前的文章介绍过Non-Posted Header的信用大小为5DW,也就是20Bytes, 所以Flow control单元数目最大为2KB/20Bytes=102d=66h.

初始状态下:CC=00h, CL=66h, CrRcv=00h, CrAl=66h,

2. 传输一个TLP之后的Flow Control控制逻辑单元:

此时,CC=01h,CrRcv=01h,

3. VC buffer出于满的状态时的Flow Control控制逻辑单元:

发送端: CC=CL=66h, CR=CC+PTLP=66h+01h=67h,

CL-CR=66h-67h=66h+99h=FFh不满足判断公式.

接收端: CrRcv=CrAl=66h,

此时,说明了VC buffer已经满了,暂停传输TLPs.

4. VC buffer清空部分数据的Flow Control控制逻辑单元:

接收端VC buffer清空了3个Non-Posted Header数据,此时VC buffer有了新的可用空间,可以继续接受TLPs. 但此时发送端并不知道,怎么办呢?

放大招!!!

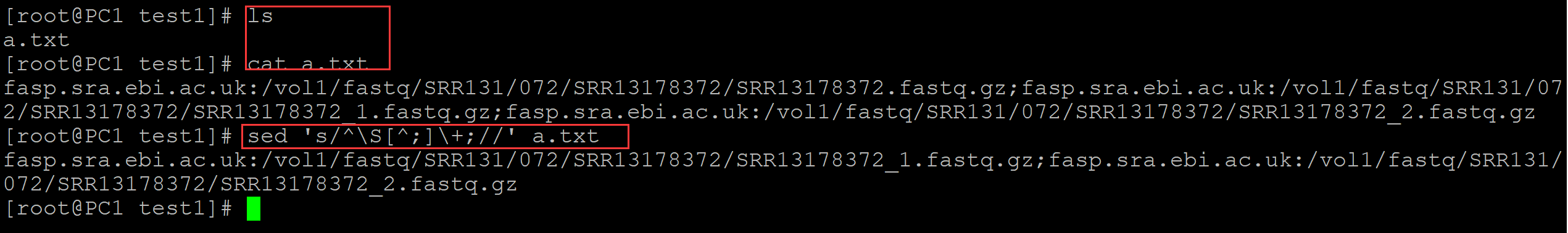

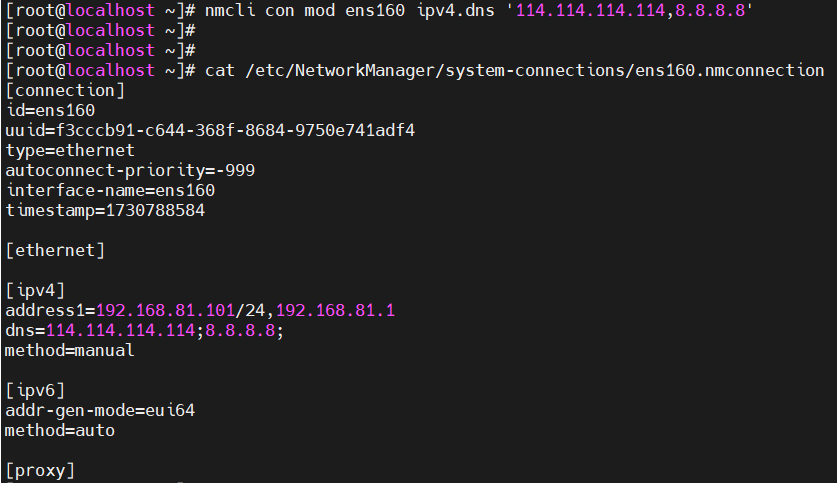

PCIe协议中有定义一个Flow Control update packets, 也即Flow Control update DLLPs.格式如下图,

有了大招就好办了,接受端通过发送Flow control update DLLPs告知发送端:“我这边腾出地方了,可以传TLPs过来咯!”

同时,CL更新为69h, CC=66h, CR=66h+01h=67h,

CL-CR=69h-67h=02h<128, 满足判断公式,TLPs可以继续传输。