AER

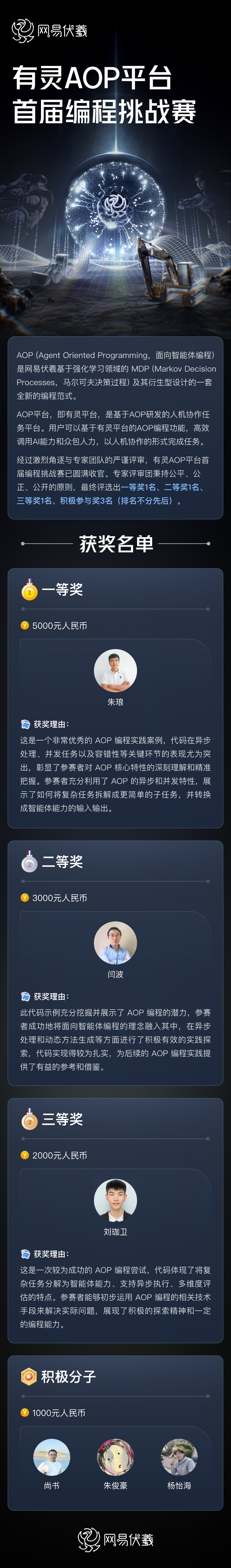

AER(Advanced Error Reporting)是一种用于检测和报告PCIe设备中发生的错误的机制,它允许PCIe设备检测到并报告各种类型的错误。错误类型包含Correctable Errors 和Uncorrectable errors两种,其中Uncorrectable errors下面又分为ERR_FATAL和ERR_NONFATAL。

- Correctable Errors:可纠正错误是指错误发生后,硬件可以自动恢复,不影响正常业务。

- Uncorrectable errors:错误发生后,影响设备功能,硬件不能自动恢复

- ERR_FATAL:致命错误,此错误类型影响了PCIe link链路,为了防止错误扩散,通常会由错误设备的上游桥对错误设备进行复位操作

- ERR_NONFATAL:指影响了设备功能,但是PCIe link还是稳定的

AER功能启动条件:

- 对于EP设备和RC都应该启动Command Register寄存器中SERR#Enable;

- 对于EP设备,需要将AER中不可纠正错误掩码和可纠正错误掩码清空;

- 对于EP设备,需要将Device Control Register寄存器中Correctable Error Reporting Enable、Non-Fatal Error Reporting Enable、Fatal Error Reporting Enable、Unsupported Request Reporting Enable功能打开;

- 对于RC,需要将AER Root Error Command Register寄存器中Correctable Error Reporting Enable、Non-Fatal Error Reporting Enable、Fatal Error Reporting Enable功能打开

AER相关寄存器

当Uncorrectable Error Status Register寄存器对应Bit为1时,Uncorrectable Error Severity Register寄存器对应Bit为1表示ERR_FATAL,为0表示ERR_NONFATAL。

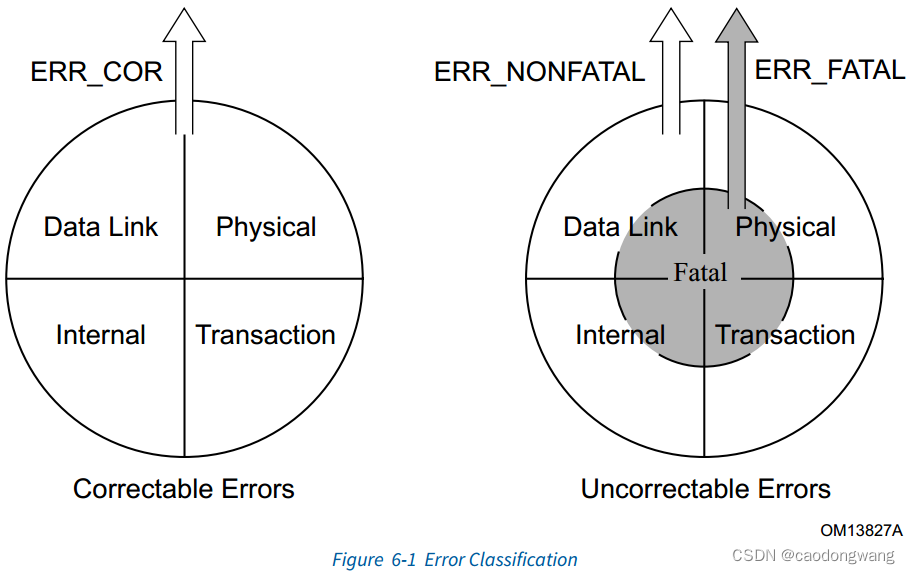

Advanced Error Reporting Extended Capability Header (Offset 00h)

| Bit Location | Register Description |

|---|---|

| 15:0 | PCI Express Extended Capability ID,PCIe扩展Cap的ID,对于AER功能,其ID为0x0001. |

| 19:16 | Capability Version,对于支持End-End TLP Prefix的设备,这个必须为2,其他设备可填1或2. |

| 31:20 | Next Capability Offset,下一个Cap的偏移地址。 |

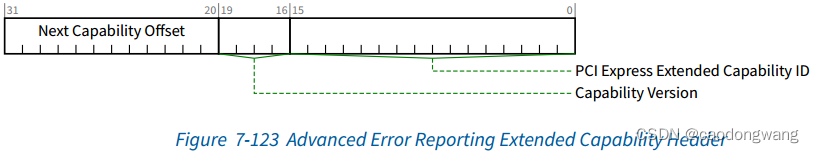

Uncorrectable Error Status Register (Offset 04h)

不可纠正错误状态寄存器表示PCI Express设备上单个错误的错误检测状态。该寄存器不同Bit置1表示检测到特定错误,软件可以通过向相应的位写入1b来清除错误状态,寄存器含义如下:

[0] Undefined

Undefined-从该位读取的值是未定义的。

[3:1] Reserve

[4] Data Link Protocol Error Status

可能原因:发送端数据链路层收到了预期之外的ACK或NAK。

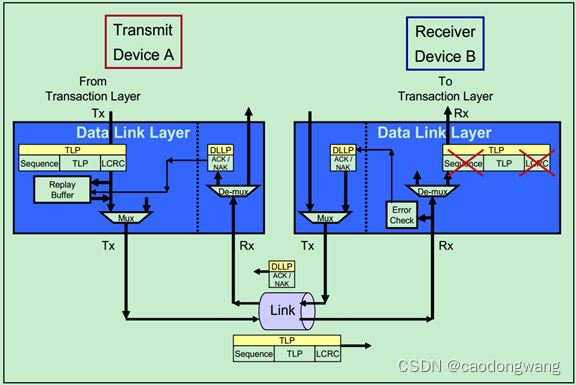

数据链路层在发送TLP之前,发送端会将TLP封装,加上Sequence前缀和LCRC后缀,用于保障数据链路层两端报文完整性,如下图所示。

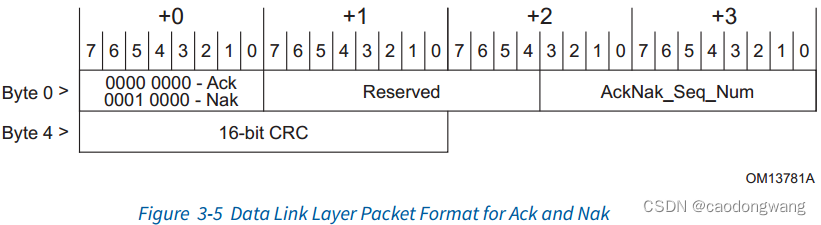

假设上电协商之后发送端只发送了Sequence=1的一个报文,那么发送端就预期接收Sequence=1的ACK或NAK。接收端接收到这个报文之后,应该回复一个ACK或NAK报文(假设不聚合),这个回复的报文中Sequence也必须为1。ACK/NAK的报文格式如下。

当接收端接收到的ACK或NCK的Sequence不等于1,那么将产生Data Link Protocol Error,如果Data Link Protocol Error Status位对应的mask不为1,则将Data Link Protocol Error Status位置1,并上报错误。

数据链路层更详细的交互流程可参考网址或查看PCIe体系结构导读第7.2章节。

[5] Surprise Down Error Status (Optional)

该状态为可选,如果硬件不支持,则应硬连接至0。

由link up状态在L0期间突然被置位,表示物理链路层意外断开。这个功能一般是桥设备支持的功能,也就是说,桥下面的EP意外链路断开时,桥设备可以将该Bit置1,并上报给系统软件。设备未插好、暴力热插拔都可能产生该错误。

当桥设备Slot Capabilities Register的Hot-Plug Surprise bit置1时(表示支持热插拔),桥设备将不会上报这个错误。

[11:6] Reserve

[12] Poisoned TLP Received Status

在TLP报文中,有一个EP Bit表示这个报文是否为Poisoned TLP,当该Bit为1时,表示这个报文携带的Date已经不可靠,注意,这个EP只是表征报文携带的数据不可靠了,与报文的Header无关。

[13] Flow Control Protocol Error Status (Optional)

接收端一段时间未收到更新Credit的报文或更新Credit超过限制。

[14] Completion Timeout Status

一个经常碰到的错误。请求端发出的Non-post请求(cfg read与memory read)在规定时间内未收到完成报文。可通过修改请求端的Device Capabilities 2 Register 寄存器来调整超时时间。

[15] Completer Abort Status (Optional)

响应者接收到请求,因为某些原因无法正确响应这个请求,将回复Completer Abort报文给请求者,并将Completer Abort Status置1。

可能出现错误的原因:

- 设备接收的请求,违反了设备的某些规则,比如读BAR空间长度超出能力;

- 设备已经处于某种错误状态,无法正确响应请求;

- 设备接收到存在访问控制服务错误(Access Control Services Error)的请求;

- PCIe-to-PCI桥接收到针对其连接的PCI设备的请求,但是该PCI设备无法处理该请求,则PCIe-to-PCI桥回复Completer Abort报文给请求者。

[16] Unexpected Completion Status

当请求者收到非预期的完成报文,将上报该错误。

可能原因:

- 请求者接收到的完成报文中的Request ID与请求者BDF不一致;

- 请求者接收到的完成报文中的Comleter ID与所有Outstanding请求中的Request ID不一致;

- 请求者接收到的完成报文,检查其中Tag,发现并无对应的Outstanding请求。

[17] Receiver Overflow Status (Optional)

接收端收到的TLP多于可用的接收缓冲空间。出现这种问题,要么是FC有问题,要么就是接收端发送的request由问题。

[18] Malformed TLP Status

接受者接收到了畸形报文,则上报该错误。

可能原因:

- 设备接收到Message报文,检查发现流量类型不是TC 0;

- 设备接收到TLP中TD位是1,但TLP又不带ECRC,或TLP中TD位是0,但TLP又带ECRC;

- 设备接收到Completer报文,但报文携带数据长度超过设备协商的MPS(Max Payload Size);

- 设备接收到TLP数据长度(Data Length)与包头中的长度值不一致;

- 设备接收到TLP发现违反了RCB对齐要求;

- 设备接收到Completer报文,发现其完成状态是CRS(Configuration Request Retry Status),但该Completer报文对应的请求不是配置请求;

- 设备接收TLP其TC域包含了一个未被分配到当前使能的VC的值;

- 设备接收TLP,发现报文中字节使能冲突,比如读2个DW数据的请求,其Last DW BE为0;

- RC收到Downstream Ports发送的Assert_INTx/Deassert_INTx Messages。

[19] ECRC Error Status (Optional)

设备接收TLP报文,ECRC校验错误,这也就意味着LCRC校验是成功的,大概率是报文通过pcie switch时,数据出现了问题。

[20] Unsupported Request Error Status

收到的报文不属于任何一种协议规定的DLLP或TLP类型,或者报文的域段非法或越界(如MEM WRITE访问越界)等。注意,只要是会返回Comleter报文的请求,就不会上报Unsupported Request Error,而是通过Comleter报文来指示,比如,cfg报文访问设备未实现的function。

[21] ACS Violation Status (Optional)

接收的posted或non-posted请求中,存在访问控制错误。

[22] Uncorrectable Internal Error Status (Optional)

PCIe IP内部出现错误,可能情况很多,比如IP后端模块给IP反压导致丢包。

[23] MC Blocked TLP Status (Optional)

笔者对其不了解。

[24] AtomicOp Egress Blocked Status (Optional)

如果Port口将AmicOp Egress Blocking使能,则在其收到待转发的AtomicOp Request请求时,将提前结束这个请求,并给请求者回复UR completion。

[25] TLP Prefix Blocked Error Status (Optional)

如果Port口将End-End TLP Prefix Blocking使能,则在其收到带Prefix的TLP时,将提前结束这个请求,并给请求者回复UR completion(如果是Non-post的话)。

[26] Poisoned TLP Egress Blocked Status (Optional)

如果Port口将Poisoned TLP Egress Blocking使能,则在其收到待转发的poisoned TLP时,将上报Poisoned TLP Egress Blocked error。

[31:27] Reserve

Uncorrectable Error Mask Register (Offset 08h)

不可恢复错误掩码寄存器,与状态寄存器一一对应,当对应Bit为1时,表示不检测也不上报对应错误。

默认情况下,22 Bit(Uncorrectable Internal Error Mask )和26 Bit(Poisoned TLP Egress Blocked Mask)复位值为1。

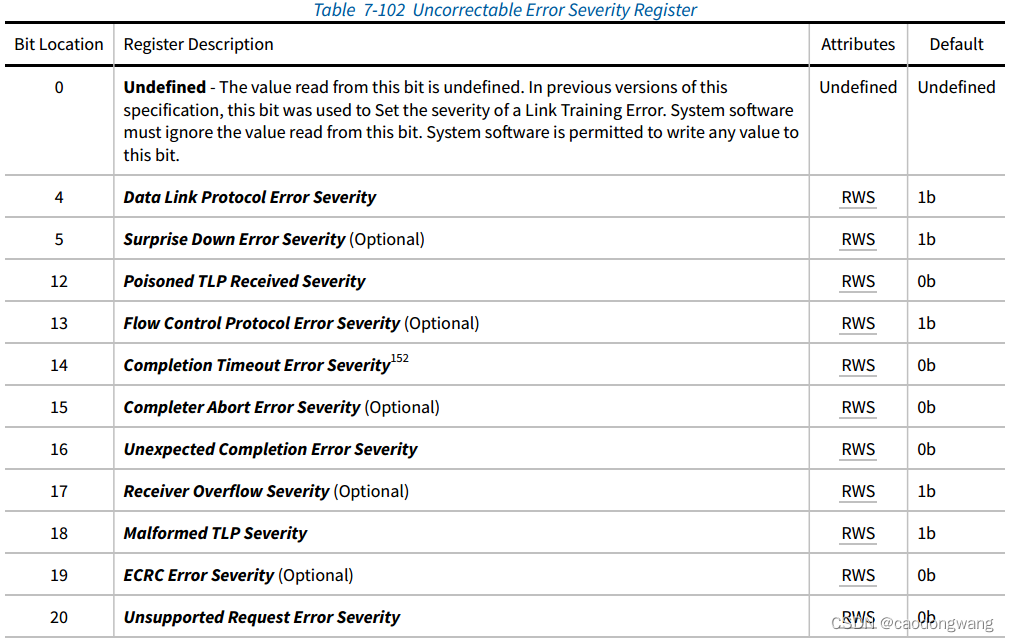

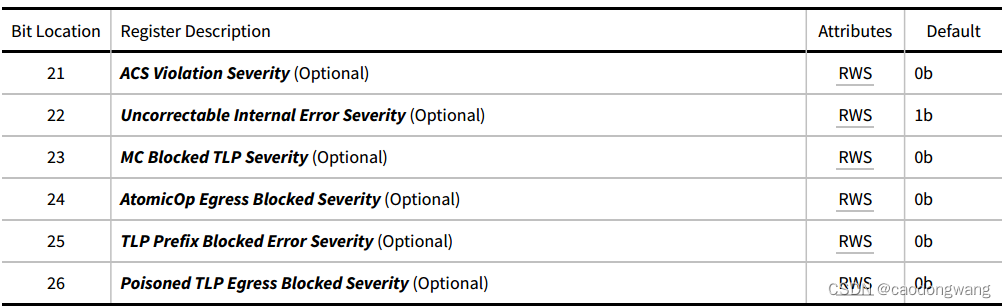

Uncorrectable Error Severity Register (Offset 0Ch)

不可恢复错误严重程度寄存器,当不可恢复错误状态寄存器某个Bit为1时,不可恢复错误严重程度寄存器对应Bit为1,则表示致命错误(ERR_FATAL),为0则表示非致命错误(ERR_NONFATAL)。

注意,上面默认为1表示部分错误只要上报,必然为致命错误。

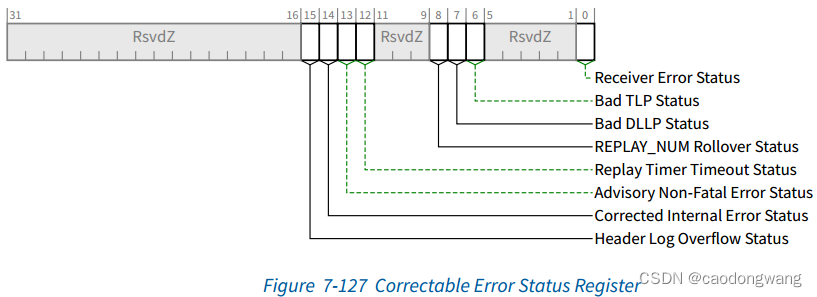

Correctable Error Status Register (Offset 10h)

可恢复错误状态寄存器,表示硬件发生了可恢复错误,由硬件自行纠正之后上报错误状态,注意,一般来说,可纠正错误不会影响正常业务。

[0] Receiver Error Status

Link errors都可以认为是receiver error,可能原因:

- 可能是协商过程中出现误码;

- 可能是由于lane处于L0时的MAC错误;

- 错误lane中接收到Control控制符号;

- 链路可能从L0跳转到Recovery状态的信号完整性问题造成。

[5:1] Reserve

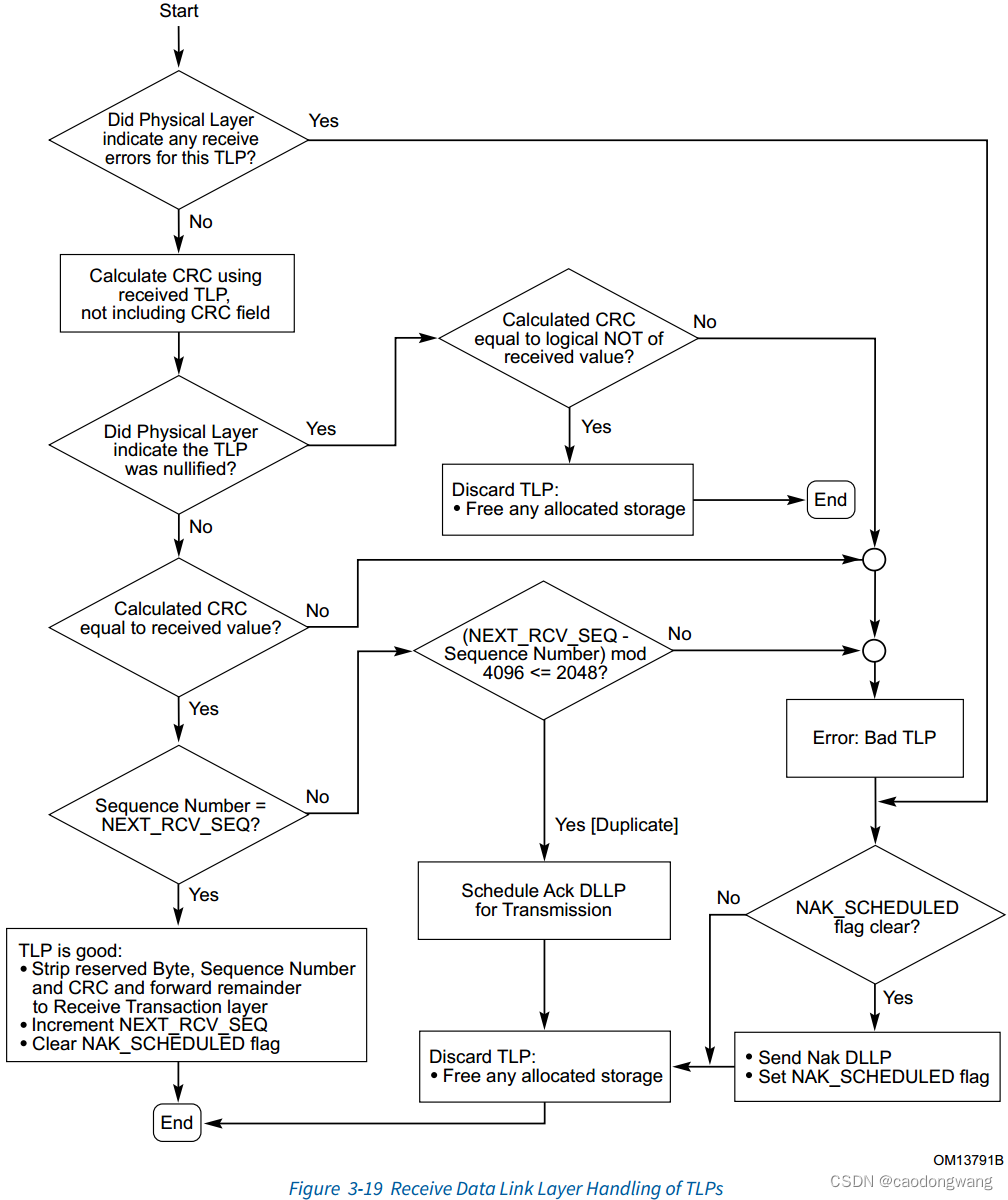

[6] Bad TLP Status

先来看一张TLP处理流程图:

从上面可以知道导致Bad TLP错误的有三种可能:

- 接收出错(Rx Err);

- 数据链路层CRC校验出错(LCRC);

- 数据链路层接收的报文序列号与预期序列号不一致(Sequence Number)。

[7] Bad DLLP Status

DLLP报文计算CRC出错。

[8] REPLAY_NUM Rollover Status

TLP因为某些原因重传,当重传次数超过四次则上报REPLAY_NUM Rollover错误。注意,一旦设备上报这个错误,链路会进入recovery重新训练。

[11:9] Reserve

[12] Replay Timer Timeout Status

发送端每发送一个TLP报文都会有启动一个定时器,在规定时间内未接收到正确的ACK/NAK,则上报Replay Timer Timeout错误。

[13] Advisory Non-Fatal Error Status

在某些情况下,非致命错误的检测器不确定错误是否可恢复,或者是否需要任何恢复动作。例如,如果RC尝试配置请求访问设备未实现的function,则完成报文中的UR状态可以告知向RC错误信息,而不需要设备ERR_NONFATAL消息告知RC,因此,设备将AER中的Advisory Non-Fatal Error Status置起和device status中的Unsupported Request置起,但又不会置位AER中的Unsupported Request Error Status。

[14] Corrected Internal Error Status

可能是由于内部Hard IP RAM中的ECC错误。

[15] Header Log Overflow Status

设备接收到错误报文,会将报文head记录在AER的Header Log字段中,当记满之后再来错误TLP,则上报Header Log Overflow错误。

[31:16] Reserve

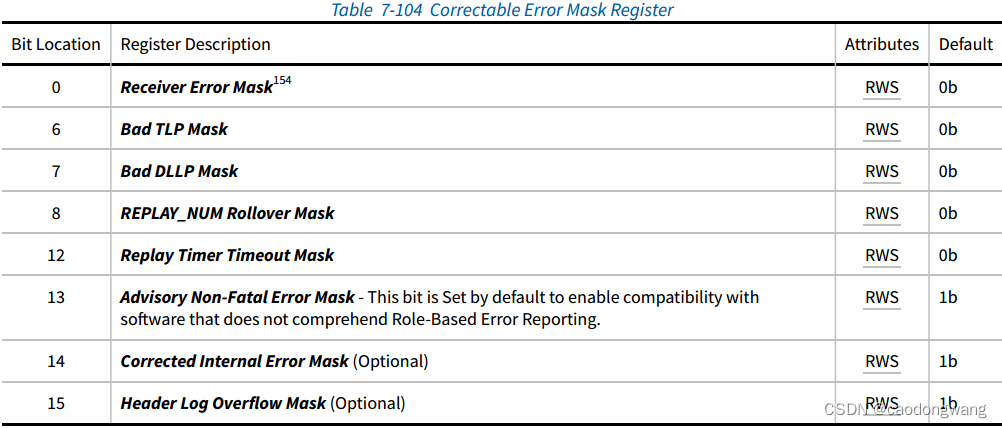

Correctable Error Mask Register (Offset 14h)

可纠正错误掩码寄存器,注意,默认有3种错误上报不开启。

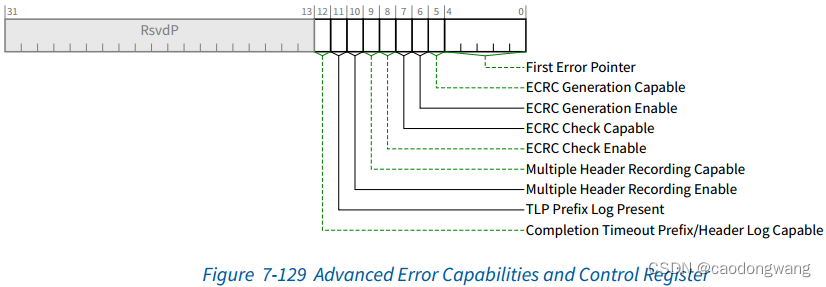

Advanced Error Capabilities and Control Register (Offset 18h)

| Bit | 描述 | 权限 |

|---|---|---|

| 4:0 | First Error Pointer,第一个不可恢复错误的位置(lspci中十六进制显示),当PCIe设备出现错误时,往往不止一个错误,找到第一个错误类型可通过该字段 | ROS |

| 5 | ECRC Generation Capable,表示function能否支持产生ECRC | RO |

| 6 | ECRC Generation Enable,当function支持产生ECRC时,可通过该Bit控制function开启ECRC功能 | RWS |

| 7 | ECRC Check Capable,表示function能否支持校验ECRC | RO |

| 8 | ECRC Check Enable,当function支持校验ECRC时,可通过该Bit控制function开启ECRC校验功能 | RWS |

| 9 | Multiple Header Recording Capable,表示function支持多个错误head报文记录能力,当出现报文错误时,按照错误顺序依次记录多个TLP head。该寄存器与First Error Pointer联动,比如First Error Pointer指示了某个错误,并且是错误TLP导致的,那么Header Log就记录着这个错误TLP head,当清除First Error Pointer对应的错误时(对应Bit写1),First Error Pointer将指向下一个错误类型,并且Header Log与之联动,若错误并非TLP导致,则Header Log为无效值。 | RO |

| 10 | Multiple Header Recording Enable,使能多错误报文head记录能力 | RWS |

| 11 | TLP Prefix Log Present,表示function支持End to End TLP Prefix error记录能力,错误TLP head记录在AER中TLP Prefix Log Register中 | ROS |

| 12 | Completion Timeout Prefix/Header Log Capable,该Bit为1表示function记录了一笔完成超时TLP的head,即该function发出请求超时未得到响应,则将该请求TLP记录 | RO |

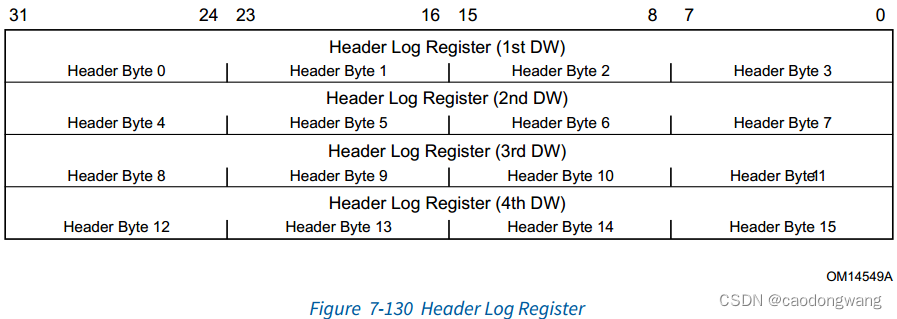

Header Log Register (Offset 1Ch)

4DW寄存器,用来存放异常TLP的head。PCIe协议要求支持AER的设备,至少支持存放一个head。

其对应格式为:

通过lspci -vvvs xxx命令可以查看设备的HeaderLog,例如:

[root@localhost ~]# lspci -vvvs 00:1c.2

00:1c.2 PCI bridge: Intel Corporation Device 7aba (rev 11) (prog-if 00 [Normal decode])...Capabilities: [100 v1] Advanced Error ReportingUESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-UESvrt: DLP+ SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr-CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+AERCap: First Error Pointer: 00, ECRCGenCap- ECRCGenEn- ECRCChkCap- ECRCChkEn-MultHdrRecCap- MultHdrRecEn- TLPPfxPres- HdrLogCap-HeaderLog: 00000000 00000000 00000000 00000000RootCmd: CERptEn+ NFERptEn+ FERptEn+RootSta: CERcvd- MultCERcvd- UERcvd- MultUERcvd-FirstFatal- NonFatalMsg- FatalMsg- IntMsg 0ErrorSrc: ERR_COR: 0000 ERR_FATAL/NONFATAL: 0000...

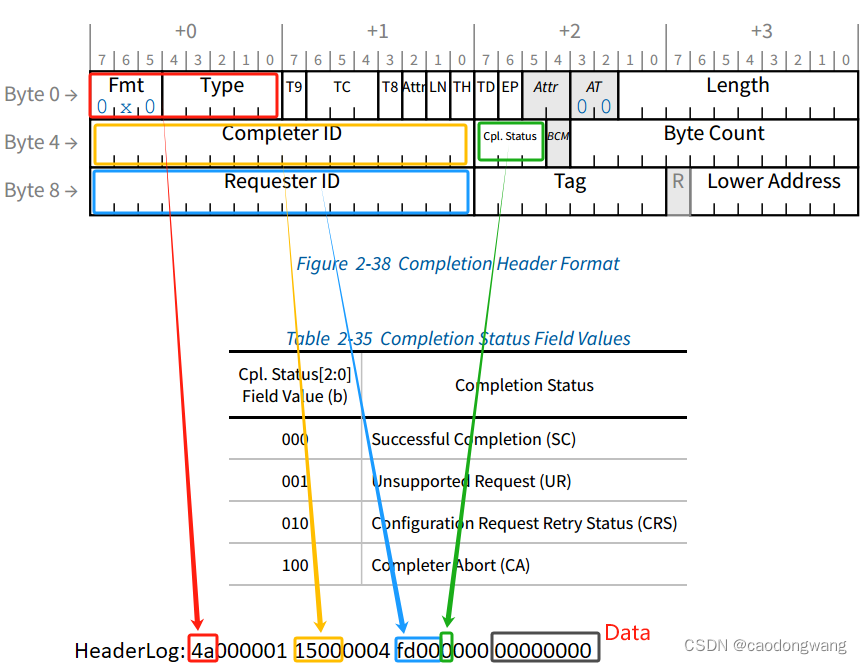

正常情况,HeaderLog中为全0,当出现异常报文时,将记录TLP的head 4DW,比如:

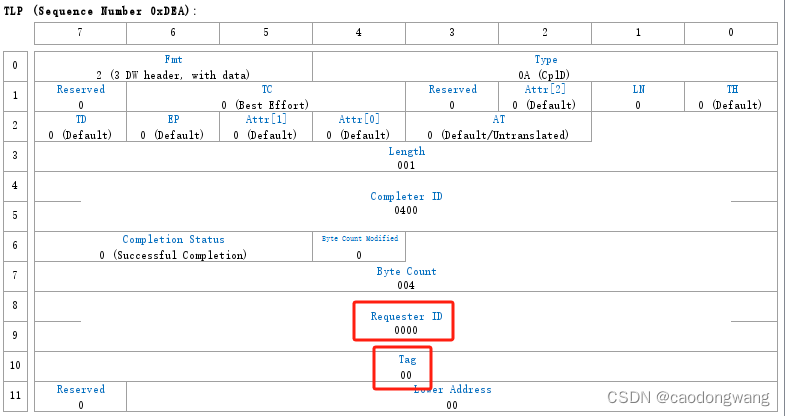

HeaderLog: 4a000001 15000004 fd000000 00000000

根据head byte0(0x4a)可以知道,异常报文是带数据的完成报文(CplD),再根据具体报文格式解析就好了,比如。

上面异常报文的错误是Request ID(0xfd00)不对,这笔报文对应的是cfg0 read请求,一般源Request ID是0x0000,回复的Request ID却是0xfd00。

报文类型可查看以下:

注:r2表示第二Bit为0或1都可,但细分报文类型不一样。

更多报文类型头部格式请查阅协议第二章节。

Root Error Command Register (Offset 2Ch)

注意,该寄存器只有RC才有效,普通PCIe设备没有该字段。

| Bit | 描述 | 权限 |

|---|---|---|

| 0 | Correctable Error Reporting Enable,可纠正错误中断上报能力使能,当该RC下游任何设备上报可纠正错误消息,都将触发中断告知系统 | RW |

| 1 | Non-Fatal Error Reporting Enable,非致命错误中断上报能力使能,当该RC下游任何设备上报非致命错误消息,都将触发中断告知系统 | RW |

| 2 | Fatal Error Reporting Enable,致命错误中断上报能力使能,当该RC下游任何设备上报致命错误消息,都将触发中断告知系统 | RW |

上电默认都是关闭的,但系统内核一般会全部打开。

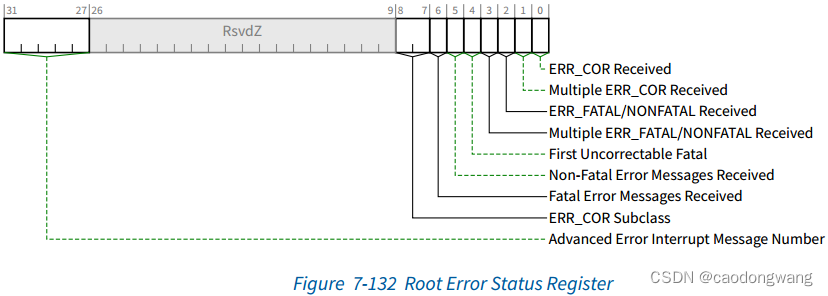

Root Error Status Register (Offset 30h)

注意,该寄存器只有RC才有效,普通PCIe设备没有该字段。

| Bit | 描述 | 权限 |

|---|---|---|

| 0 | ERR_COR Received,当Root Port收到Correctable Error Message后该Bit被置1 | RW1CS |

| 1 | Multiple ERR_COR Received,当Root Error Status Register中的ERR_COR Received Bit被置1且Root Port再次收到了Correctable Error Message,该Bit被置1 | RW1CS |

| 2 | ERR_FATAL/NONFATAL Received,当Root Port接收到Fatal或者Non-Fatal Message后且该Bit为0时,该Bit被置1 | RW1CS |

| 3 | Multiple ERR_FATAL/NONFATAL Received,当Root Error Status Register中的ERR_FATAL/NONFATAL Received Bit被置1且Root Port再次收到了Error Message,该Bit被置1 | RW1CS |

| 4 | First Uncorrectable Fatal,当Root Port收到的第一个uncorrectable error message是ERR_FATAL error则置1 | RW1CS |

| 5 | Non-Fatal Error Messages Received,当Root Port收到一个或者多个Non-Fatal Uncorrectable Error Messages后该Bit被置1 | RW1CS |

| 6 | Fatal Error Messages Received,当Root Port收到一个或者多个Fatal Uncorrectable Error Messages后该Bit被置1 | RW1CS |

| 8:7 | ERR_COR Subclass,当ERR_COR Received bit被置1,ERR_COR Subclass保存的是Root Port接收到的ERR_COR Message中ERR_COR Received 域的值 | ROS/RsvdZ |

| 31:27 | Advanced Error Interrupt Message Number,定义了Root port针对收到的error message将使用MSI/MSIX的哪个entry来产生中断。这个field由HW给出的,并且可能会随着enable MSI/MSIX entry数目的不同而变化。注意,这个值必须小于等于31,因为需要兼容MSI中断(MSI最多32个中断) | RO |

Error Source Identification Register (Offset 34h)

注意,该寄存器只有RC才有效,普通PCIe设备没有该字段。

用来保存Root Port收到的第一笔Correctable Error Message的Requester ID或Uncorrectable Fatal/Non-Fatal Error Message的Requester ID。

TLP Prefix Log Register (Offset 38h)

设备必须支持且使能了TLP Prefix能力,这个字段才有效。

这个寄存器保存了触发错误的TLP包的End-End TLP Prefix(local TLP Prefix报文错误不会记录在此),其数据排布方式与Header Log Register相同。

DPC

DPC(Downstream Port Containment)是一种用于处理PCIe链路中错误情况的机制。当PCIe链路上的一个设备发送错误信号时,DPC机制允许系统针对该错误进行处理,以避免错误的传播和影响其他设备。具体而言,DPC机制会隔离出故障设备,从而限制错误的影响范围,确保其他设备继续正常工作。注意:DPC机制依赖于AER提供的错误信息来进行错误处理。

AER和DPC通常结合使用,以提供更全面的错误处理和容错机制。当PCIe设备发生错误时,AER会检测和报告错误的详细信息,而DPC则可以根据这些错误信息采取相应的措施,例如隔离故障设备,以维护整个PCIe系统的稳定性和可靠性。通常,Downstream Port接收到下游发送的不可纠正错误消息,会将下游链路断开,防止错误扩散,如果在调试PCIe设备时碰到link断开情况并且系统未重启,则很大可能是DPC发挥的作用。

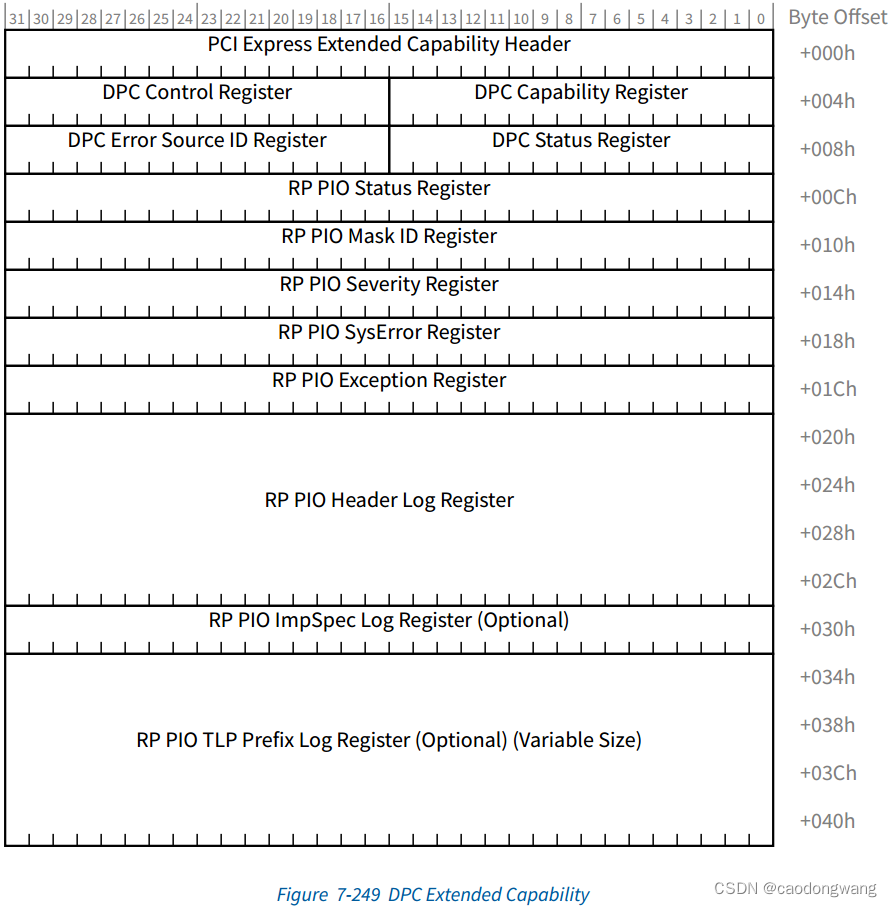

相关寄存器

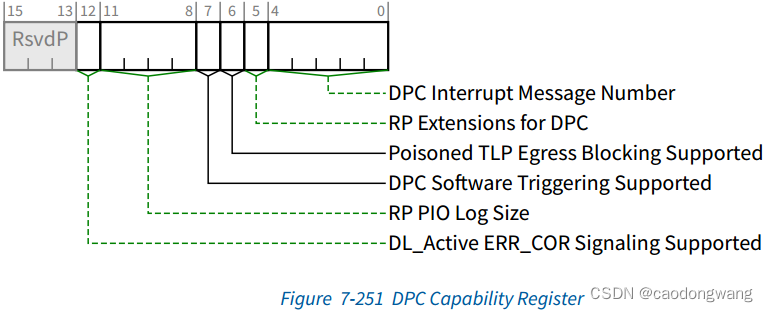

DPC Capability Register (Offset 04h)

DPC能力寄存器。

| Bit | 描述 | 权限 |

|---|---|---|

| 4:0 | DPC Interrupt Message Number,定义了Port针对收到的error message将使用MSI/MSIX的哪个entry来产生中断通知的系统。这个field由HW给出的,并且可能会随着enable MSI/MSIX entry数目的不同而变化。注意,这个值必须小于等于31,因为需要兼容MSI中断(MSI最多32个中断) | RO |

| 5 | RP Extensions for DPC,该位表示根端口支持特定于根端口的一组定义的DPCl扩展(即DPC 0x10之后的寄存器有效)。PCIe switch下行端口不能设置此位 | RO |

| 6 | Poisoned TLP Egress Blocking Supported,该Bit置1,表示支持阻塞 Poisoned TLP能力 | RO |

| 7 | DPC Sofware Triggering Supported,该Bit置1,表示根端口或交换机下行端口支持软件触发DPC。对于支持DPC的RP扩展的Root Port必须设置此位 | RO |

| 11:8 | RP PIO Log Size ,该字段表示为RP PIO日志寄存器分配了多少DWORDs,由RP PIO Header Log、RP PIO ImpSpec Log和RP PIO TLP Prefix Log组成。如果Root Port支持DPC的RP扩展,该字段的值必须大于等于4;否则,该字段的值必须为0 | RO |

| 12 | DL_Active ERR_COR Signaling Supported,表示根端口或交换机下游端口支持在链路转换为DL_Active状态时,支持使用ERR_COR进行信号传输 | RO |

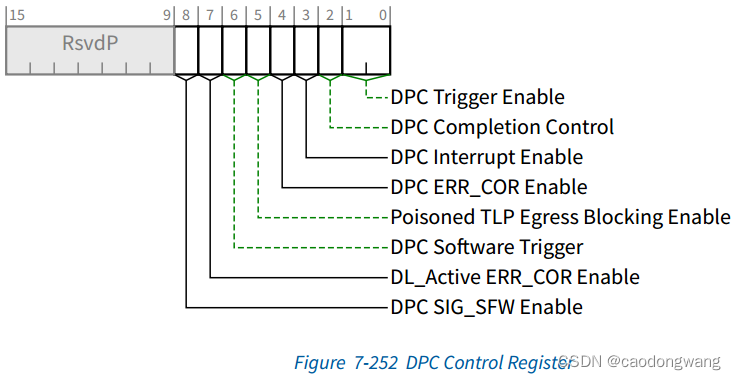

DPC Control Register (Offset 06h)

DPC控制寄存器。

| Bit | 描述 | 权限 |

|---|---|---|

| 1:0 | DPC Trigger Enable,用于控制DPC是否检测下游错误。00,表示关闭检测;01,表示检测不可恢复错误和致命错误消息;02,表示检测不可恢复错误、致命错误消息、非致命错误消息;03,预留 | RW |

| 2 | DPC Completion Control,这个Bit控制在DPC期间回复什么完成状态的报文给下游。0,回复Completer Abort (CA) Completion Status完成报文;1,回复Unsupported Request (UR) Completion Status完成报文 | RW |

| 3 | DPC Interrupt Enable,该Bit置1,当DPC检测到问题,是否要上报中断 | RW |

| 4 | DPC ERR_COR Enable,该Bit置1,当DPC检测到问题,可以发送ERR_COR消息给上游报告已触发DPC | RW |

| 5 | Poisoned TLP Egress Blocking Enable,该Bit置1,则不允许转发Poisoned TLP | RW/RO |

| 6 | DPC Sofware Trigger,向该Bit写1,可以软件触发DPC,这个Bit读为0 | RW/RO |

| 7 | DL_Active ERR_COR Enabl,如果设置了该位,表示根端口或交换机下游端口支持在链路转换为DL_Active状态时,支持使用ERR_COR进行信号传输(即主动发出ERR_COR) | RW/RO |

| 8 | DPC SIG_SFW Enable,当设置时,启用发送ERR_COR消息,以指示已启用ERR_COR信号的DPC事件(ECS有效) | RW/RO |

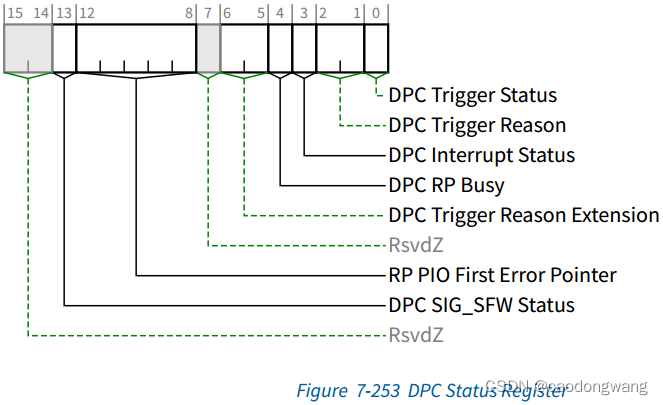

DPC Status Register (Offset 08h)

| Bit | 描述 | 权限 |

|---|---|---|

| 0 | DPC Trigger Status,当该Bit置1时,表示DPC已经触发,此时这个Port下游链路将LTSSM转为禁用状态(链路断开无法link),只有将此Bit写1清除,LTSSM才能从禁用状态释放出来,即下游重新训练,注意,进入DPC之后,必须等待100ms才能清除(链路link down需要一定时间),且清除之后还必须等待100ms才能访问下游设备 | RW1CS |

| 2:1 | DPC Trigger Reason,表示是因为什么触发DPC的。00b,表示收到未屏蔽的不可纠正错误;01b,表示收到ERR_NONFATAL消息;10b,表示收到ERR_FATAL消息;11b,表示信息由扩展字段(DPC Trigger Reason Extension)指示; | ROS |

| 3 | DPC Interrupt Status,表示是否产生了DPC中断 | RW1CS |

| 4 | DPC RP Busy,当触发DPC时,可能DP内部在繁忙,必须等待该Bit为0时,才能对DPC Trigger Status写1 | RO/RsvdZ |

| 6:5 | DPC Trigger Reason Extension,DPC触发原因扩展字段,当DPC Trigger Reason字段为11b时,该字段才有效。00b,表示由RP PIO error触发DPC;01b,表示由软件主动触发DPC | ROS |

| 12:8 | RP PIO First Error Pointer,该字段指示RP PIO状态寄存器中的位位置,当该位被设置时,该字段被认为是有效的。当该字段有效时,软件将1b写入指定的RP PIO Status位(从而清除它),该字段必须恢复到其默认值。该字段仅适用于支持DPC的RP扩展的Root端口,否则为保留。如果该字段不为Reserved,则默认值为11111b,表示永久保留的RP PIO状态位,因此保证该字段不被认为是有效的。 | ROS/RsvdZ |

| 13 | DPC SIG_SFW Status,当该Bit置1,表示使用了SIG_SFW ERR_COR消息触发了DPC事件 | RW1CS/RsvdZ |

DPC Error Source ID Register (Offset 0Ah)

错误源ID寄存器,当Port收到ERR_NONFATAL或ERR_FATAL而触发DPC时,该字段存放发送错误消息的请求者ID(BDF)。

其他寄存器

只有Root Port支持扩展DPC能力(RP Extensions for DPC)才有效,本文不展开。