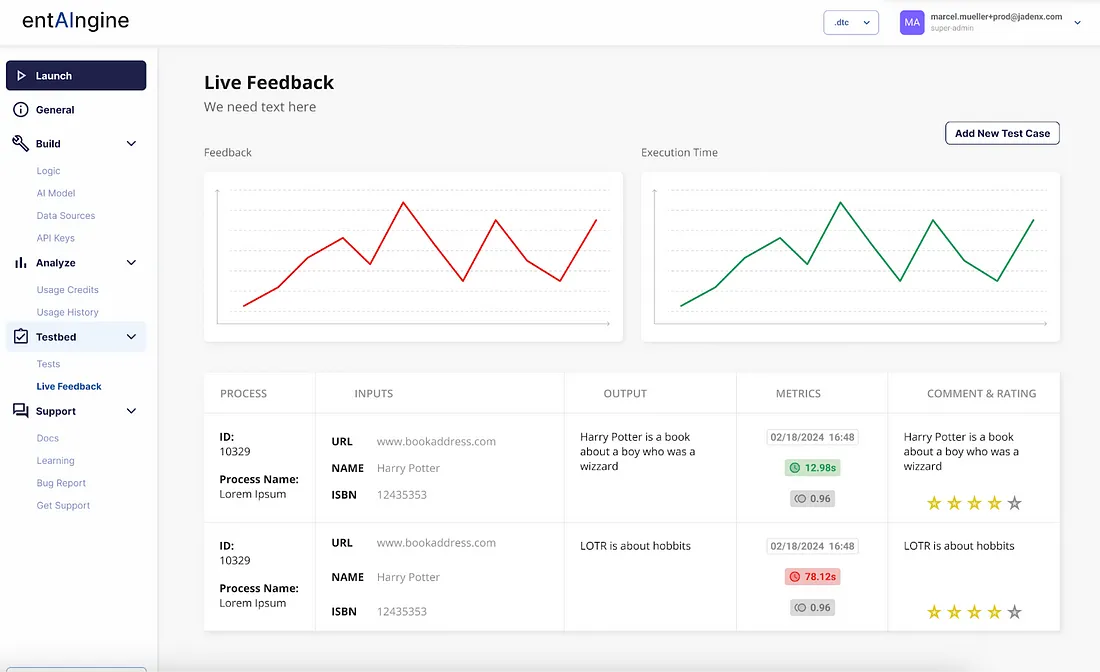

1.1 EDMA3简介

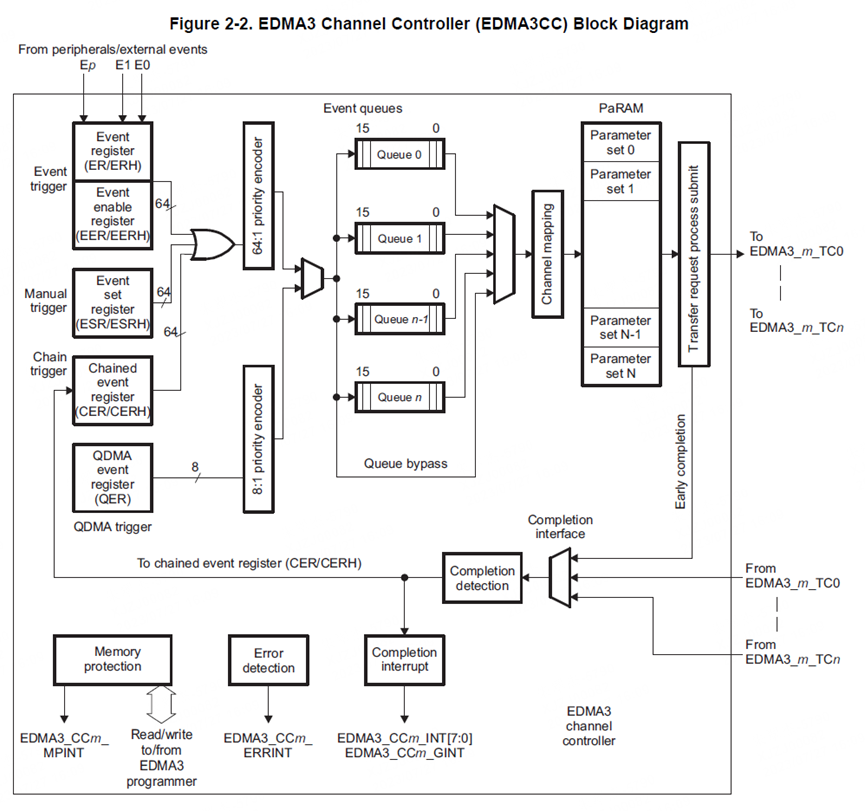

EDMA3(Enhanced Direct Memory Access 3):增强型直接存储器访问的控制器。它是DSP中一个高级数据传输引擎,其结构适合数据的高速传输,可以在没有CPU主要参与的情况下,由控制器完成数据转移,主要服务外部内存(DDR)、片上内存(L2 SRAM)以及串口外设等。EDMA3控制器主要由两个模块组成:

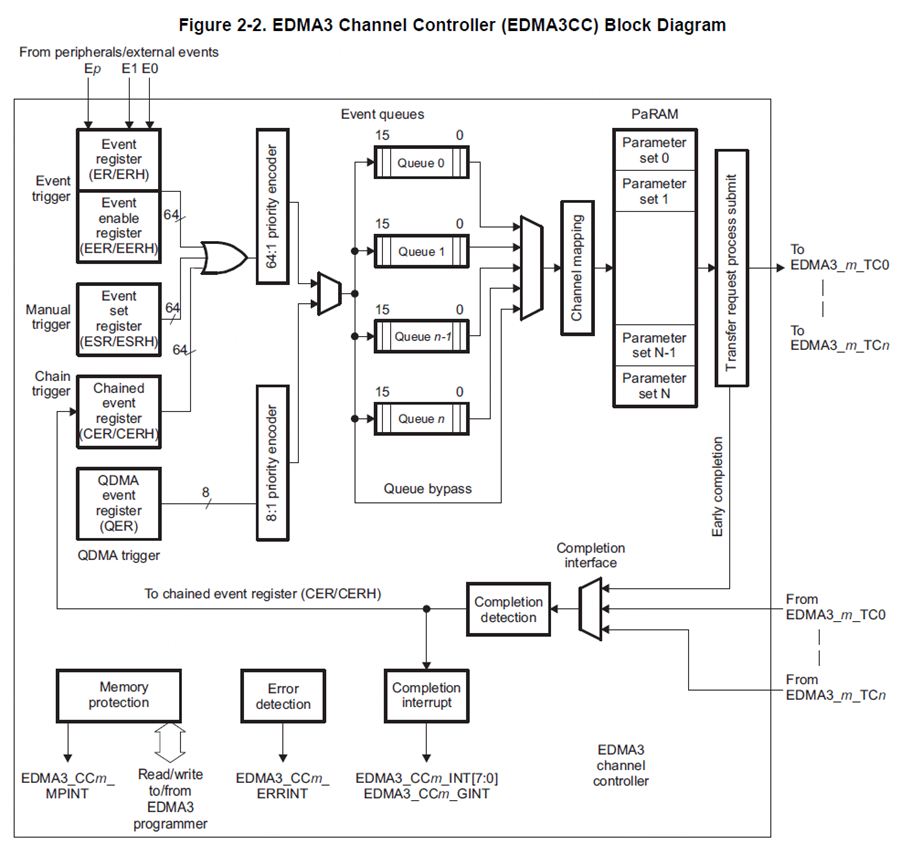

EDMA3通道控制器(EDMA3CC),作为EDMA3控制器的用户接口,其参数主要包括:参数RAM(PaRAM)、通道控制寄存器、中断控制寄存器等。EDMA3CC负责软件请求或外设事件的优先级管理,向传输控制器发送传输请求(TR)。

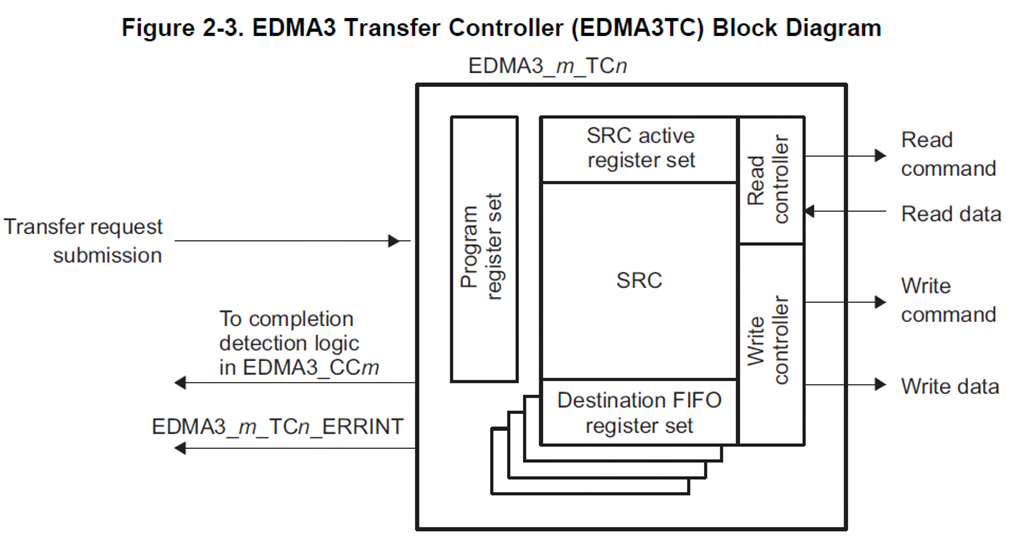

EDMA3传输控制器(EDMA3TC),接受CC的TR,向传输的源和目的地址发出读写请求并执行数据传输。

1.2 EDMA3特征

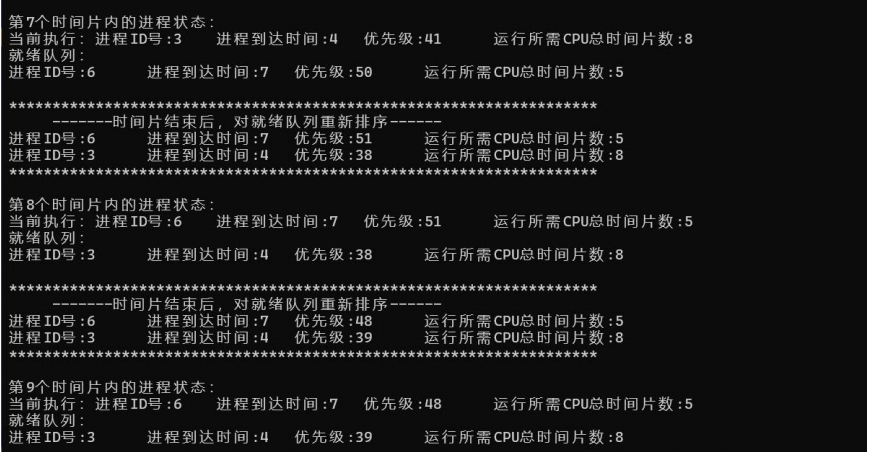

① 提供三个维度完全正交的传输方式(三个维度之间不存在相互干扰);

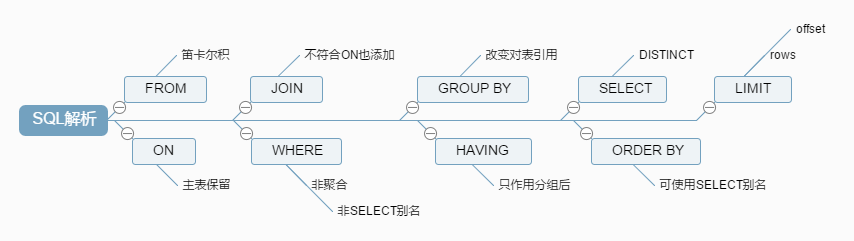

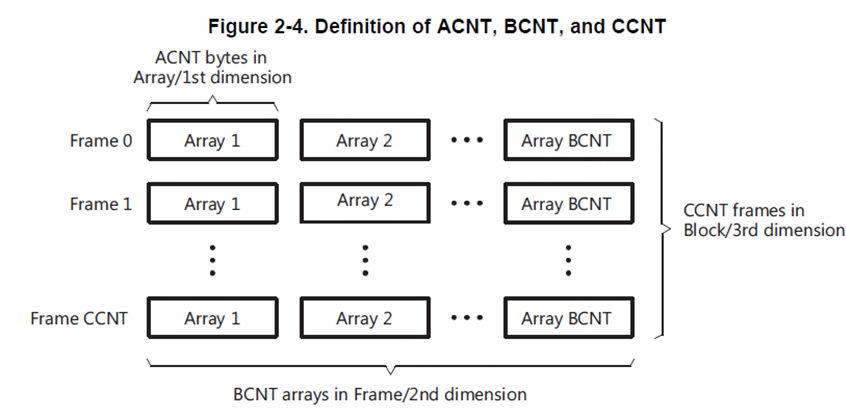

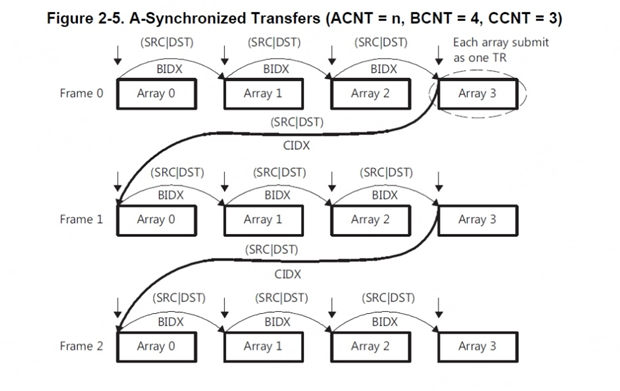

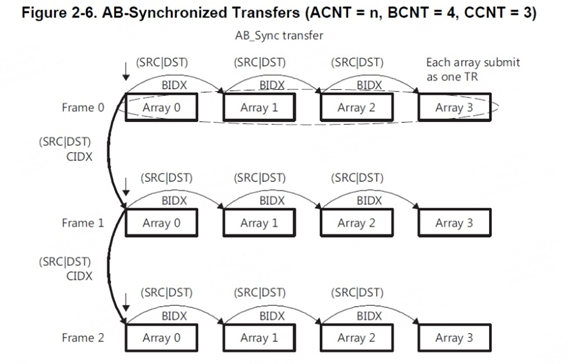

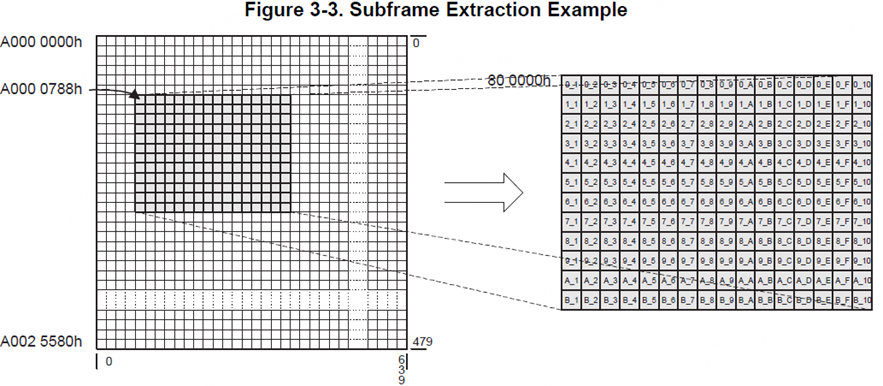

EDMA3支持1D传输(A同步传输:一次触发值搬移ACNT个字节的数据,BCNT=1、CCNT=1)和2D传输(AB同步传输:一次触发只搬运ACNT*BCNT个字节数据,CCNT=1)这两种方式,不支持同步3D传输,但可以通过配置EDMA3为周期性事件触发模式,同时配置好CCNT的值,就可以实现ABC的3D传输,如下图。

NOTE:

A同步传输:以阵列为单位进行1D阵列传输(每个event/TR包只传输一个阵列的数据,因此为了完整服务PaRAM set 需要BCNT*CCNT个event),阵列中字节个数由ACNT决定,相邻阵列间隔由BIDX决定,相邻帧的间隔由CIDX决定(尾->首)。

AB同步传输:以帧为单位进行2D帧传输(每个event/TR包只传输一帧的数据,需要CCNT个event)帧中阵列间隔仍是BIDX决定,但CIDX是指帧之间的首地址间隔(首->首)。

A模式和AB模式详细关系如下:

② 可变的独立源地址和目的地址;

EDMA3在初始化时会设定源地址和目的地址,在EDMA3的传输过程中,其源地址和目的地址会不断往后偏移。

③ 支持事件同步传输、手动同步传输以及链接同步传输方式;

事件同步传输:外设、系统或者外部产生的事件触发请求

手动同步传输:CPU通过在对应的寄存器位(ESR/ESRH)上写1来进行主动触发产生发送请求

链接同步传输:一个发送的完成触发(当EDMA3CC提交了与当前传输相关的全部PaRAM set后,表示事件参数耗尽,通过重新加载参数集指针)另一次的发送(要终止发送,可以通过null传输来阻塞)

NOTE:

Linking传输:当event对应的通道传输完成后,通过update(预设)PaRAM set中的LINK值且OPT中的STATIC位为0时,实现linking传输。其特点是不需要CPU中断的情况下实现循环传输的场景或ping-pong buffer。

Chaining传输:event在对应通道中完成传输或TR后对应的PaRAM无需update即可链接另一个event对应另一通道进行传输。

EDMA3CC对待null和dummy传输时不同。

(当ACNT、BCNT、CCNT全0时)null传输是一次非法传输,事件缺失寄存器(EMR/QEMR)会置1,并且相关次要事件寄存器(SER/QSER)也会保持为1,这样会阻塞通道。

(当ACNT、BCNT、CCNT至少一个为0以及至少一个不为0时)dummy传输实现一次0字节的合法传输,EMR/QEMR不会置0,并且SER/QSER会被清0,保证通道不会阻塞后续传输。

④ EDMA3具有64个DMA通道,8个QDMA通道。256个PaRAM参数集。每一个通道都可以与给定的事件队列和PaRAM相关联。

⑤ EDMA3主要包括EDMA3CC(通道控制器)和EDMA3TC(传输控制器),EDMA3CC是用户控制EDMA控制器的接口,是EDMA3中用户编程的一部分。DEMA3CC包括PaRAM参数、通道控制寄存器以及中断控制寄存器。传输控制器EDMA3TC负责数据的搬移并分别向源地址和目的地址发出读写命令,源地址和目的地址是在EDMA3CC中设定的。

1.3 EDMA3CC

- DMA/QDMA channel logic:主要包括对外部事件的捕获,配置DMA/QMDA通道的寄存器以及配置不同触发类型的使能和状态寄存器。

- EDMA3 event和interruption处理寄存器:映射事件的参数设置,事件使能/去使能,中断使能/去使能,清除中断等。

- Event queues:事件检测逻辑和发送请求提交逻辑之间的接口。

- PaRAM:设置了数据传输的一些信息,例如源地址、目的地址、传输的数据大小,以及传输方式等信息。

- TR submission logic:将基于事件的PaRAM set向TC提交TR。

- Completion detection:可用作链接触发新传输或向DSP断言完成中断。

- Error detection:检测触发执行后产生的错误并向DSP断言错误中断。

- Memory protection:定义了主动存储保护和代理存储保护。

NOTE:队列深度为16,队列数量对应于TC数量。如果队列和TC都处于empty,new event可以绕过队列直接到PaRAM处理逻辑后向TC进行TR。这种情况下,event不会被event队列状态寄存器记录。

1.4 EDMA3TC

- DMA program register set:存储来自CC的TR。

- SRC active register set:为正在进行的读控制器存储TR中源端的传输上下文。

- Read controller:用于向源端发出数据读命令。

- DST FIFO register set:为正在进行的写控制器存储TR中目的端的传输上下文。

- Write controller:用于向目的端发出数据写命令。

- Data FIFO:临时存放读取来的in-flight数据。

- Completion interface:主要用于传输完成时向CC返回completion code,用于产生中断和链接event。

NOTE:

Q:为何SRC的寄存器集设置为普通的存储形式,而DST寄存器集设置为FIFO的存储形式?

A:发出读请求后,可能需要等待较长周期来接受

1.5 PaRAM

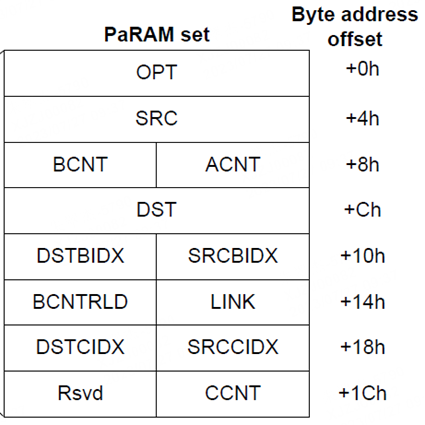

EDMA3共有256个PaRAM参数集,DMA和QDMA的通道传输内容(源/目的地址、数量、索引值等)都是在PaRAM中设置的。用户可以将256个PaRAM映射到任意DMA通道或QDMA通道上,来控制传输控制器进行一定数据量的搬运。

PaRAM各字段含义

|

字段 |

含义 |

|

OPT |

传输配置选项 |

|

SRC |

数据源端地址 |

|

ACNT |

一个array中的连续字节数 |

|

BCNT |

一帧中的array数 |

|

DST |

数据目的端地址 |

|

SRCBIDX |

源BCNT索引值,数据源端提取时的array间隔 |

|

DSTBIDX |

目的BCNT索引值,数据目的端排布时的array间隔 |

|

LINK |

当前PaRAM耗尽时,用于LINK的PaRAM的地址 |

|

BCNTRLD |

A同步传输时,BCNT耗尽时的重载值 |

|

SRCCIDX |

源端CCNT索引值,数据源端提取时的帧间隔 |

|

DSTCIDX |

目的端CCNT索引值,数据目的端排布时的帧间隔 |

|

CCNT |

一个传输块中的帧数 |

1.6 DMA和QDMA的区别

DMA和QDMA通道的不同之处在于使用的触发条件不同。DMA的触发方式有三种:主动触发、事件触发以及链接触发。而QDMA的触发方式是通过配置PaRAM参数中的触发字后就会自动触发,链接触发与DMA比较类似。QDMA只能发送1D array的数据格式,而DMA可以发送1D、2D和3D的数据格式;DMA通道比QDMA通道优先级更高。

1.7 配置EDMA3发送的主要步骤

- DMA通道的初始化:

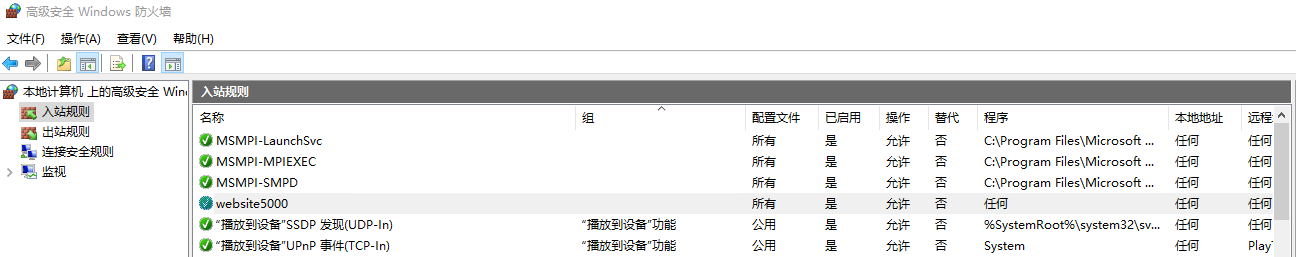

a.通道选择,包括通道类型选择以及通道号选择,特别是事件触发时,不同的事件绑定了不同的通道号(在主动触发方式下,可以任意选择通道号,但不可冲突。如果是事件触发模式,必须使用触发事件对应的通道号)。

b.通道映射,QDMA通道:用QCHMAP寄存器将PaRAM参数地址映射到使用的通道;

DMA通道:用DCHMAP寄存器对PaRAM参数地址映射到使用的通道;

c.通道分区配置,EDMA3CC寄存器分为全局寄存器、全局区域通道寄存器和shadow区域通道寄存器,若将某个通道配置为shadow区域,那么后续操作必须使用shadow区域的寄存器。

d.确定触发类型,选择DMA/QDMA通道并配置对应通道的使能寄存器。

e.根据DMA/QDMA通道来分配不同的事件队列上。

NOTE:

全局寄存器:位于EDMA3CC唯一且固定的内存映射处,其主要控制EDMA3资源映射、提供相应通道的可视化debug以及error tracking信息。

通道寄存器:包括DMA、QDMA以及中断寄存器

2. PaRAM参数配置

将搬移的上下文信息配置到绑定通道的PaRAM中。

3. 中断配置

PaRAM中的OPT字段中配置使能相应的中断,通过设置IESR/IESRH使能中断响应。

4. 触发传输

a.事件触发,每当外部事件发生后,EDMA3自动传输一次数据。

b.手动传输,通过CPU手动配置ESR寄存器触发。

c.链接触发,根据linking或chaining的方式进行链接触发。

5. 等待完成

a. 在中断复位函数中等待,按照3的中断配置,当传输完成后,EDMA3会通过设置IPR/IPRH(中断待处理寄存器)给DSP产生中断,完成后由ICR/ICRH(中断清除寄存器)进行清零。

b. 轮询寄存器,若未产生使能中断响应,要等待相应的IPR/IPRH置1,表示传输完成。

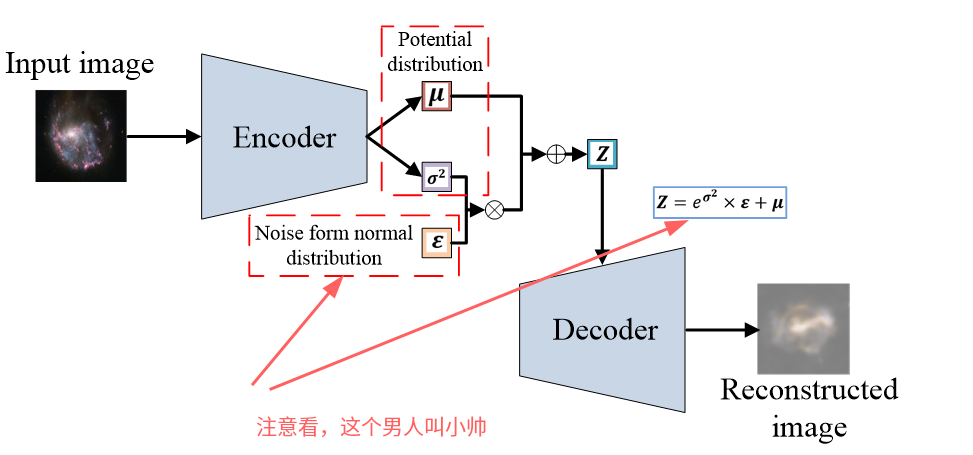

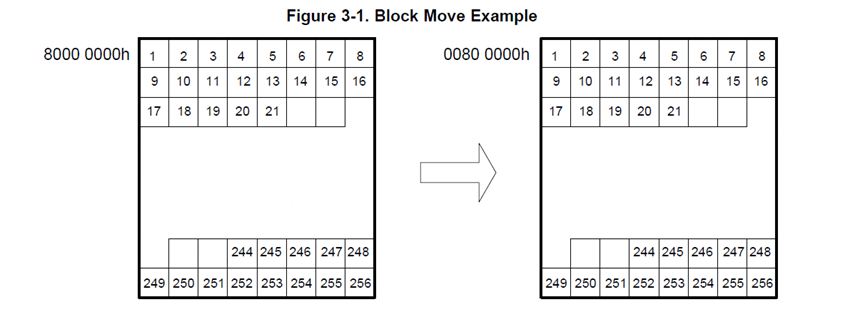

1.8 传输实例

外部存储向L2 SRAM进行data block copy

整块作为一个1D传输阵列的参数,并且OPT中的STATIC位置1禁止linking传输。

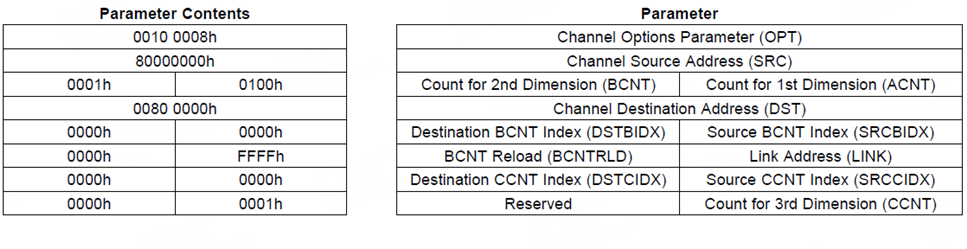

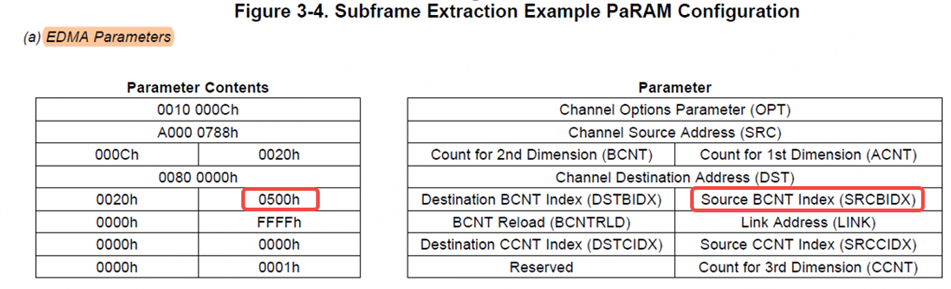

子帧提取

每个pixel是16bit半字=2 Byte 一共16*12-pixel子帧,作为一个frame进行AB传输,ACNT=2*16=32,BCNT=12

作为一个frame 2D传输的参数,其中OPT中的STATIC设置为1。

NOTE:AB的3D模式传输时,STATIC必须为0,即允许update parameter set(ACNT、BCNT、CCNT)或者允许linking传输,而2D传输时,STATIC位只对于是否进行linking传输有作用(预设Link Address)。

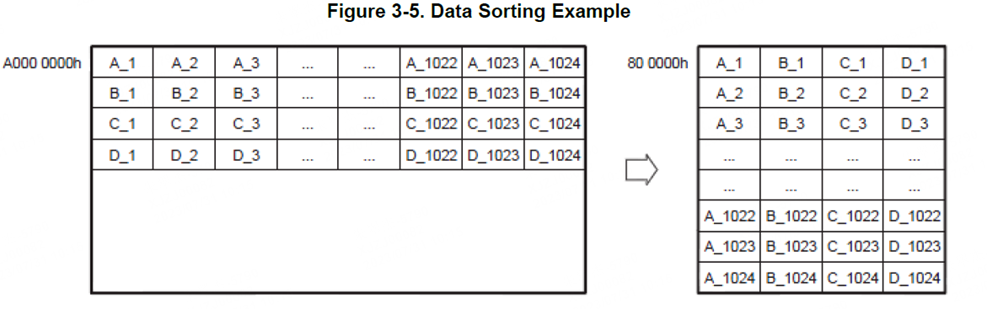

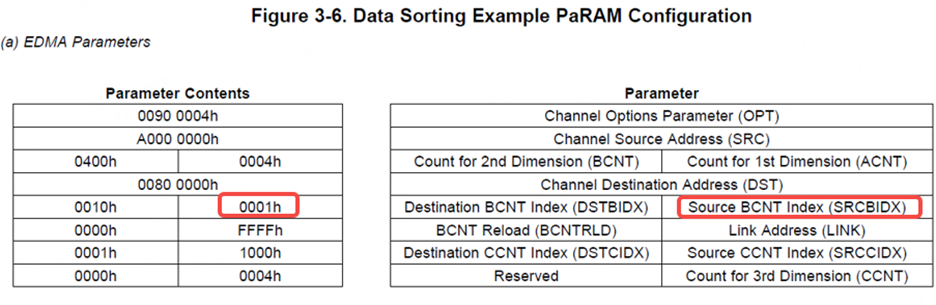

数据分类

每帧由1024个阵列组成,每个阵列由4个bytes组成,一共4帧。

ACNT=4、BCNT=1024、CCNT=4,SRCBIDX=1,SRCCIDX=1024*4=4096=1000h,DSTBIDX=4*4=16=10h,DSTCIDX=1

NOTE:SRCBIDX=1以及DSTCIDX=1时,数据存取时出现数据交叠,可能应用为滑窗数据取样?应用于神经网络卷积?