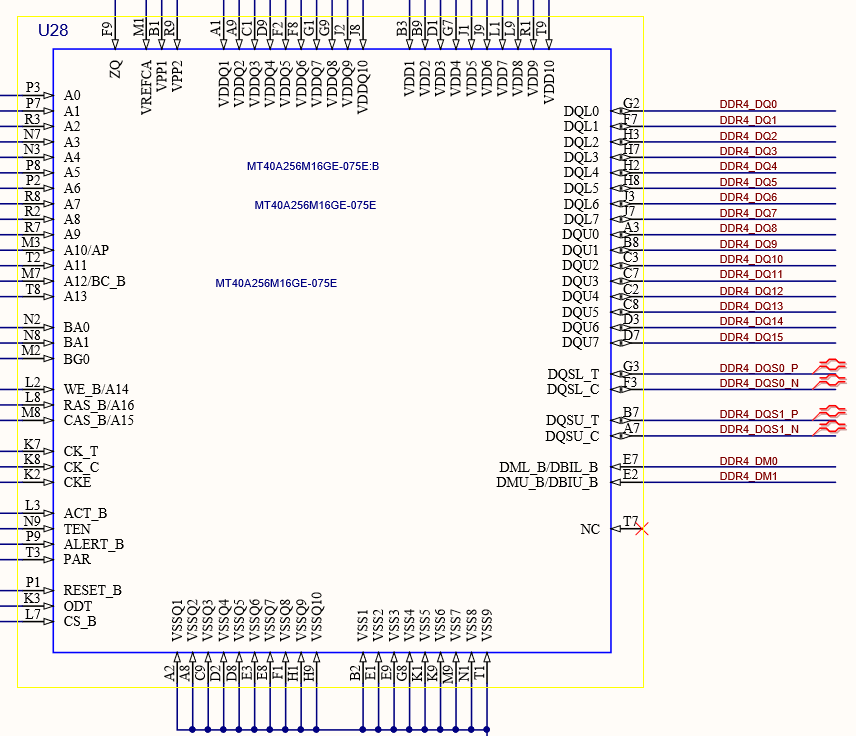

首先这是PL端的DDR4芯片,型号为MT40A256M16GE-075E,256Mx16,即512MB,由于不能上传附件,所以PDF还请大家自行上网搜索下载。

DDR4参数的获取参考了以下两个CSDN的博客。

https://ztzhang.blog.csdn.net/article/details/142444632

https://blog.csdn.net/apple_53311083/article/details/144952443

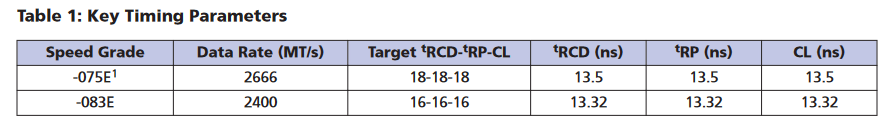

时序参数信息表格如下,

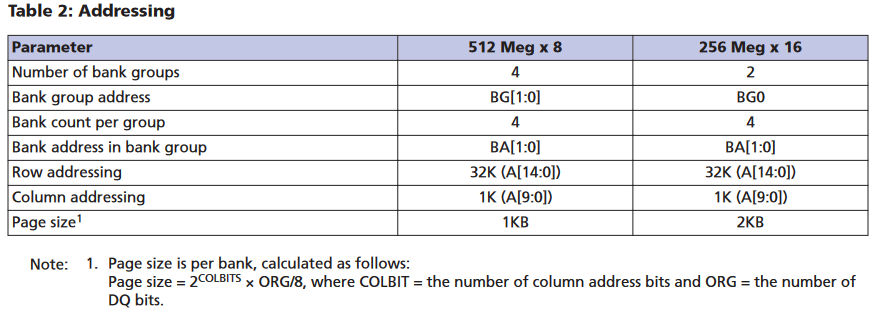

地址信息如下,这里简单描述一下,2个bank组,每个bank组里有4个bank,512MB/8=64MB,即每个bank64MB容量,行列位宽=3210241102416/8/1024/1024=64MB与前面计算的结果相符合。

简单来讲总bank数行列=832102411024/1024/1024=256M,这就是前面型号名称256M的由来,加上位宽16,可简单理解为,按16并行写入,可写256M次。

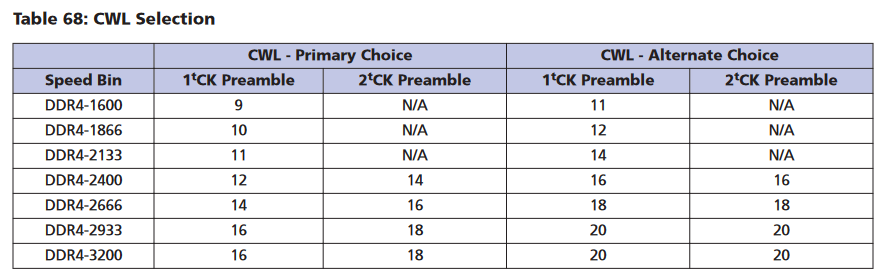

CWL信息如下。

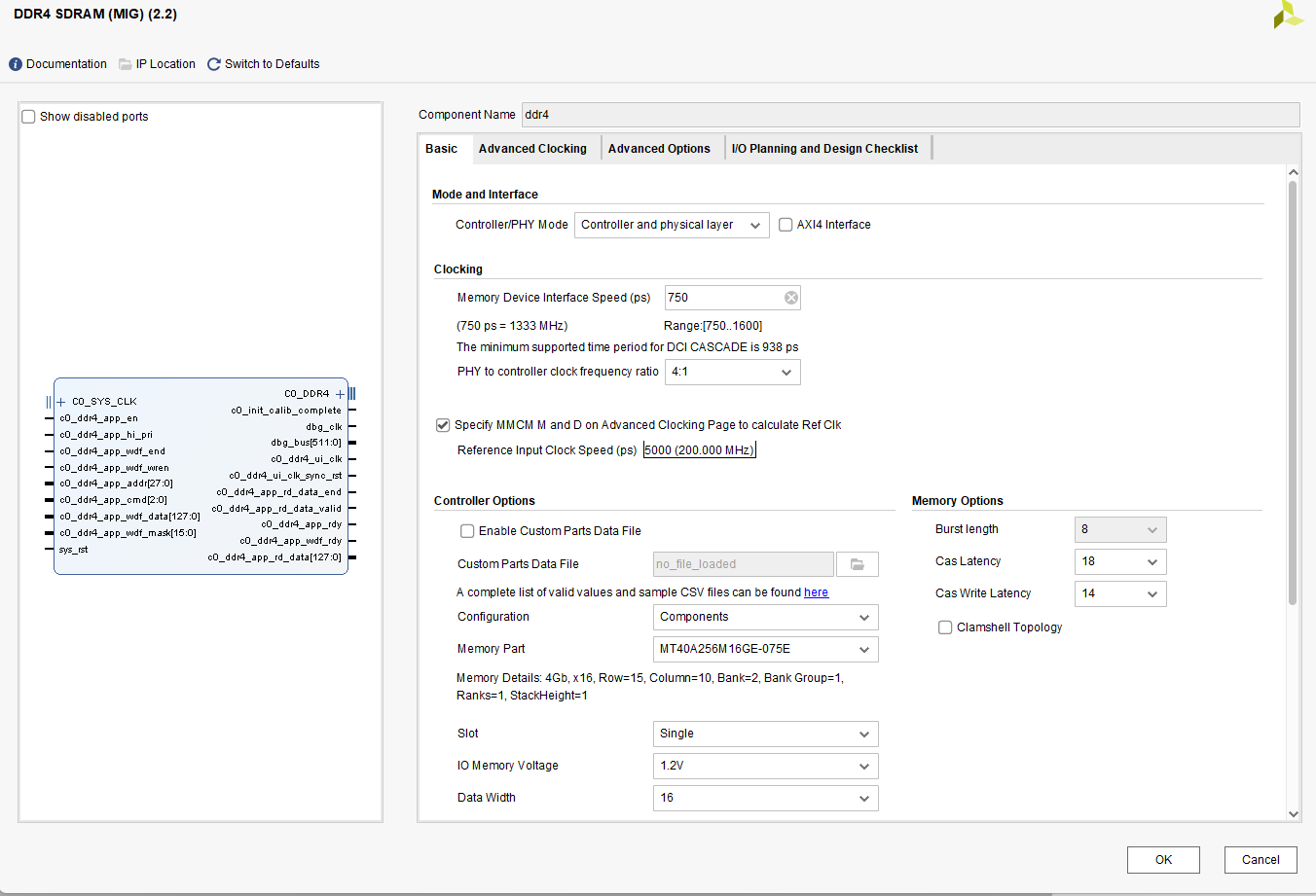

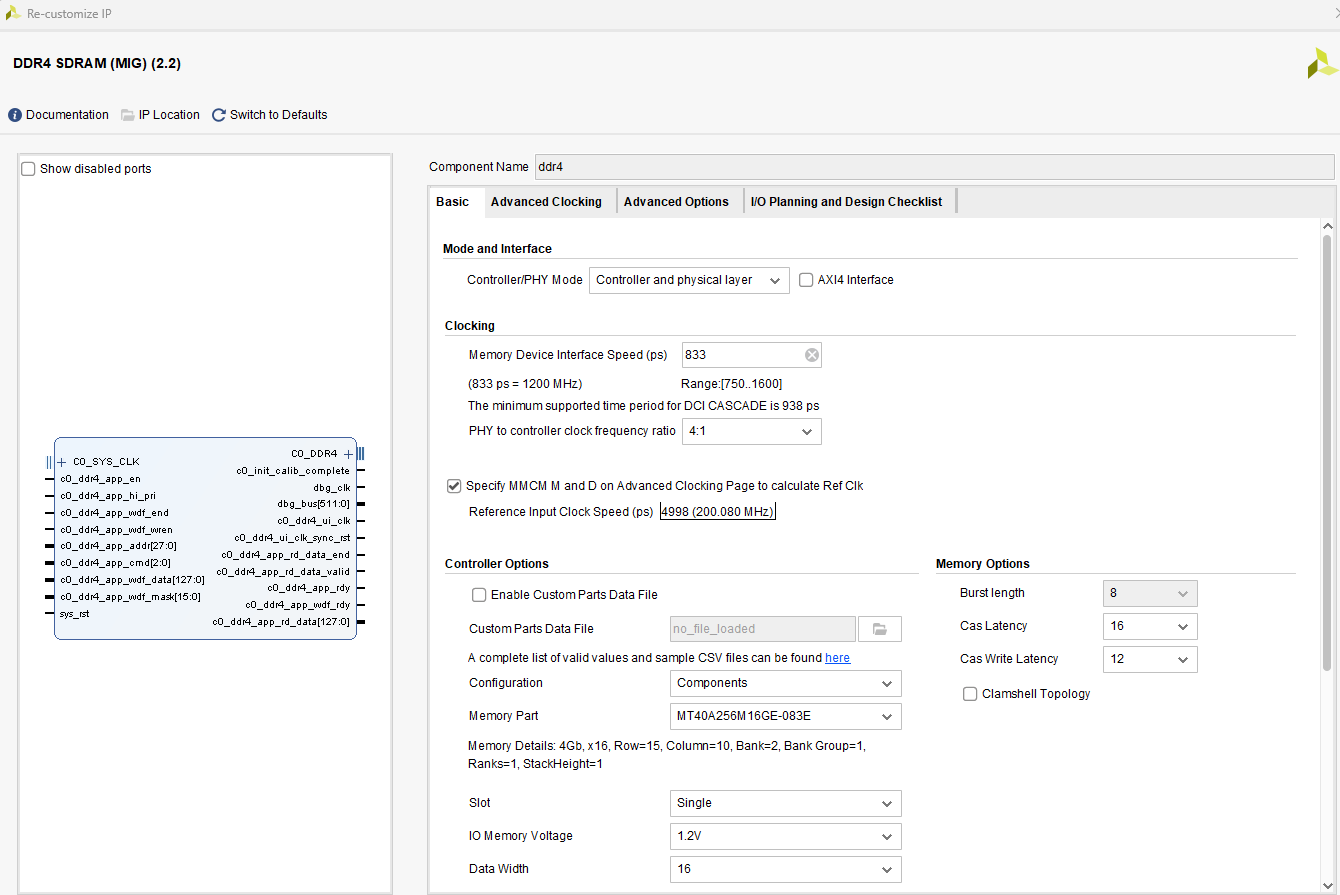

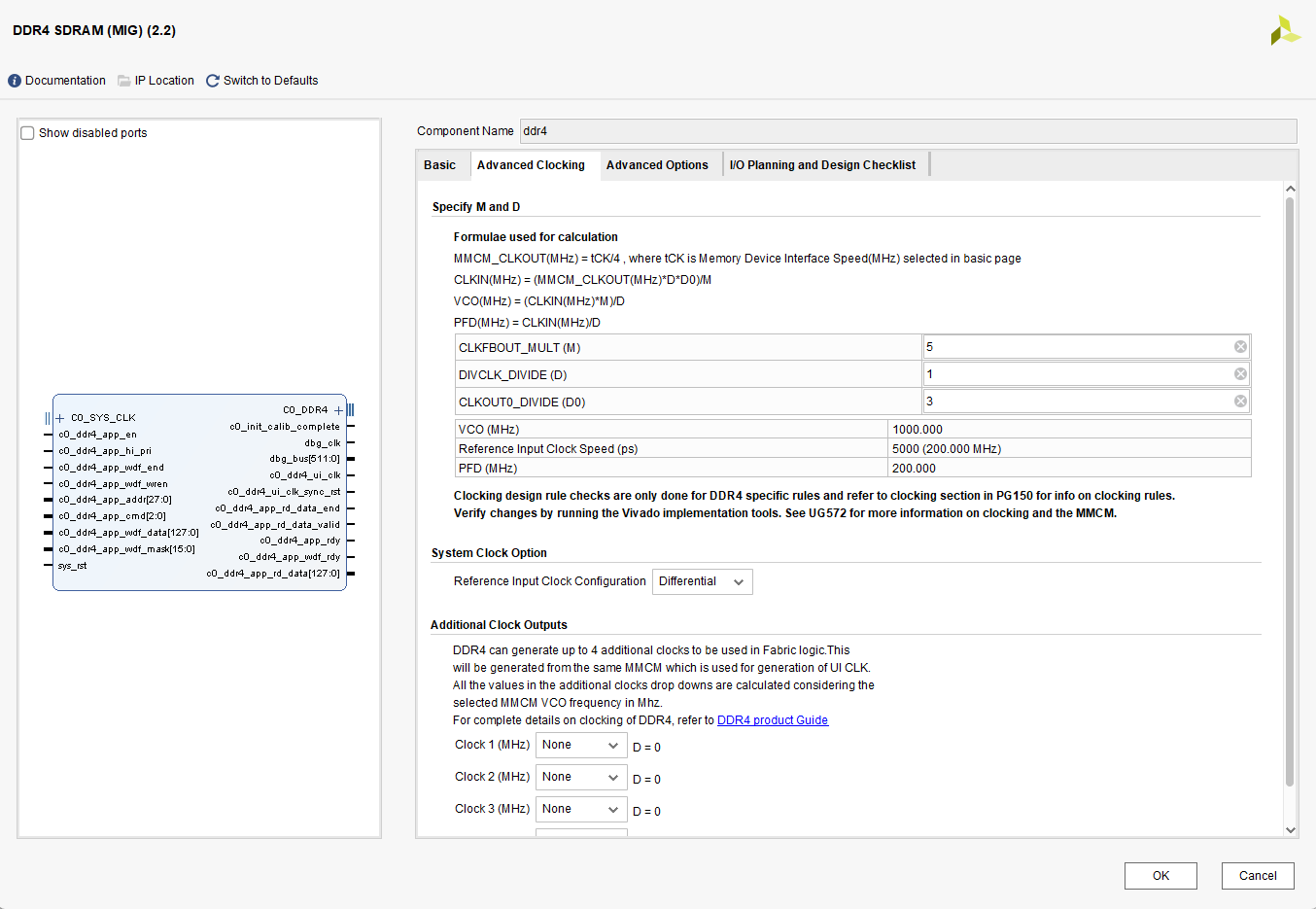

打开vivado,点击MIG DDR4 IP核,具体设置如下,未展示的部分默认(两种配置方式,2666MHz或者2400MHz,实测,都可以),输入时钟,该板卡输入是200MHz差分时钟,具体引脚请看原理图。

逻辑代码部分参考了官方example design的逻辑代码,官方的例程是先写入一大段,然后再读出来测试验证,我这边是写8个,读8个,ila看是否正确。

代码直接抄就行,我另一个随笔分类有解析,这边不再详述。下面展示ila波形。

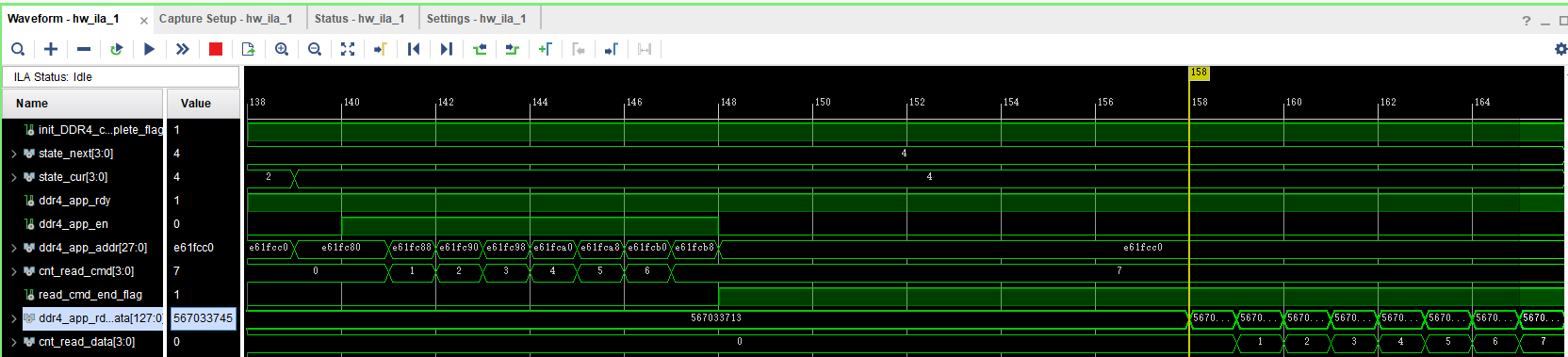

ila写时序波形,地址从e61fc80到e61fcb8,对应写入数据为567033745-567033752共八个数字

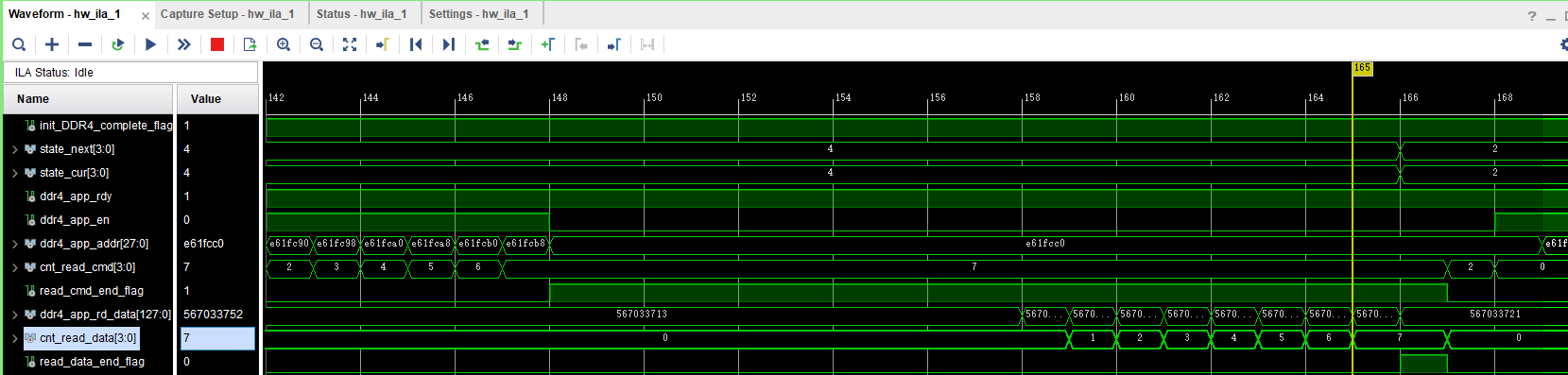

ila读时序波形,地址从e61fc80到e61fcb8,对应读出数据为567033745-567033752

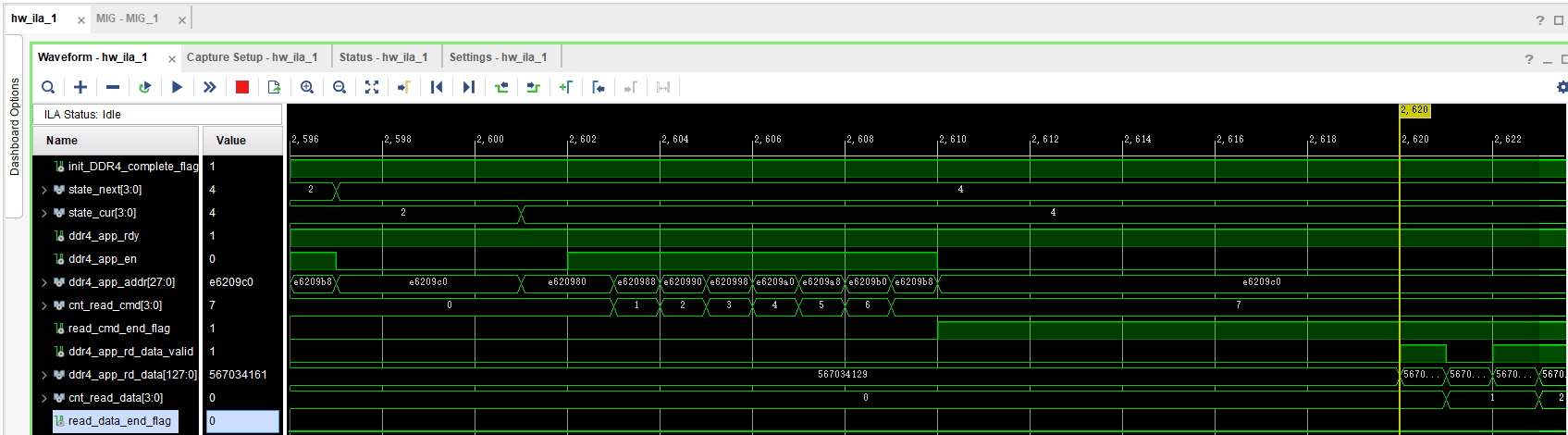

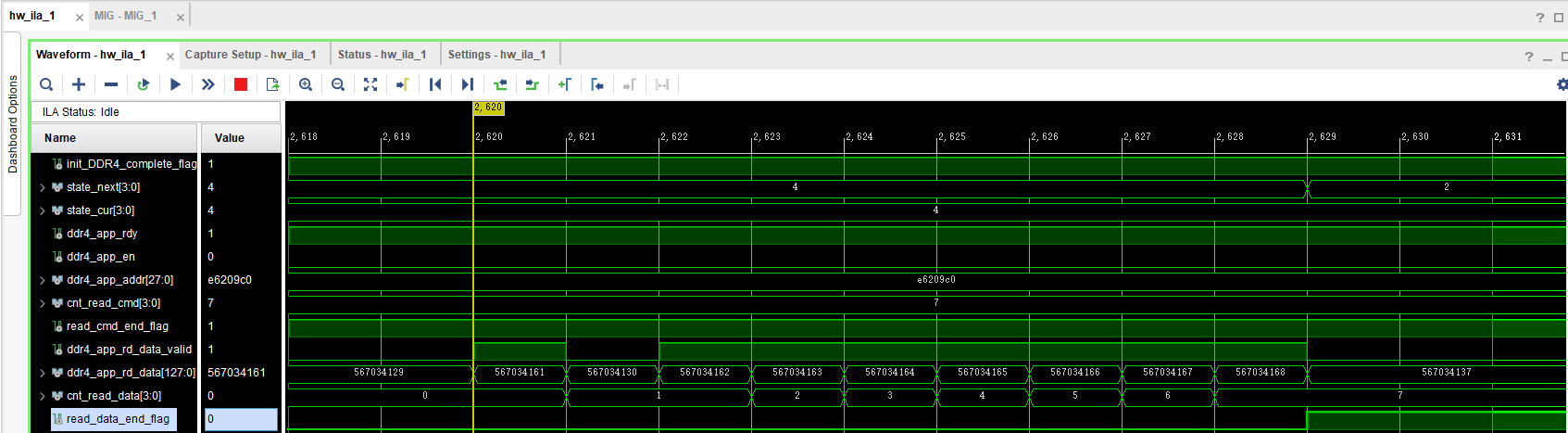

再选一段后面。写部分,地址从e620980到e6209b8,对应写入数据为567034161到567034168

读部分以及读出来的数据,都是对应的上的。

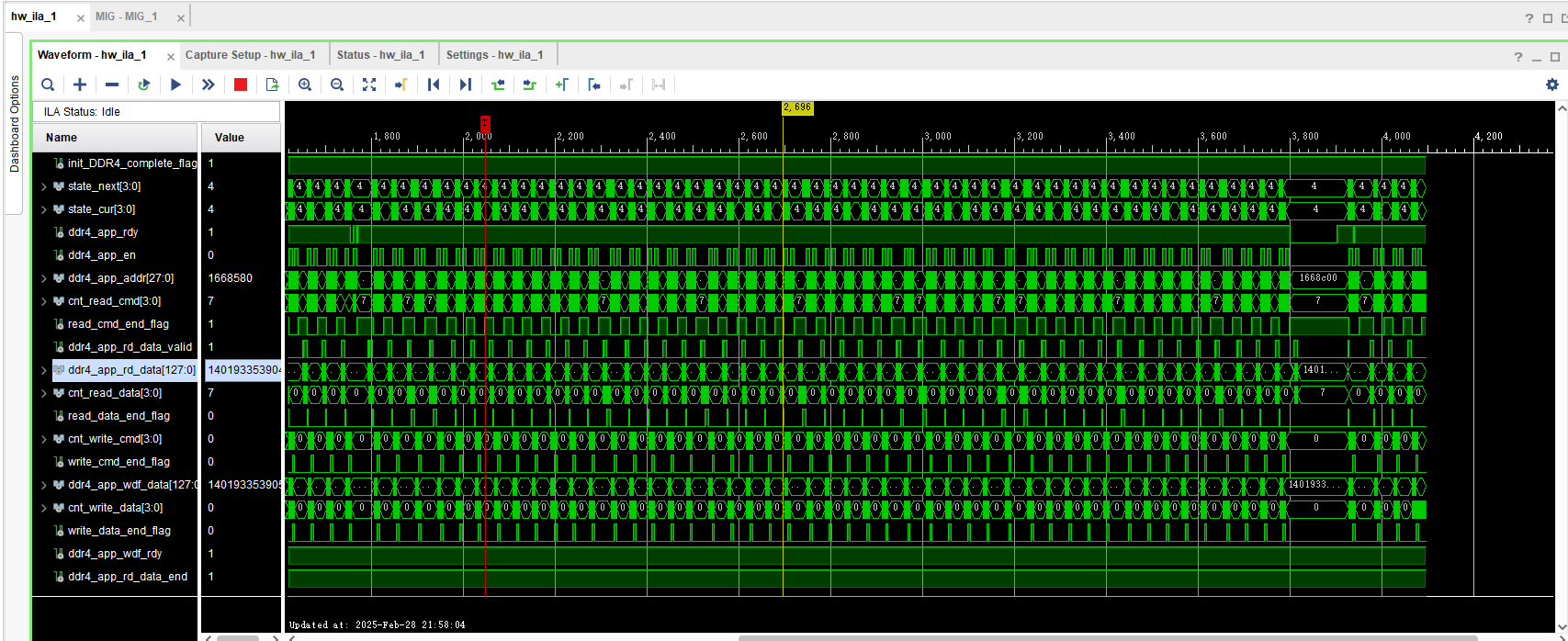

MIG IP核PASS

一段时间后,再ila取数据,对比后依然读写数据能对应上,故DDR4数据读写实验通过。

天嵌通途xczu15eg学习笔记——PL端DDR4的MIG IP核配置及测试过程

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.hqwc.cn/news/894687.html

如若内容造成侵权/违法违规/事实不符,请联系编程知识网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!相关文章

ThingsPanel与ThingsBoard:深度对比与选型剖析

在物联网平台领域,ThingsPanel和ThingsBoard各有千秋,为助大家明晰二者差异、精准选型,以下将从多个核心维度展开深度解读:ThingsPanelThingsBoard一、开源协议与版本模式开源协议:

ThingsPanel遵循AGPLv3.0协议。

ThingsBoard采用Apache2.0协议。

版本提供:二者均配备社…

2025 年开源替代方案为何正在取代 OutSystems?技术自由度与成本优势深度解析

2025 年企业为何转向开源?揭秘 OutSystems 四大痛点,推荐 NocoBase、Appsmith、Budibase 等开源方案,帮助你的团队实现技术自由+成本优势双赢。原文链接:https://www.nocobase.com/cn/blog/outsystems-open-source-alternatives

OutSystems 的隐藏成本不只是金钱

OutSystem…

rocketmq引入版本不对的问题

原因是,公司电脑可以正常启动,自己的电脑启动报错,报错是缺少了这个类

之后查看版本发现对不上,公司的事4.9.7,自己上面的居然是5.1.4

然后去除版本指定版本,不知道是否有问题,反正启动没问题了,不过部署还是用公司电脑吧,怕出问题<dependency><groupId>o…

navicat如何导出数据?附navicat15安装包

前言

大家好,我是小徐啊。navicat是我们常用的数据库连接工具,其功能十分强大。可以说是我使用过的各个连接工具中,最强大的工具。今天,小徐就来介绍下如何在navicat里面导出数据。文末附navicat15获取方式。

如何导出数据

首先,打开navicat,然后连接我们要导出的数据库。…

城市犯罪大数据时空分析与预测系统

随着城市化进程的加快,城市犯罪问题日益突出,对社会稳定和居民安全构成严重威胁。为了有效预防和打击犯罪,提升城市管理水平,构建城市犯罪大数据时空分析与预测系统显得尤为重要。本文将从系统建设内容的角度,探讨如何利用大数据和遥感技术,为城市安全保驾护航。一、系统…

华为云昇腾专区重磅上线!带你入门昇腾AI技术与DeepSeek实践

华为云昇腾专区重磅上线!专区围绕DeepSeek对话、互动式课程体系、业界主流大模型、免费实践环境四大核心能力,打造“体验—学习—应用”闭环,助力开发者实现AI转型“零门槛”跃迁。摘要:专区围绕DeepSeek对话、互动式课程体系、业界主流大模型、免费实践环境四大核心能力,…

基因测序芯片(Flowcell)加工工艺 -原子能和替代能源委员会生物梅里埃公司

一、公司简介:

原子能和替代能源委员会生物梅里埃公司

二、主流产品三、专利检索

★专利检索1:

★专利:

US8647465B2-Method of bonding microstructured substrates-2003

★测序芯片(Flowcell)类型:

纳米孔FC

★加工工艺

1、一种含有微结构(5-50um)的基板的胶水粘接方…

React18 04 JSX底层渲染机制--创建虚拟DOM与真实DOM

关于JSX底层处理机制

1)首先,编写的JSX语法,编译为虚拟DOM对象(virtualDOM)

虚拟DOM对象:框架内部构建的一套对象体系(对象的相关成员都是React内部规定的),基于这些属性描述出所构建视图中的DOM节点的相关特征。

a. 基于babel-preset-react-app,把JSX编译为React.cr…

基因测序芯片(Flowcell)加工工艺 -赛陆医疗

一、公司简介:

赛陆医疗是一家测序和空间组学平台开发商,公司专注于开发自主知识产权的上游测序平台,并基于其上构建了全球领先的超分辨空间组学平台,实现基因组学和空间组学产品的自主开发及科研临床端转化。公司创立于2020年,由美国知名大学教授和三位深圳市孔雀人才联合…