CMOS 版图知识预备

1. 版图效应

CMOS 版图设计前,需要了解一下版图设计中的影响效应。

版图效应的四大主要来源分别是:阱邻近效应(Well Proximity Effect, WPE)、浅槽隔离应力效应(Shallow Trench Isolation, STI)、氧化层长度扩散效应(Length of Oxide Diffusion, LOD), 以及氧化层间隙效应(Oxide Spacing Effect, OSE)是版图相关效应的四个主要来源,他们显著影响 MOSFET 的固有参数。

1.1 阱邻近效应

在 CMOS 工艺中,阱离子注入工艺过程中会出现阱区边缘的横向杂质浓度梯度。这种杂质分布的不均匀性会导致距离阱边缘距离不同的晶体管的阈值电压也会不同,在高精度设计中极为不利。

解决方法:

- 将阱梯度变化沿栅极长度方向定向。

- 同时将多个输出晶体管布置在一个公共大阱中,从而远离任何阱的边缘。

1.2 浅槽隔离应力效应

浅槽隔离(STI)工艺产生的应力对器件性能产生影响,体现在:双轴压缩应力增加了空穴迁移率,降低了电子迁移率;并且影响了阈值电压。

解决方法:

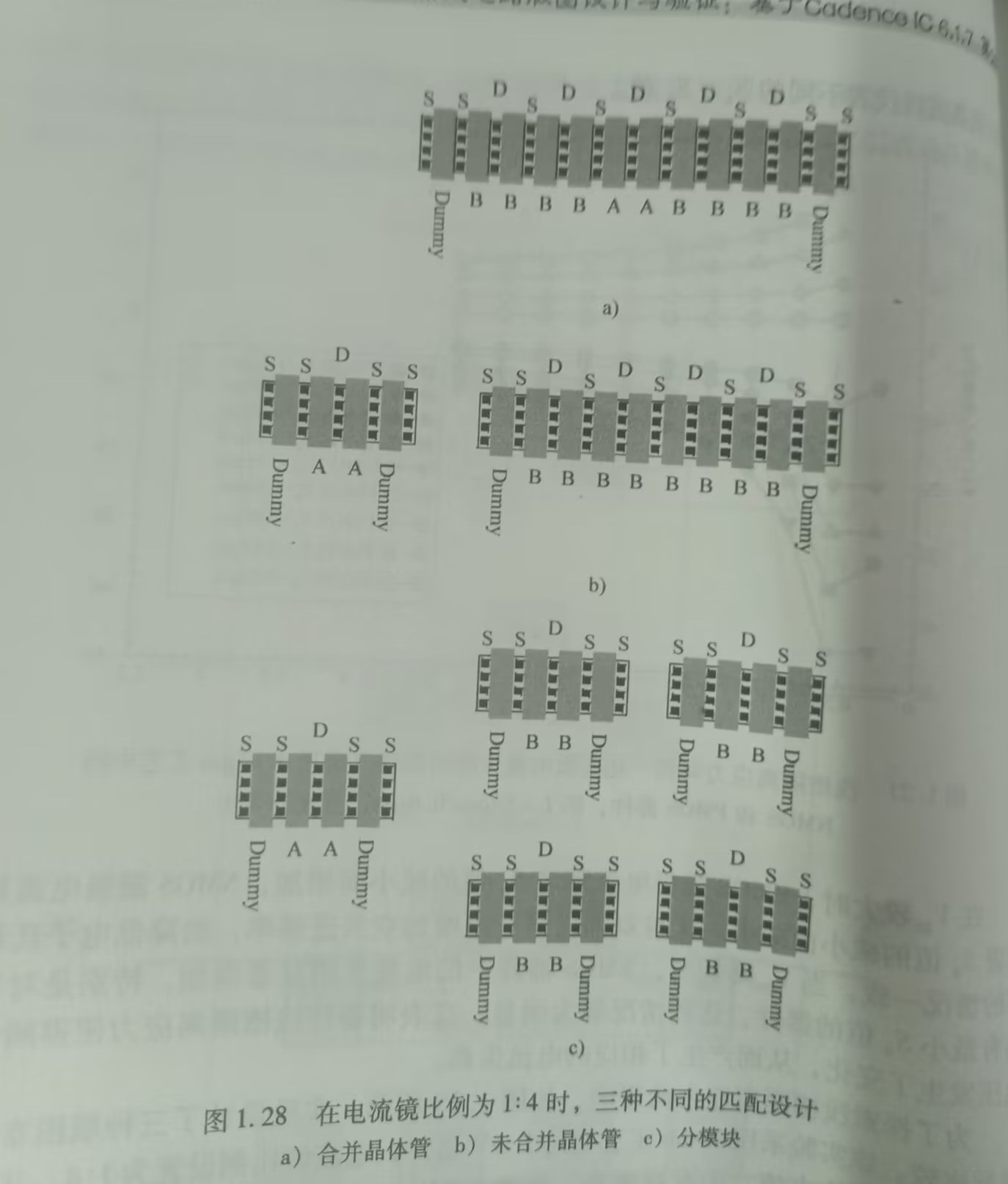

- 消耗更大的硅片面积,使用 dummy 晶体管做虚拟栅。

- 设计电流镜时,为电流镜设计完全相同的匹配模块(对称化设计)。

1.3 氧化物扩散长度和氧化层间隙变化

这两者都可以视为是 STI 应力效应所引起的。

2. 集成电路的 Physical Cells

关于这部分,知乎搬运翻译了很好的一篇面对初学者的文章:

集成电路中的 Physical Cells - elon 在上学的文章 - 知乎

下面介绍五种 Physical Cells:

Filler Cells, Tap Cells, Decap Cells, Boundary Cells, Endcap Cells

2.1 Filler Cells

没有任何特定的逻辑功能,仅用于填充布局中的空白区域,它可以帮助 CMP 表面平整化、保证掺杂区域连续性。

2.2 Tap Cells

也叫 Well Tap Cells,主要用于连接 N-well 或 P-well 区域到相应的电源或地(VDD 或 GND),有效防止了 latch-up 效应。

2.3 Decap Cells

也叫 Decoupling capacitor cells,去耦电容单元,用于稳定电源,去除电源噪声。

2.4 Boundary cells or Endcap Cells

这两个概念没有什么不同:

For 40nm and above, we used endcap cells. For 28nm and below, we used boundary cells.

详见上知乎文章

3. CMOS 版图设计流程

- 系统规格定义

这一阶段,需要确定设计的输入输出、时序、性能指标要求。 - 电路设计

这一阶段也叫前仿,首先确定工艺库(多少 nm,哪家公司,工艺库提供了什么仿真文件?),然后构架系统。 - 电路仿真

借助 EDA 工具的仿真功能,测试电路性能指标,功能是否正确,并且还要评估电路的温漂等环境参数,以保证产品寿命与稳定性。 - 版图设计

集成电路设计中最核心的部分,通常是全定制的手工设计,设计时要遵守设计规则(可以查阅 pdk 文件),并考虑噪声、寄生效应、串扰。 - 物理验证

DRC(设计规则检查)与 LVS(版图与电路图一致性检查)。 - 参数提取后仿真

这一阶段也叫后仿,加入版图中的寄生参数后进行电路网表的仿真。 - 导出流片数据

导出版图数据(GDSII)文件,交给 Foundry 代工厂即可。

要注意,2~6 阶段大部分时候是重复循环进行的,在后仿出现差错时,我们需要返回上一步甚至电路结构设计的步骤来,直到后仿结果满意为止。