芯片上放置HBM(High Bandwidth Memory,高带宽存储器)的主要原因是为了解决传统内存(如DDR、GDDR等)在带宽、容量和功耗方面的限制。

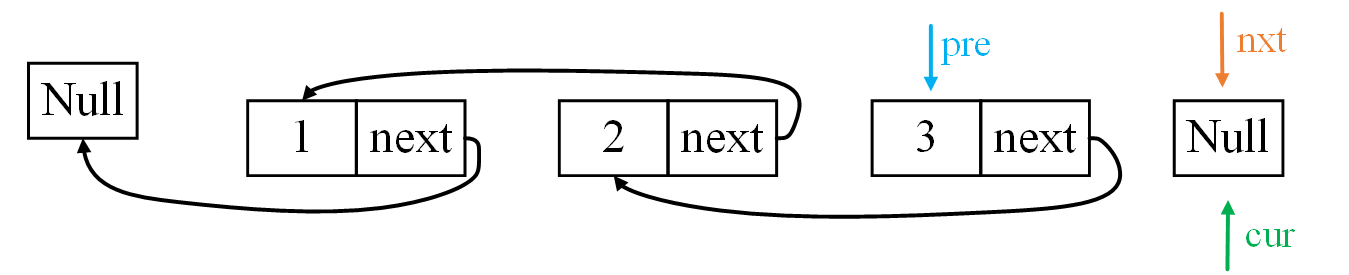

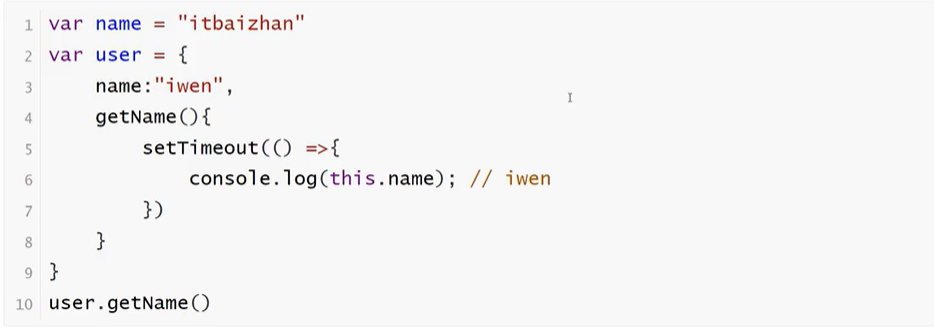

HBM==High Bandwidth Memory 是一款新型的CPU/GPU 内存芯片(即 “RAM”),其实就是将很多个DDR芯片堆叠在一起后和GPU封装在一起,实现大容量,高位宽的DDR组合阵列。先看个平面图:

中间的die是GPU/CPU,左右2边4个小die就是DDR颗粒的堆叠。在堆叠上,现在一般只有2/4/8三种数量的堆叠,立体上最多堆叠4层.

HBM的优势

1. 高带宽:HBM通过宽接口和多通道设计实现了高数据吞吐量。相较于传统的GDDR内存,HBM提供更高的每针带宽,适合处理大规模并行计算任务1。

2. 低功耗:HBM通过减少信号传输路径长度和优化电路设计,降低了功耗。工作电压通常为1.2V或更低,比GDDR显著节能1。

3. 高容量:HBM采用TSV(Through-Silicon Via)技术将多个DRAM单元紧密相连,形成大容量存储器,能够满足高性能计算和图形处理的需求12。

4. 高效封装:HBM采用2.5D封装技术,将DRAM芯片垂直堆叠并通过硅中介层连接到处理器,显著减少了PCB面积,提升了数据传输效率。

HBM的应用场景

HBM主要应用于高性能计算(HPC)、人工智能(AI)、图形处理(GPU)和数据中心等领域。随着AI和大数据的快速发展,对高带宽内存的需求日益增长,HBM因其高带宽、低功耗和高密度的特性,成为这些领域理想的内存解决方案1。

为什么要HBM:

• 更高速,更高带宽

HBM 堆栈没有以物理方式与 CPU 或 GPU 集成,而是通过中介层紧凑而快速地连接,HBM 具备的特性几乎和芯片集成的 RAM一样。

• 更高位宽

HBM 堆栈方式可以实现更多的IO数量,1024位。

HBM推动AI成功

人工智能,云计算,深度学习出现3个算力阶段

第一,早期,AI处理器架构的探讨源于学术界的半导体和体系架构领域,此时模型层数较少,计算规模较小,算力较低。

第二,模型逐渐加深,对算力需求相应增加,导致了带宽瓶颈,即IO问题,此时可通过增大片内缓存、优化调度模型来增加数据复用率等方式解决

第三,云端AI处理需求多用户、高吞吐、低延迟、高密度部署。计算单元剧增使IO瓶颈愈加严重,要解决需要付出较高代价(如增加DDR接口通道数量、片内缓存容量、多芯片互联)

此时,片上HBM(High Bandwidth Memory,高带宽存储器)的出现使AI/深度学习完全放到片上成为可能,集成度提升的同时,使带宽不再受制于芯片引脚的互联数量,从而在一定程度上解决了IO瓶颈。

总结一句话:HBM就是将很多DRAM通过3D技术集成在一个封装内,满足各种计算对高带宽的需求。