文章目录

- 第一讲

- 第二讲

- 第三讲

- 第四讲

- 第五讲

第一讲

1、testbench 没有端口,所以没括号

2、testbench 输入端 之后要变动 所以定义为reg

3、#10 :过10个时间单位 ;’timescale 1ns/10ps 即 1ns 的时间单位 10ps的时间精度

4、reg 型变量赋值的时候 用带箭头的等号“<=”,

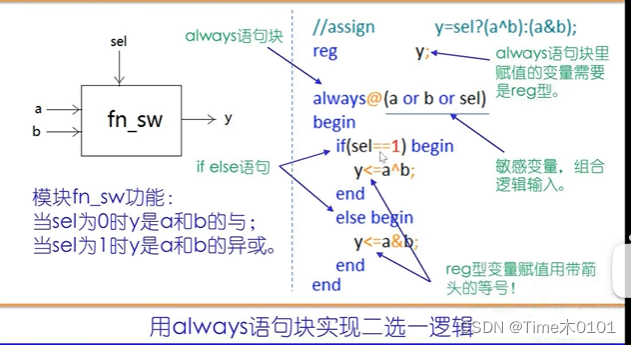

第二讲

1、always@(a or b or sel) 中的a, b, c是敏感变量,输入。有几个输入写几个输入

2、在always 里面赋值饿变量需要是reg型。

3、$stop 系统任务

4、多路选择器

代码:

//四选一逻辑

`timescale 1ns/1ps

module fn_sw_4(a,b,sel,y);

input a;

input b;

input[1:0] sel;

output y;reg y;

always@(a or b or sel)begincase(sel)2'b00:begin y <= a&b;end2'b01:begin y <= a|b;end2'b10:begin y <= a^b;end2'b11:begin y <= ~(a^b);endendcase

endendmodule//-------testbench of fn_sw_4----------

module fn_sw_4_tb;

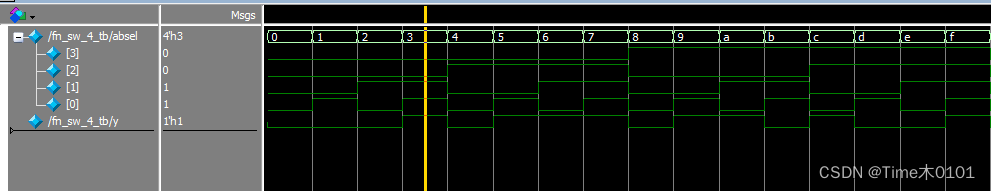

reg[3:0] absel;

fn_sw_4 fn_sw_4(.a(absel[0]),.b(absel[1]),.sel(absel[3:2]),.y(y));initial beginabsel<=0; //先赋初始值#200 $stop;

endalways #10 absel<=absel+1; //每过10ns,absel加一,这样经过16次加一,可以取完四位寄存器所有可能,并观察y的取值

endmodule

仿真结果:

小结:

第三讲

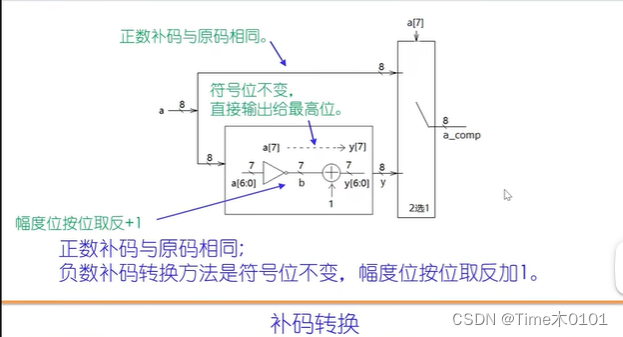

1、补码转换

代码:

//补码转换逻辑

`timescale 1ns/10ps

module comp_conv(a,a_comp);input[7:0] a;

output[7:0] a_comp;wire[6:0] b;//按位取反的幅度位

wire[7:0] y;//负数的补码assign b=~a[6:0];

assign y[6:0]=b+1;//按位取反+1

assign y[7]=a[7];//符号位不变assign a_comp=a[7]==1?y:a;//二选一

//assign a_comp=a[7]?{a[7],~a[6:0]+1}:a;//可替换上面的wire和assign语句

endmodule //----------testbench of comp_conv--------

module comp_conv_tb;

reg[7:0] a_in;

wire[7:0] y_out;

comp_conv comp_conv(.a(a_in),.a_comp(y_out));

initial begin a_in<=0;#3000 $stop;

endalways#10 a_in=a_in+1;

endmodule

2、7段数码管译码器

代码:

//七段码译码器

`timescale 1ns/10ps

module seg_dec(num,a_g);

input[3:0] num;

output[6:0] a_g;//a_g-->{a,b,c,d,e,f,g}reg[6:0] a_g;

always@(num)begincase(num)4'd0: a_g<=7'b111_1110; 4'd1: a_g<=7'b011_0000; 4'd2: a_g<=7'b110_1101; 4'd3: a_g<=7'b111_1100; 4'd4: a_g<=7'b011_0011; 4'd5: a_g<=7'b101_1011; 4'd6: a_g<=7'b101_1111; 4'd7: a_g<=7'b111_0000; 4'd8: a_g<=7'b111_1111; 4'd9: a_g<=7'b111_1011; default: a_g<=7'b000_0001; //中杠endcaseendendmodule//--------test bench of seg_dec---------

module seg_dec_tb;

reg[3:0] num_in;

wire[6:0] a_g_out;

seg_dec seg_dec(.num(num_in),.a_g(a_g_out));

initial begin num_in<=0;#100 $stop;

end always #10 num_in<=num_in+1;

endmodule

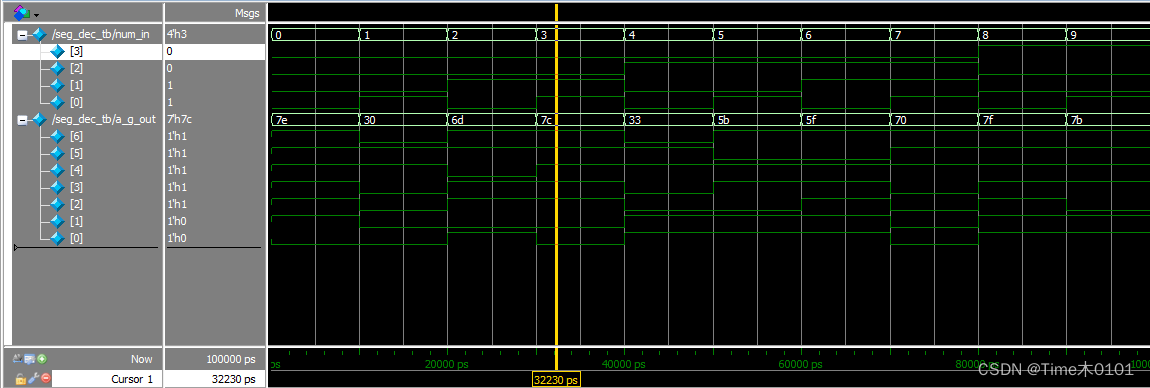

如图:输入3,应该是111_1110,根据波形图是正确的。

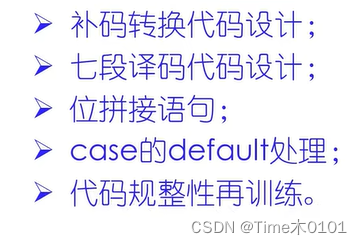

小结:

第四讲

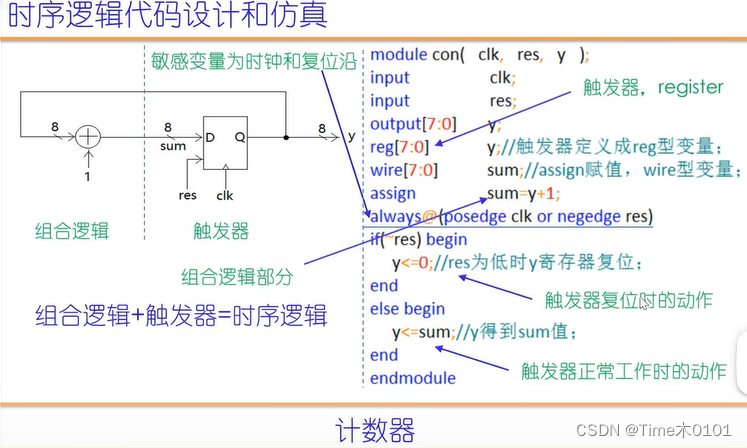

1、计数器

代码:

//计数器

`timescale 1ns/10ps

module counter(clk,res,y);

input clk;

input res;

output[7:0] y;reg[7:0] y;

wire[7:0] sum;//+1运算的结果(1)

assign sum=y+1;//组合逻辑部分(2)always@(posedge clk or negedge res)

if(~res) beginy<=0;

end

else beginy<=sum; //可省略上面(1)(2)语句,y<=y+1;

end

endmodule//--------testbench of counter------

module counter_tb;

reg clk,res;

wire[7:0] y;counter counter(.clk(clk),.res(res),.y(y));initial beginclk<=0;res<=0;#17 res<=1;#6000 $stop;

endalways #5 clk<=~clk;endmodule

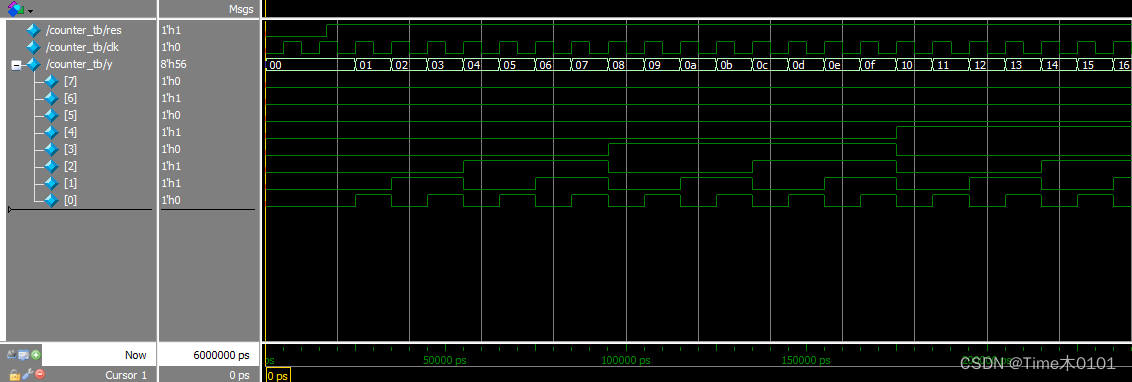

仿真结果:

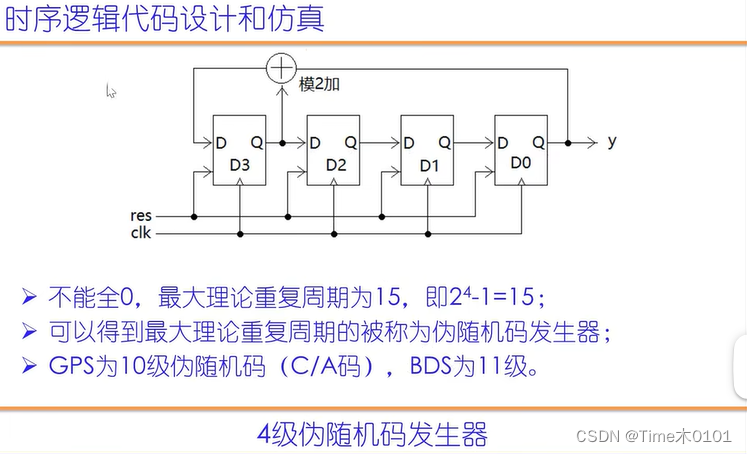

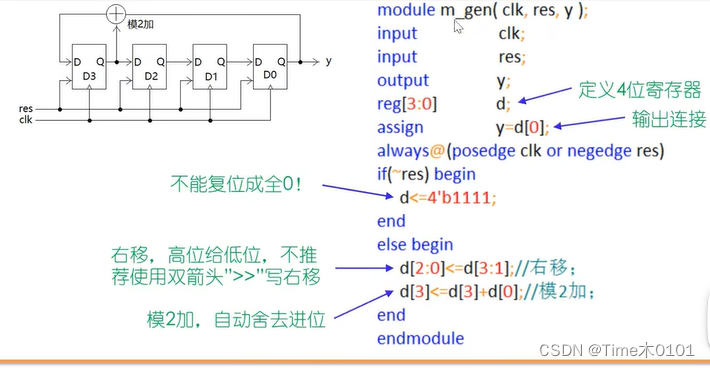

2、4级伪随机码发生器

代码:

//四级伪随机码发生器

`timescale 1ns/10ps

module m_gen(clk,res,y);

input clk;

input res;

output y;reg[3:0] d;

assign y=d[0];always@(posedge clk or negedge res)

if(~res)begind<=4'b1111;

end

else begind[2:0]<=d[3:1]; //右移一位d[3]<=d[3]+d[0]; //模二加

endendmodule//-------testbench of m_gen-------

module m_gen_tb;

reg clk,res;

wire y;

m_gen m_gen(.clk(clk),.res(res),.y(y));initial beginclk=0;res=0;#17 res=1;#600 $stop;

end

always #5 clk=~clk;endmodule

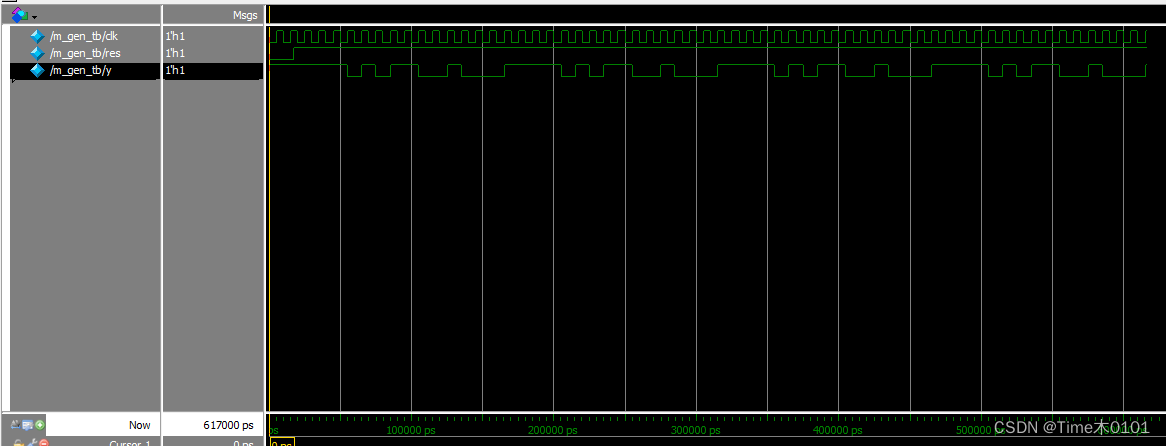

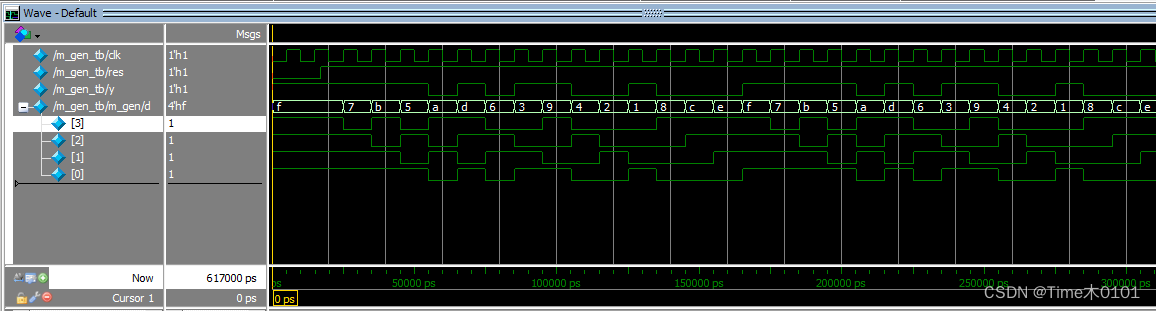

仿真波形图:

小结:

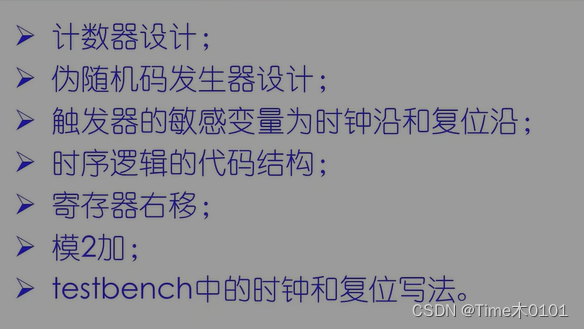

第五讲

1、秒计数器