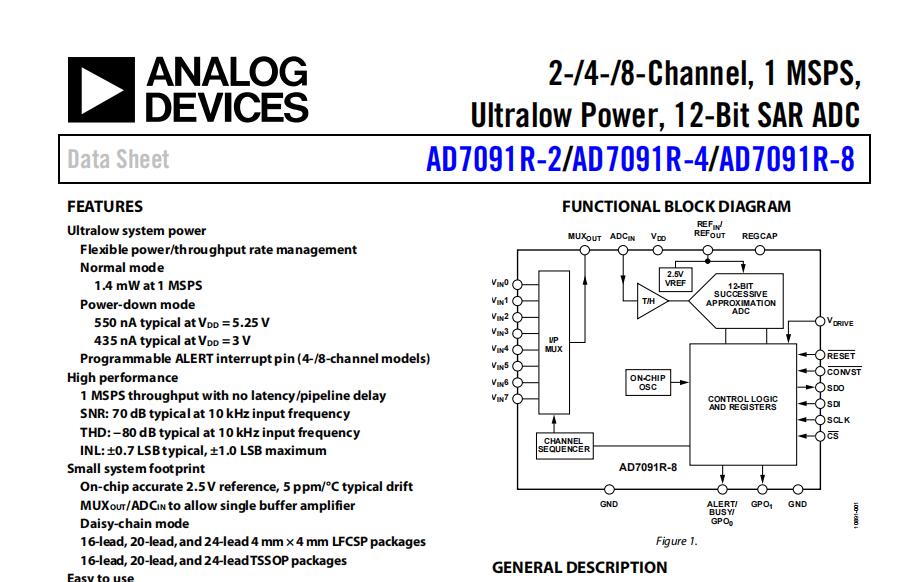

名称:8通道模数转换AD7091驱动代码

软件:QuartusII

语言:Verilog

代码功能:

使用verilog代码设计AD7091R-8驱动代码

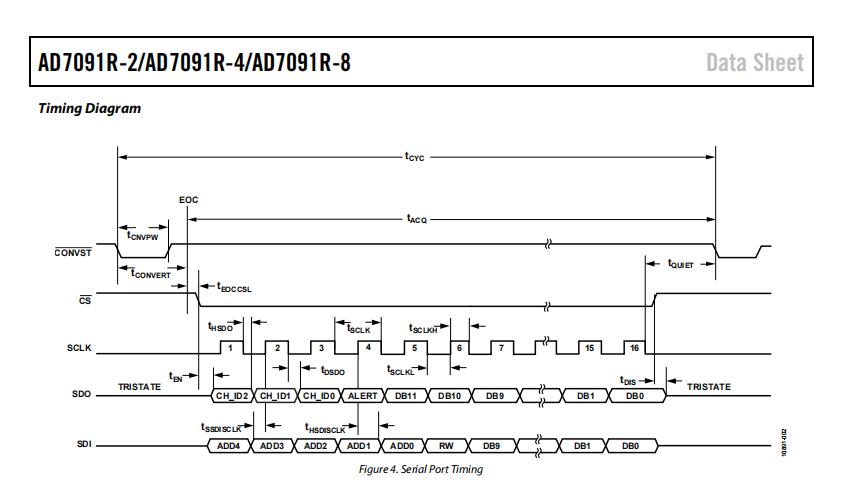

控制接口为SPI接口,实现8通道模数转换,输出8通道数字信号。

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

8通道模数转换AD7091驱动代码(代码在文末付费下载)软件:QuartusII语言:Verilog代码功能: 使用verilog代码设计AD7091R-8驱动代码 控制接口为SPI接口,实现8通道模数转换,输出8通道数字信号。FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com部分代码展示//AD7091驱动module AD7091(input名称:8通道模数转换AD7091驱动代码(代码在文末付费下载)软件:QuartusII语言:Verilog代码功能: 使用verilog代码设计AD7091R-8驱动代码 控制接口为SPI接口,实现8通道模数转换,输出8通道数字信号。FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com芯片手册:AD7091R-2_7091R-4_7091R-8.pdf部分![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=218

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=218

芯片手册:

AD7091R-2_7091R-4_7091R-8.pdf

部分代码展示

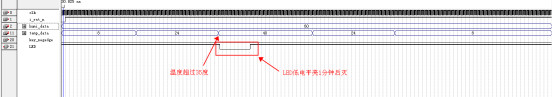

//AD7091驱动 module AD7091( input clk_50M, //input reset_p, output AD_CS, output AD_convst, output AD_sclk,//输出sclk input AD_sdo,//输入sdo output AD_sdi,//输出sdi input AD_alert, output reg [11:0] AD_0, output reg [11:0] AD_1, output reg [11:0] AD_2, output reg [11:0] AD_3, output reg [11:0] AD_4, output reg [11:0] AD_5, output reg [11:0] AD_6, output reg [11:0] AD_7 ); wire reset_p; assign reset_p=0; reg [2:0] state=3'd0; parameter s_idle=3'd0; parameter s_initial=3'd1; parameter s_write=3'd2; parameter s_wait=3'd3; reg [7:0] convst_cnt=8'd0; reg [7:0] write_cnt=8'd0; reg [7:0] wait_cnt=8'd0; //状态机 always@(posedge clk_50M or posedge reset_p) if(reset_p) state<=s_idle; else case(state) s_idle: state<=s_initial; s_initial://初始化状态 if(convst_cnt>=8'd66) state<=s_wait; else state<=s_initial; s_wait: if(wait_cnt>=8'd200) state<=s_write; else state<=s_wait; s_write://读写状态 state<=s_write; default:; endcase always@(posedge clk_50M or posedge reset_p) if(reset_p) wait_cnt<=8'd0; else if(state==s_wait) wait_cnt<=wait_cnt+8'd1; else wait_cnt<=8'd0; //初始化计数400输出66个convst周期 reg [9:0] clk_convst_cnt=10'd0; always@(posedge clk_50M or posedge reset_p) if(reset_p) clk_convst_cnt<=10'd0; else if(state==s_initial) if(clk_convst_cnt>=10'd400) clk_convst_cnt<=10'd0; else clk_convst_cnt<=clk_convst_cnt+10'd1; else clk_convst_cnt<=10'd0; reg convst_initial=1; always@(posedge clk_50M or posedge reset_p) if(reset_p) convst_initial<=1; else if(state==s_initial) if(clk_convst_cnt>10'd200)//400us低电平,400us高电平 convst_initial<=0; else convst_initial<=1; else convst_initial<=1; always@(posedge clk_50M or posedge reset_p) if(reset_p) convst_cnt<=8'd0; else if(state==s_initial) if(clk_convst_cnt>=10'd400) convst_cnt<=convst_cnt+8'd1;//convst计数 else convst_cnt<=convst_cnt; else convst_cnt<=8'd0;