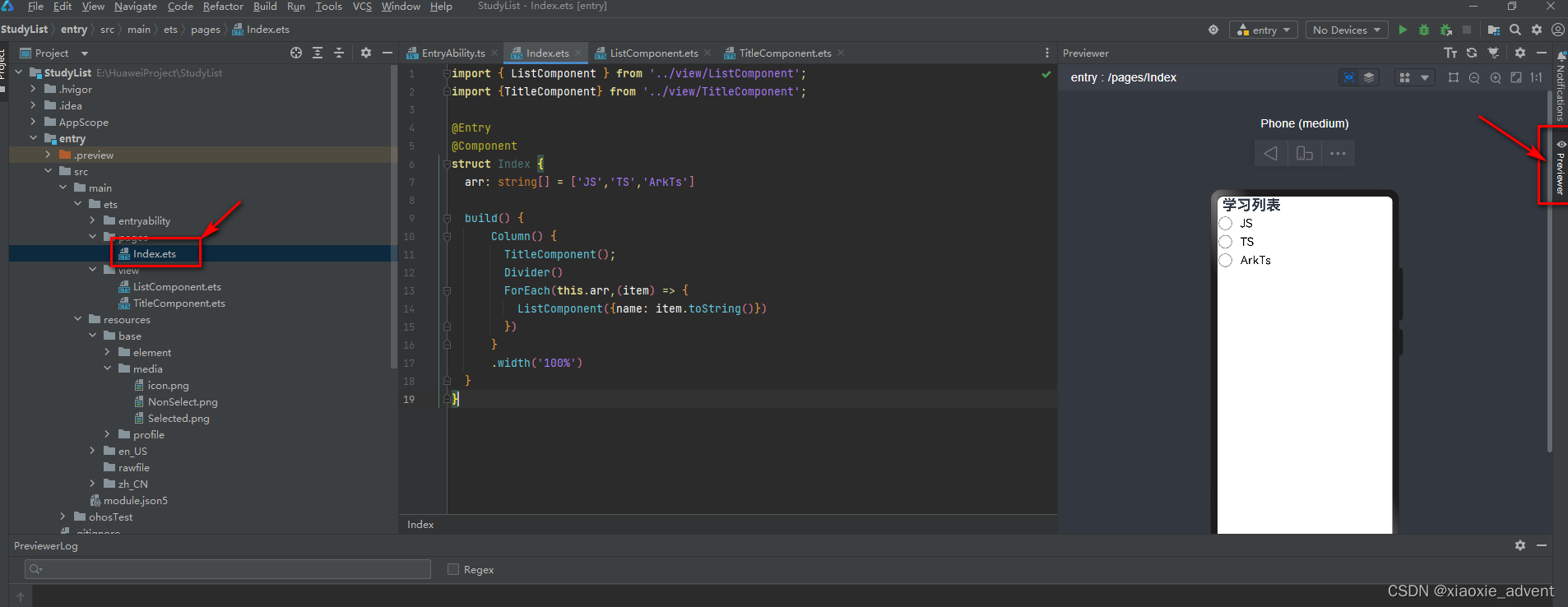

例化MMCM ip核,产生100Mhz,100Mhz并相位偏移180,50Mhz,25Mhz的时钟信号。

例化单口ram,并编写读写控制器,实现32个数据的写入与读出。

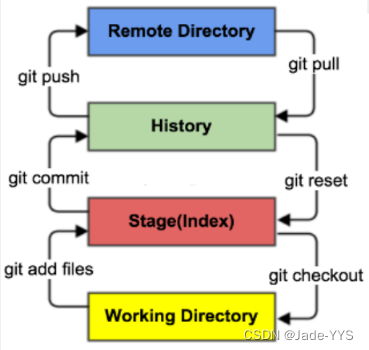

模块框图:

代码:

module ip_top(input wire sys_clk ,input wire sys_rst_n ,output wire [7:0] douta ,output wire clk_100Mhz ,output wire clk_100Mhz_180Phase ,output wire clk_50Mhz ,output wire clk_25Mhz

);// 例化间连�??wire locked ;// wire clk_50Mhz ;

//ila_0 ila_0_inst(

// .clk ( clk_100Mhz ) ,// .probe0 ( clk_100Mhz ) ,

// .probe1 ( clk_100Mhz_180Phase ) ,

// .probe2 ( clk_50Mhz ) ,

// .probe3 ( clk_25Mhz )

//);wire ENA ; wire WEA ; wire [4:0] ADDRA ; wire [7:0] DATA_INA; wire rst_n ;assign rst_n = sys_rst_n && locked ;

clk_wiz_0 clk_wiz_0_inst(.clk_in1 ( sys_clk ) , .resetn ( sys_rst_n ) ,.locked ( locked ) , .clk_out1 ( clk_100Mhz ) ,.clk_out2 ( clk_100Mhz_180Phase ) ,.clk_out3 ( clk_50Mhz ) ,.clk_out4 ( clk_25Mhz )

);ram_wrA ram_wrA_inst(.sys_clk ( clk_50Mhz ) ,.sys_rst_n ( rst_n ) ,.ENA ( ENA ) ,.WEA ( WEA ) ,.ADDRA ( ADDRA ) ,.DATA_INA ( DATA_INA )

);blk_mem_gen_0 blk_mem_gen_0_inst(.clka ( clk_50Mhz ) , .ena ( ENA ) , .wea ( WEA ) , .addra ( ADDRA ) , .dina ( DATA_INA ) , .douta ( douta )

);endmodule

module ram_wrA (input wire sys_clk ,input wire sys_rst_n ,output reg ENA ,output reg WEA ,output wire [4:0] ADDRA ,output wire [7:0] DATA_INA

);parameter DATA_NUM = 32 ;reg [4:0] cnt_wr ; // 读写计数器。always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_wr <= 5'd0 ;else if(ENA && (cnt_wr == DATA_NUM - 1))cnt_wr <= 5'd0 ;else if(ENA)cnt_wr <= cnt_wr + 1'b1 ;else cnt_wr <= 5'd0 ;end// output reg ENA ,always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) ENA <= 1'b0 ;elseENA <= 1'b1 ;end// output reg WEA ,always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) WEA <= 1'b1 ;else if(cnt_wr == DATA_NUM - 1)WEA <= ~WEA ;end// output wire [4:0] ADDRA ,// output wire [4:0] DATA_INA assign ADDRA = cnt_wr ;assign DATA_INA = {3'b000,cnt_wr} ;endmodule

`timescale 1ns/1ns

module test();reg sys_clk ;reg sys_rst_n ;wire [7:0] douta ;wire clk_100Mhz ;wire clk_100Mhz_180Phase ;wire clk_50Mhz ;wire clk_25Mhz ;

ip_top ip_top_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.douta ( douta ) ,.clk_100Mhz ( clk_100Mhz ) ,.clk_100Mhz_180Phase ( clk_100Mhz_180Phase ) ,.clk_50Mhz ( clk_50Mhz ) ,.clk_25Mhz ( clk_25Mhz )

);parameter CYCLE = 20 ;initial beginsys_clk = 1'b1 ;sys_rst_n <= 1'b0 ;#( CYCLE * 10 ) ;sys_rst_n <= 1'b1 ;#(CYCLE * 3000) ;$stop ;endalways #( CYCLE / 2 ) sys_clk = ~sys_clk ;endmodule// `timescale 1ns/1ns

// module test();

// reg sys_clk ;

// reg sys_rst_n ;// wire clk_100Mhz ;

// wire clk_100Mhz_180Phase ;

// wire clk_50Mhz ;

// wire clk_25Mhz ;// ip_top ip_top_inst(

// .sys_clk ( sys_clk ) ,

// .sys_rst_n ( sys_rst_n ) ,// .clk_100Mhz ( clk_100Mhz ) ,

// .clk_100Mhz_180Phase ( clk_100Mhz_180Phase ) ,

// .clk_50Mhz ( clk_50Mhz ) ,

// .clk_25Mhz ( clk_25Mhz )

// );// parameter CYCLE = 20 ;// initial begin

// sys_clk = 1'b1 ;

// sys_rst_n <= 1'b0 ;

// #( CYCLE * 10 ) ;

// sys_rst_n <= 1'b1 ;

// #(CYCLE * 3000) ;

// $stop ;

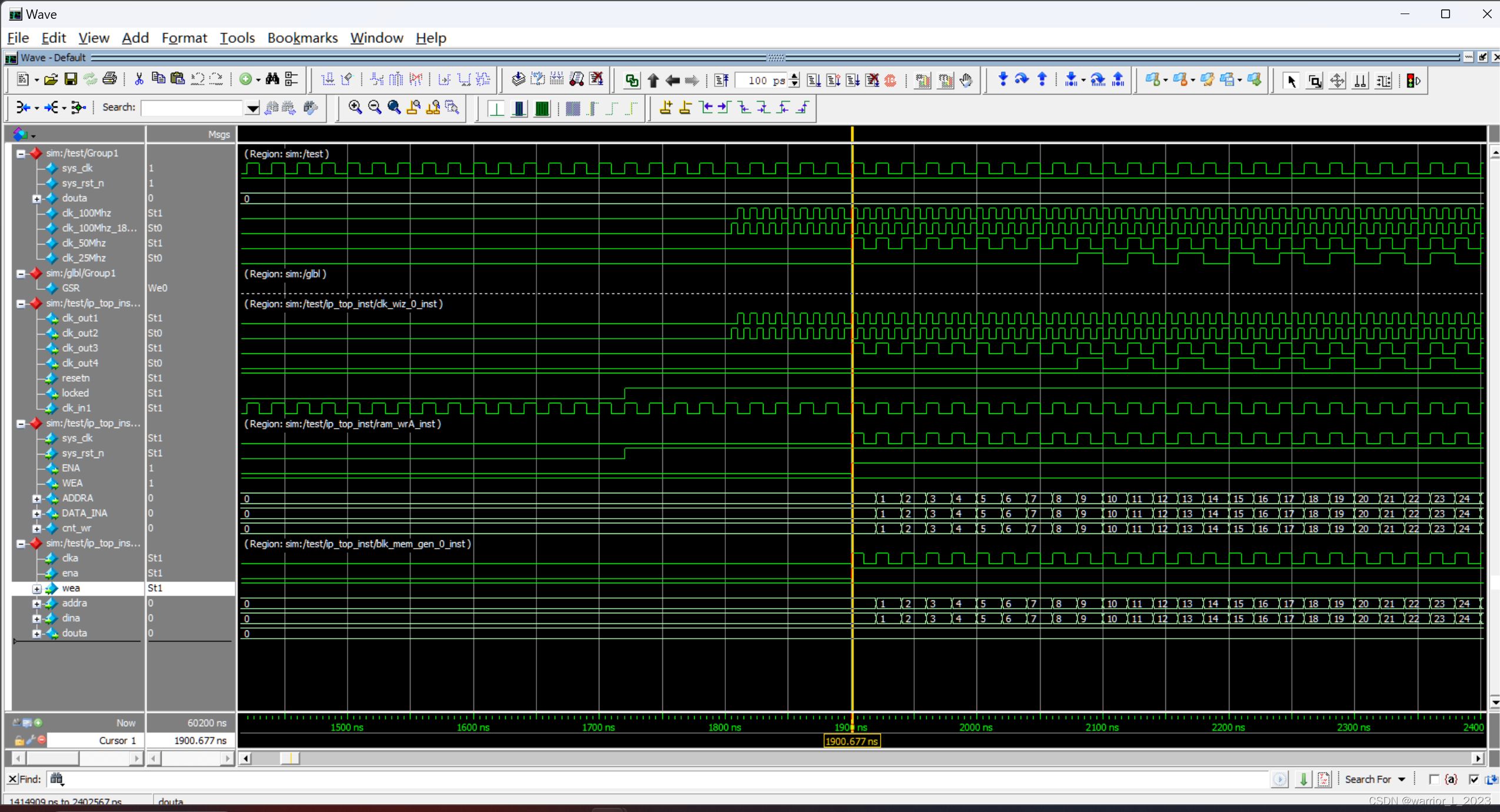

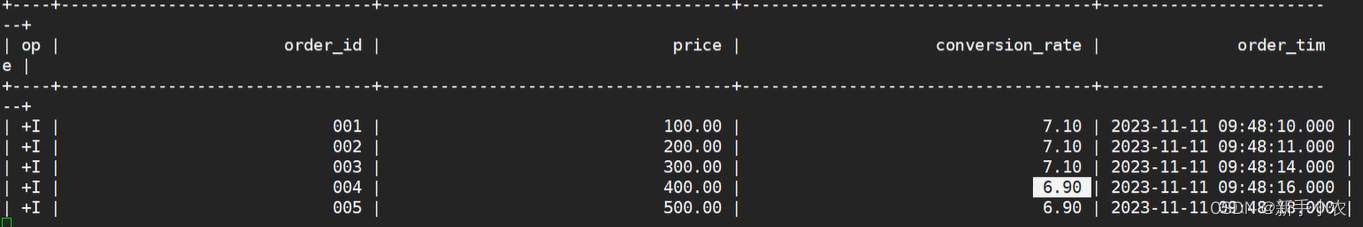

// end// always #( CYCLE / 2 ) sys_clk = ~sys_clk ;// endmodule时序图:

仿真: