文章目录

- 一、锁存器简介

- 二、verilog源码

- 三、综合及仿真结果

一、锁存器简介

本文介绍数字逻辑电路中一种常用的基础时序逻辑电路-锁存,顾名思义,它的功能就是将输入在控制信号有效时透明传输到输出端,当控制信号无效时,输出值保持不变。它具有记忆和存储功能。这是它区别组合逻辑的基本点。

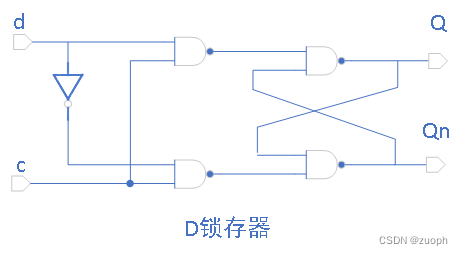

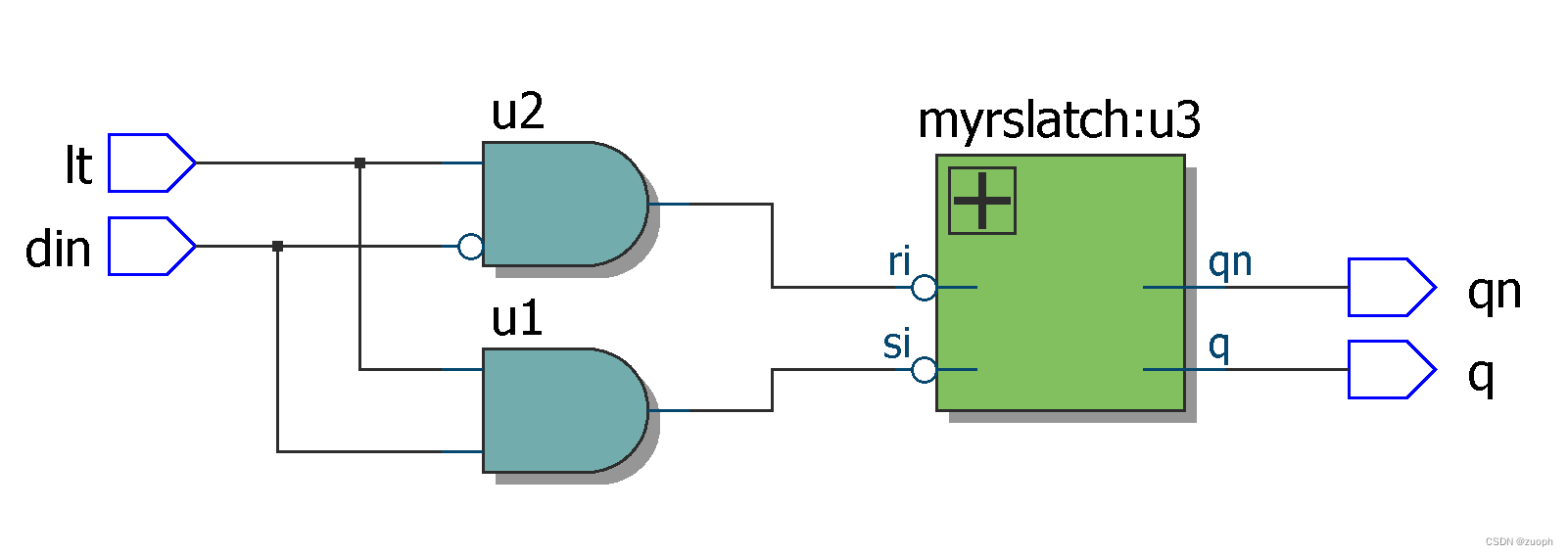

下图是锁存器的门级结构图。它由两个与非门、一个反相器及后级的RS锁存器构成。

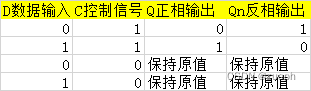

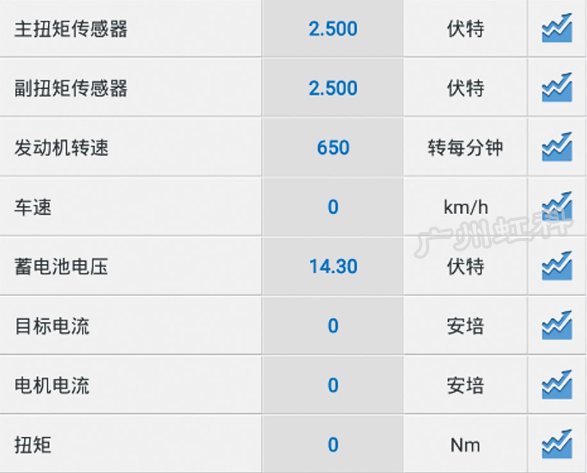

锁存器的逻辑真值表如下表所示:

锁存器通常用下面的符号描述:

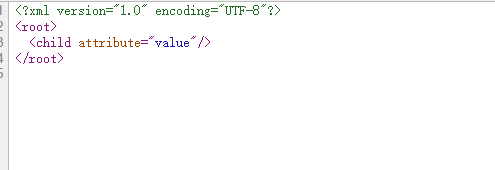

二、verilog源码

// module implements d-latchmodule dlatch (lt, din, q, qn);input lt, din;output q, qn;wire ri, si;nand u1(si, din, lt);nand u2(ri, ~din, lt);rslatch u3(si, ri, q, qn);

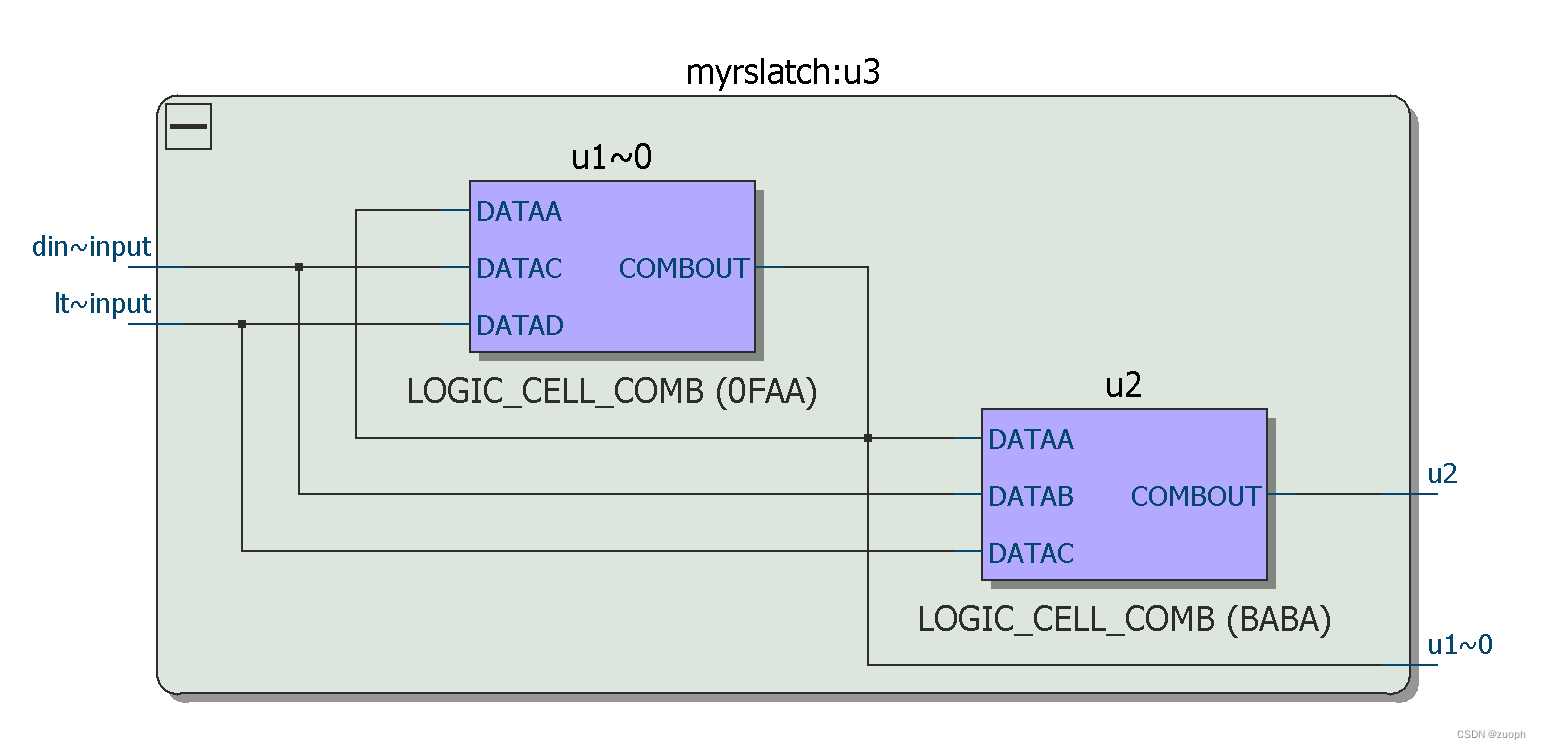

endmodule // dlatchmodule rslatch(si, ri, q, qn);input si, ri;output q, qn;nand u1(q, si, qn);nand u2(qn, ri, q);

endmodule // rslatch三、综合及仿真结果

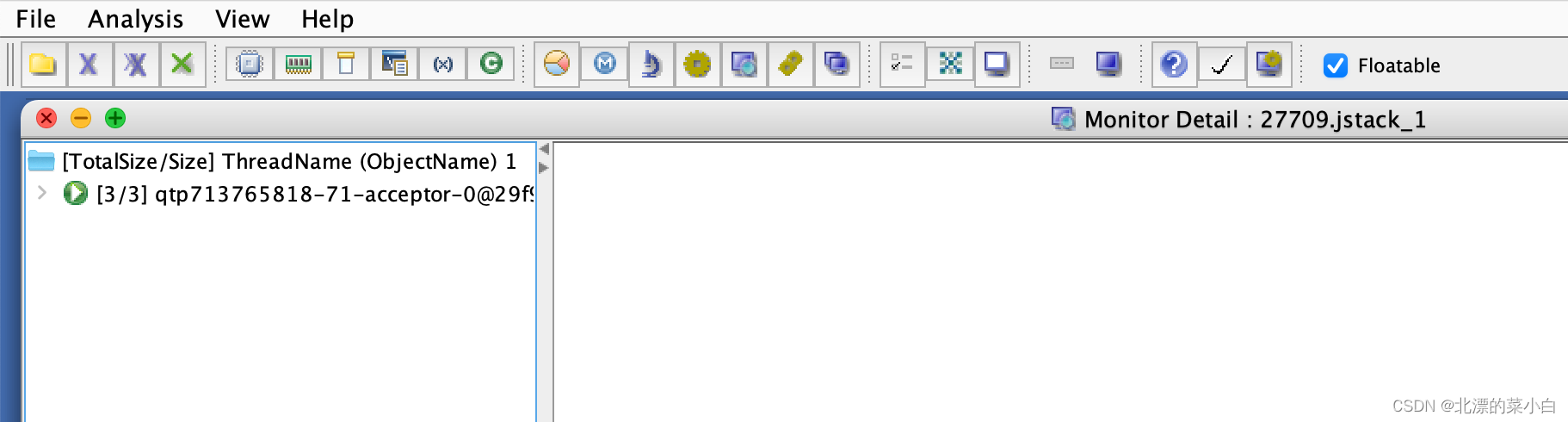

本文使用的综合工具为quartus13.1,软件的使用请搜索相关教程。综合生成的RTL及门级电路如下。

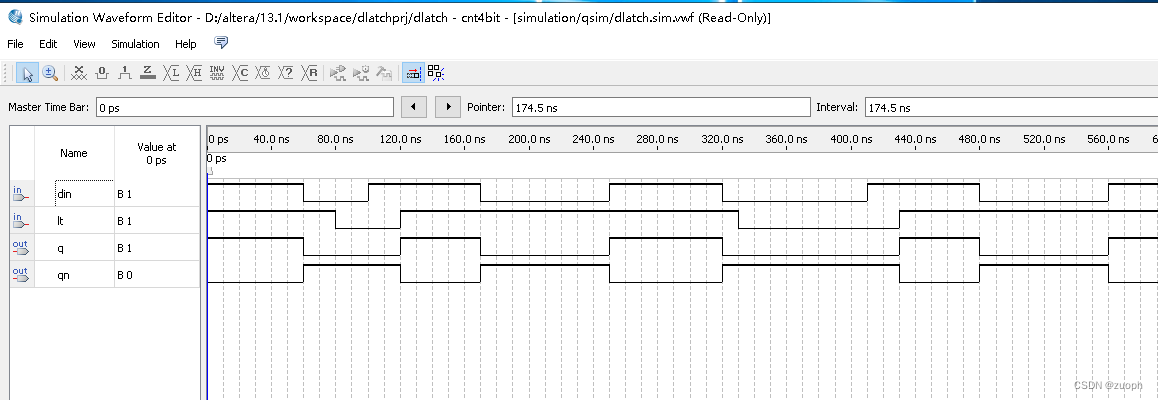

使用quartus自带波形编辑器进行仿真,最终输出波形如下:

你也可以试着修改上述的输入值或者添加更多的输入值进行试验,观察仿真结果是否和你预期的一致!

转载请注明出处!

![[ 云计算 | AWS 实践 ] 基于 Amazon S3 协议搭建个人云存储服务](https://img-blog.csdnimg.cn/567cd89250e149aab75d191644421ffb.png)