- RAM — Random Access Memory 随机访问存储器

—指定某一存储单元地址的时候,存储单元的读取速度并不会因为存储单元的物理位置改变

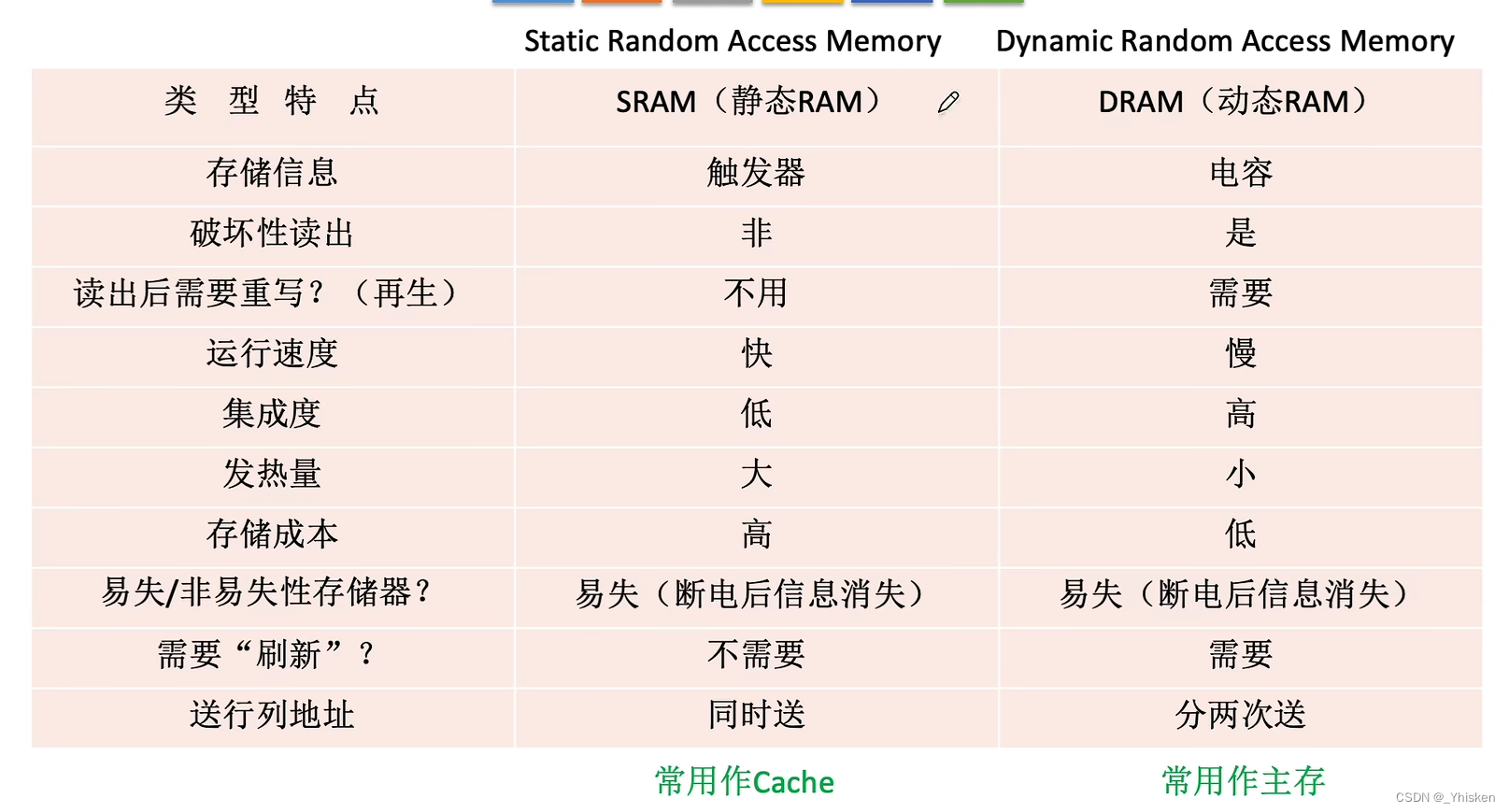

- SRAM即为 Static RAM 静态随机访问存储器 — 用于主存

- DRAM即为 Dynamic RAM 动态随机访问存储器 — 用于Cache

一、SRAM和DRAM的特性差异

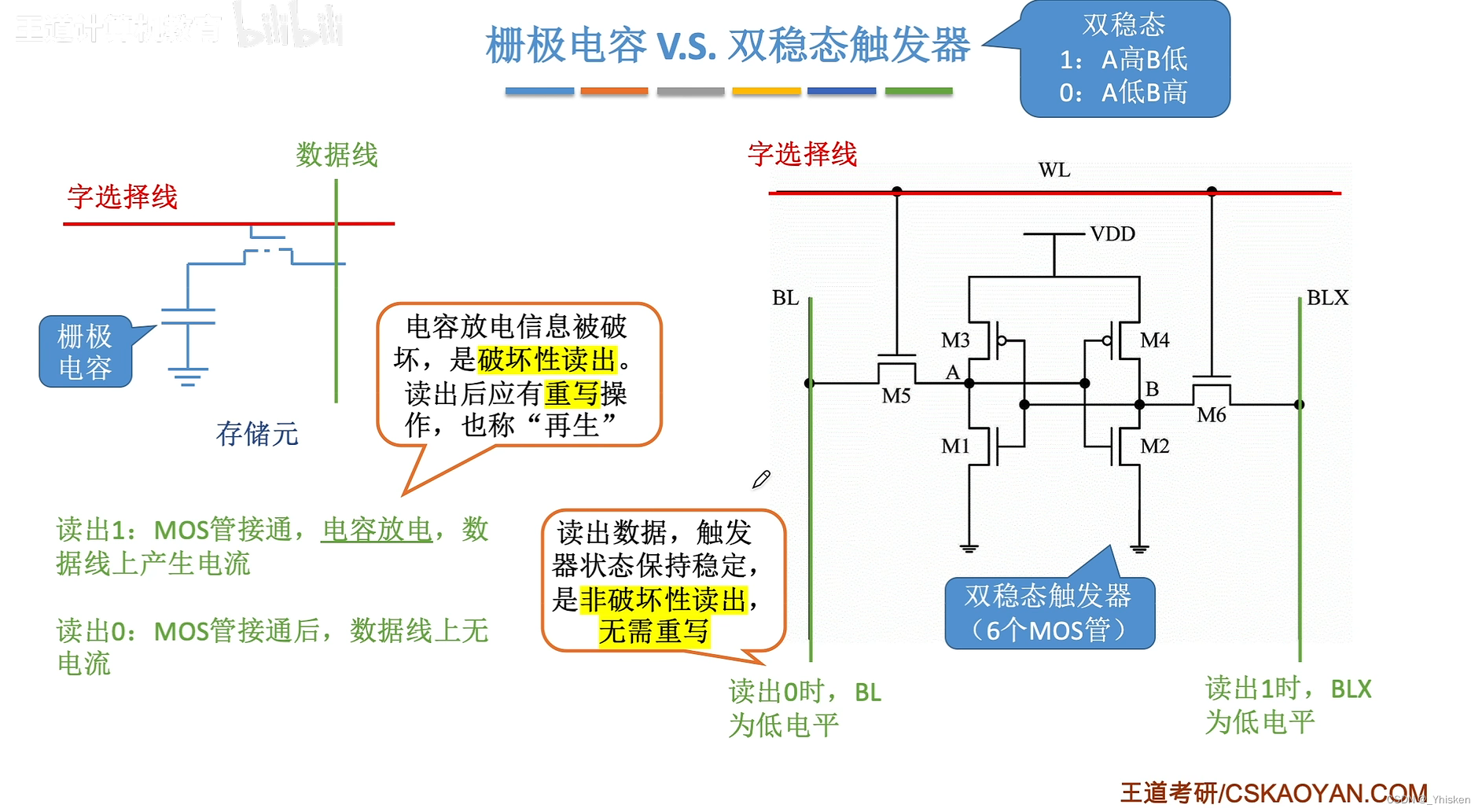

DRAM采用栅极电容存储二进制0/1,线端是否有电荷流出代表存储的是1还是0。输出电荷后原本的电容没有电荷了,这称之为破坏性读出,所以还需要进行重写操作。

SRAM采用双稳态触发器存储二进制0/1(包含6个MOS管),A端高电平B端低电平代表写入1,反正代表写入0。左线输出低电平代表输出0,右线输出低电平代表输出1。 与栅极电容不同,双稳态触发器则没有破坏性读出的问题,因此SRAM的读写速度会更快。

其次,观察栅极电容和双稳态触发器电路的复杂程度和MOS管数量,我们可以得到以下结论。

| 栅极电容 DRAM | 双稳态触发器 SRAM | |

| 功耗 | 小 | 大 |

| 相同空间集成度 | 高 | 低 |

| 成本 | 低 | 低 |

二、DRAM的刷新

1.为什么刷新

栅极电容有有一个问题,电容存储的电荷只能维持2ms,也就是说我们每2ms之内,就必须给电容进行一次充电,也就是进行刷新,使得存储的信息不会消失。

而双稳态触发器则没有刷新问题。

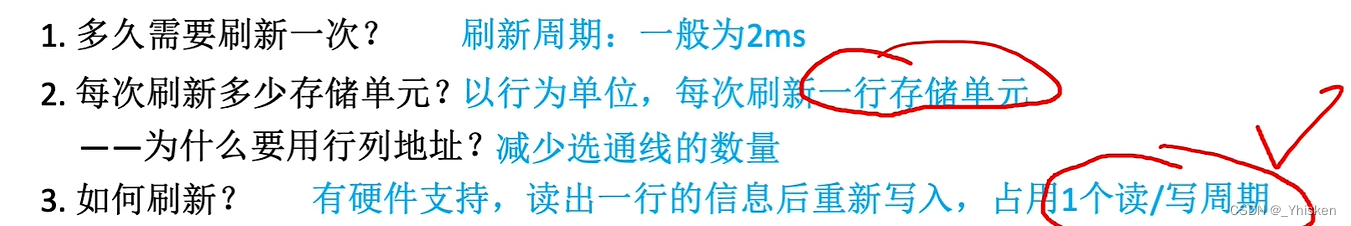

2.刷新规则

3.刷新时机

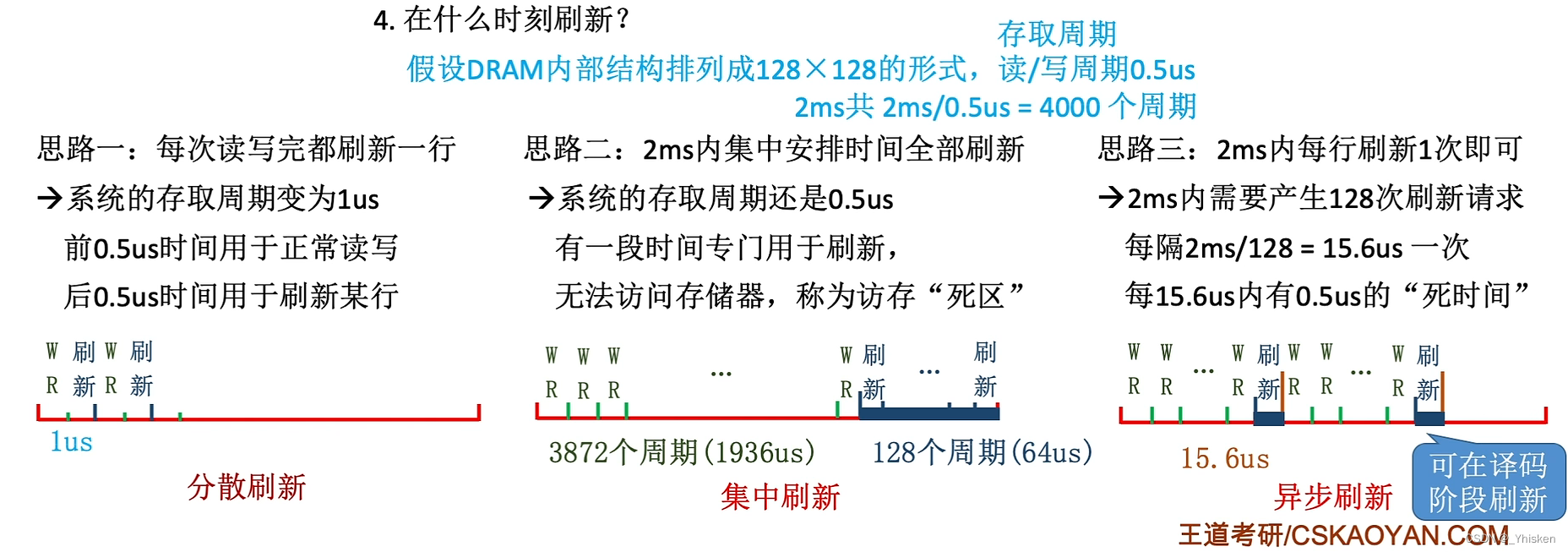

假设DRAM的存取周期位0.5μs,内部结构128x128,那么一个刷新周期内,存储器可以进行4000个存取周期。则我们要在2ms内把128行都刷新一遍。分为三种思路

(1)分散刷新

每一个存取周期之后都刷新一次,存取周期变为1μs,可以刷新2000次,足够刷新128行很多次。

(2)集中刷新

前3872个周期进行存取周期,剩下的128个周期集中进行刷新,而剩下这128个周期的时间是不可以存取的,无法访问存储器,所以被称为死区。

(3)异步刷新

把128次刷新分摊到2ms内,也就是2ms/128 = 15.6μs,也就是说我们每隔15.6μs刷新就可以了,那么每15.6μs,有15.1μs存取,0.5μs的时间刷新,也就是说有0.5μs的死区,在实际操作中,我们可以在CPU不访问存储器的一段时间内进行刷新,比如译码阶段。

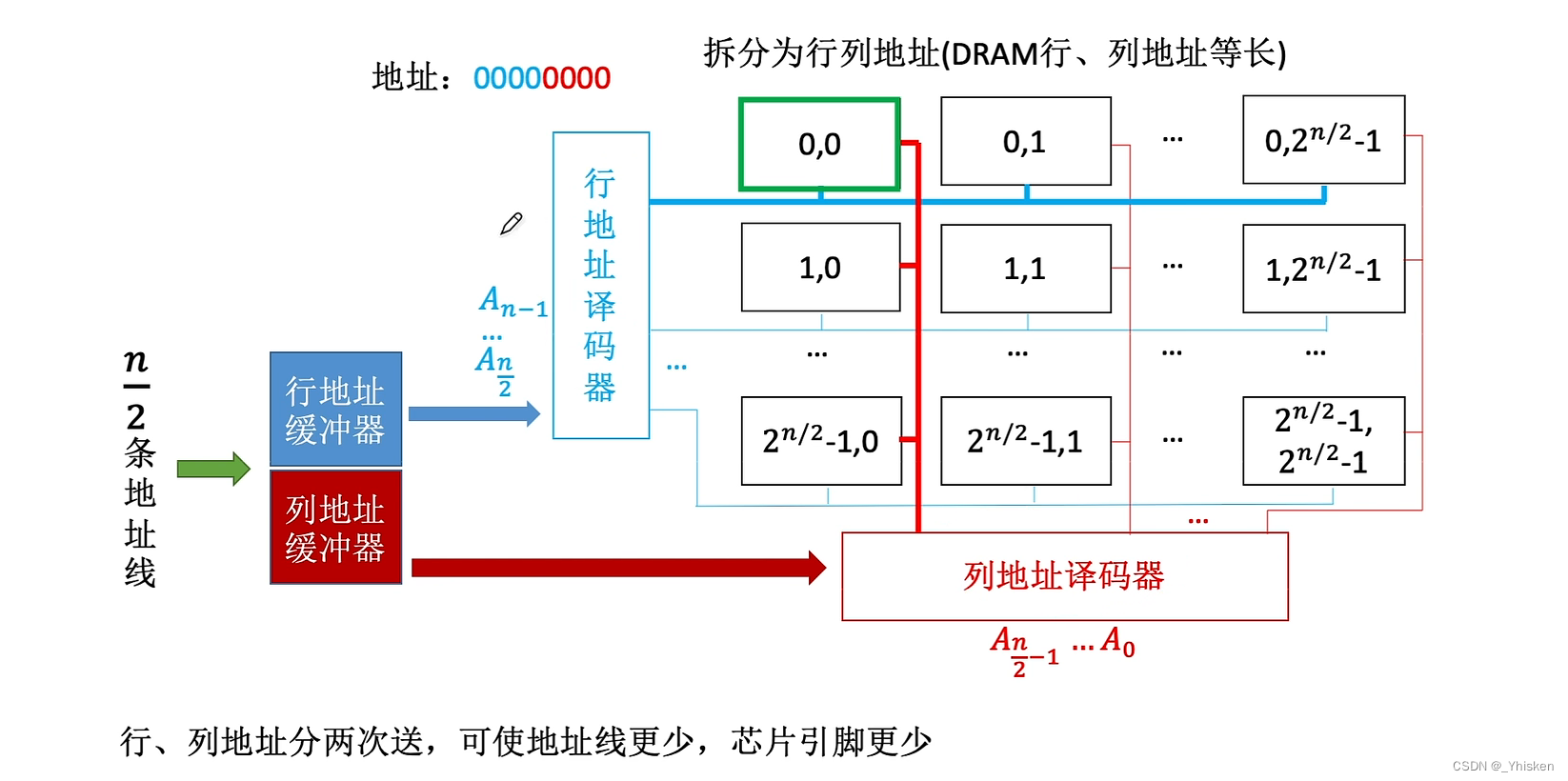

三、DRAM的地址线复用

我们上篇提到了存储器的地址是一个个存储单元的地址,如果有20位的地址,那么就要有2^20,也就是1m的选通线,显然在工程上实现是非常困难的。

因此我们通常把译码器拆分成行地址译码器和列地址译码器。 也就是把存储单元从一维展至二维。

如果是8位地址,那么一维排列的需要2^8 = 256根选通线,而二维排列只需要2 * 2^4 =32根选通线即可。

给出8位地址,00000000,左边一次性读入译码器选择第一根选通线。右边则是拆分成0000 0000行地址和列地址分别送给行列地址译码器,每个存储单元都是两个选通线都被选通才可以被读出。

在SRAM中,如果给出八位地址0000 0000,则行列地址是同时被输给行列地址译码器的。也就是说有多少位地址,就要提供给多少根地址线给译码器。

在SRAM中,如果给出八位地址0000 0000,则行列地址是同时被输给行列地址译码器的。也就是说有多少位地址,就要提供给多少根地址线给译码器。

但是DRAM则不同,DRAM存储容量一般比较大,所需的地址线较多,所以我们DRAM一般会采用地址线复用来把地址线数量减半。简单地说,就是将行列地址分两次送到行列地址缓冲区,再送到行列地址译码器。先送4位行地址,再送4位列地址,所以只需要4根地址线即可。同时,芯片引脚也减少一半。