(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

频率计可以采集外部周期信号的频率,当然实现方法有很多种,这儿我们用FPGA采样计数来实现。

如果用FPGA采样计数实现频率计,那FPGA的采样频率一定要远大于输入信号的频率。这个从直观上是很明确的,你不可能用低频率采样高频信号,就如拿砖头取打天上的飞机,根本打不到的。用相近频率采集输入信号也不可以,因为非常容易错过采集信号的跳变沿,漏过很多采样的信号;只要采样频率远远大于采集信号的频率,才能不会漏过采集信号的跳变细节,得到近似的频率值。

为什么我们不敢保证一定能得到外部输入信号的准确频率值,因为输入信号和FPGA的系统时钟是异步信号,FPGA采集的点有可以巧合错过一个跳变沿,所以我们设计的频率计会有1-2个时钟周期的误差.这个误差可以通过长时间的采集求平均值来减小。

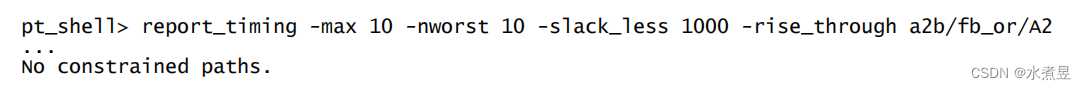

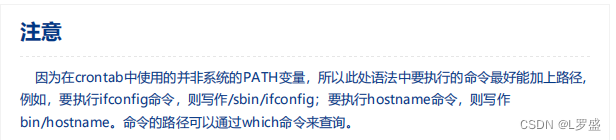

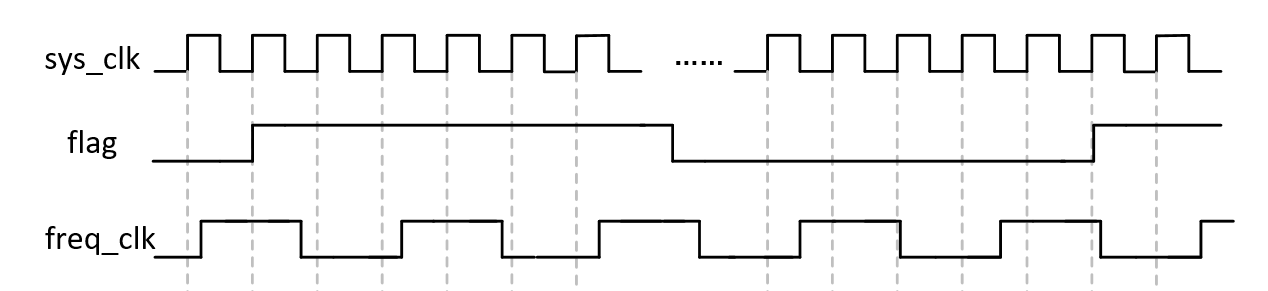

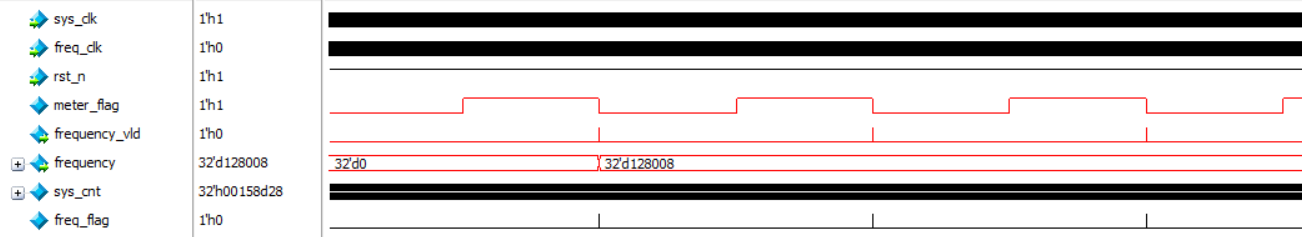

如下所示是FPGA实现频率计的波形示意图,sys_clk是系统时钟,freq_clk是要采集的时钟,flag是设定时间段进行freq_clk时钟数的统计。建议将flag设置成2幂次方秒,这样直接将计数值右移即可,避免了除法的运算。

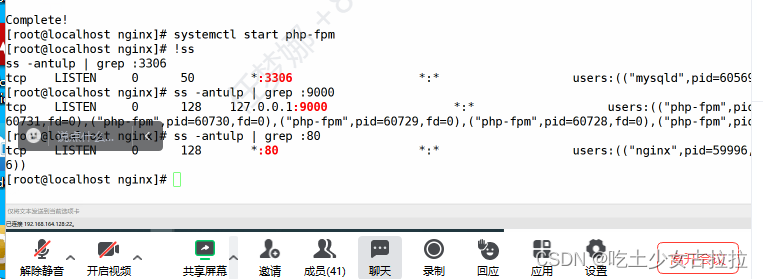

用系统时钟sys_clk采集输入时钟freq_clk,所以要先把freq_clk同步到sys_clk时钟域,再进行时钟数的统计。所以FPGA的设计也是非常简单的。这里sys_clk时钟频率设置为1MHz,主要是为了减少计数值,方便快速仿真。

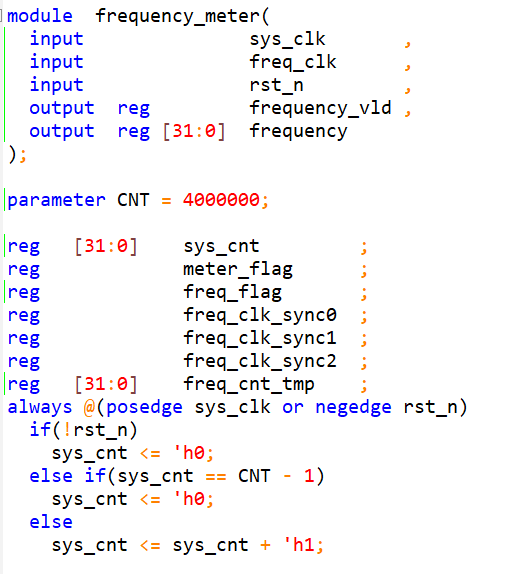

设置了一个参数CNT=4000000,就是4秒的时间进行频率计数,然后停4秒,再进行4秒的频率计数,以此反复,用meter_flag进行标识。

freq_flag用来标识采样点,完成输入周期信号freq_clk到sys_clk的同步。

在meter_flag拉高的时候,对freq_clk进行计数,通过采集freq_clk的上升沿,最终得计数值通过右移2位实现除4的操作。

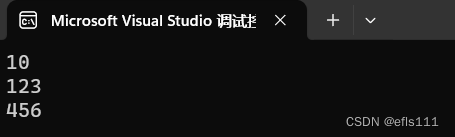

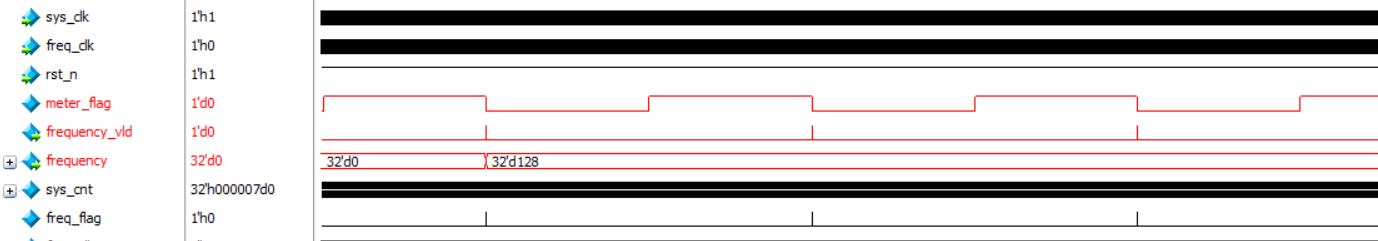

在仿真文件中设置freq_clk是128Hz,仿真结果是128,结果正确。

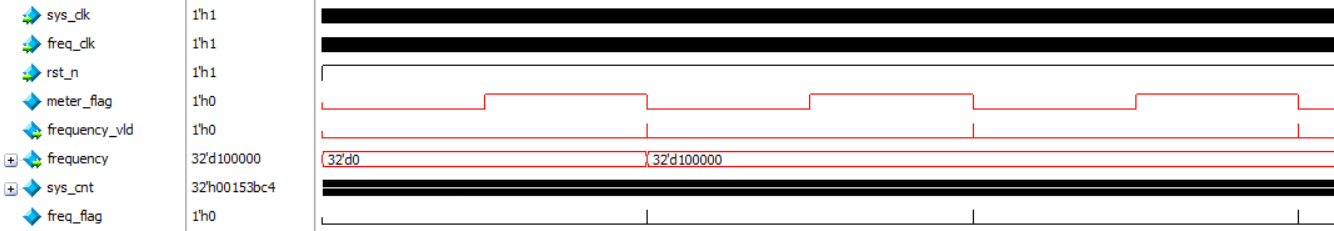

设置freq_clk是100KHz,仿真结果是100_000,结果正确。

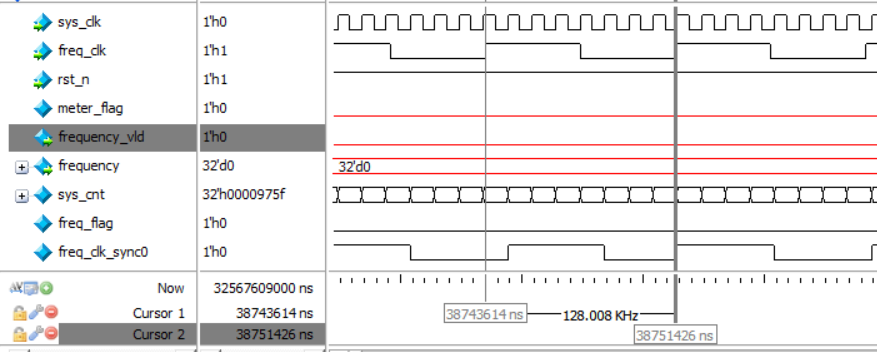

设置freq_clk是128KHz,仿真结果是128.008,有8个时钟的偏差,原因一是128KHz频率和1MHz比已经相差不大了,而且128KHz不是1MHz的整数倍,所以测量可能就会有偏差的。

还有一个重要的原因就是仿真产生的时钟周期freq_clk不是刚刚好的128KHz,可能会有偏差。我们测量一下freq_clk的频率,确实是128008Hz。

这节课只是简单的介绍频率计的FPGA实现,如果要提高频率计的精度,有多种方法可以改进,比如用两个计数器,一个上升沿计数,一个下降沿计数,相加求平均;再比如将N个连续的频率值相加求平均等等,有兴趣的读者可以自己设计来试一下。