目录

一、语句优化

1.1 if与case

1.1.1 条件语句避免出现锁存器

1.1.2 if与case语句综合效果的差异

1.2 阻塞赋值与非阻塞赋值

1.3 算法改进

1.3.1 算法改进提升速度

1.3.2 算法改进缩小面积

二、布线优化

2.1 热点

2.2 瓶颈

2.3 广播

三、总结

一、语句优化

1.1 if与case

1.1.1 条件语句避免出现锁存器

在If或case语句中,必须列举出所有可能的条件分支,并给所有的输出信号赋值, 否则综合时就会出现不期望的锁存器(而非多路选择器),这相当于在纯组合逻辑中出现了时序逻辑,是无法综合的(通常综合器会对不期望产生的锁存器发出警告)。

简单说就是if要记得写else,case要记得写default。

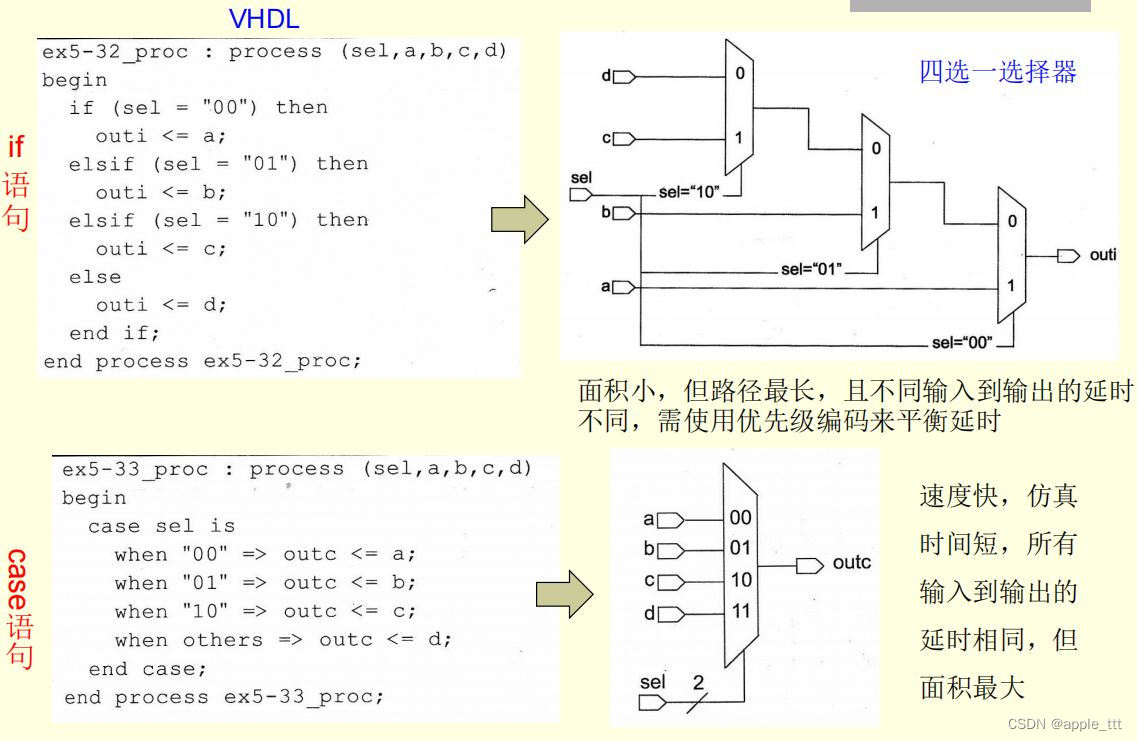

1.1.2 if与case语句综合效果的差异

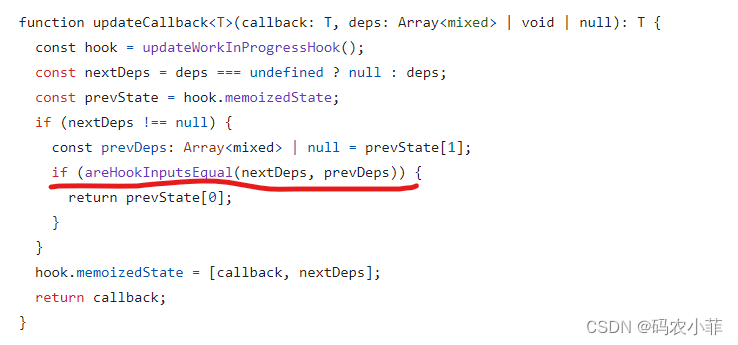

1.2 阻塞赋值与非阻塞赋值

- 阻塞赋值(不适合时序逻辑):按顺序执行语句,执行完块才结束。容易产生RTL级仿真与门级仿真不一致、信号间的竞争冒险等问题。

- 非阻塞赋值(适合时序逻辑):块结束时同时执行各语句赋值操作,不会产生冲突。

1.3 算法改进

1.3.1 算法改进提升速度

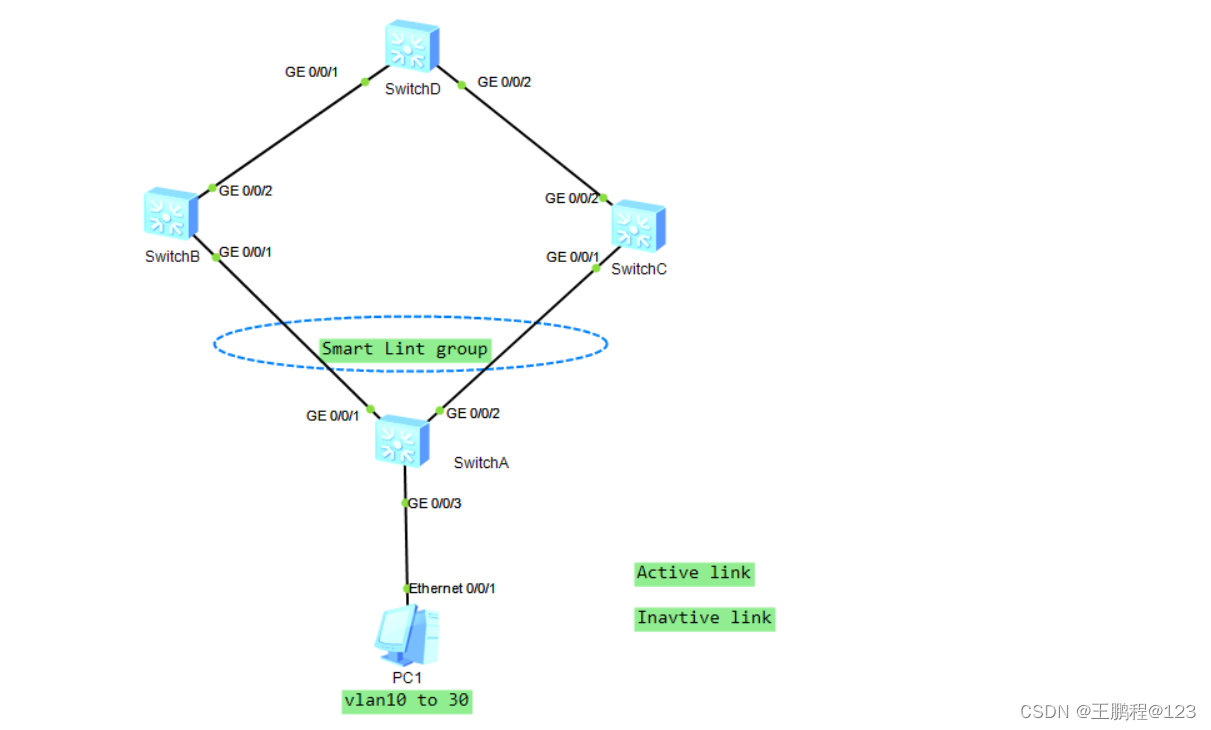

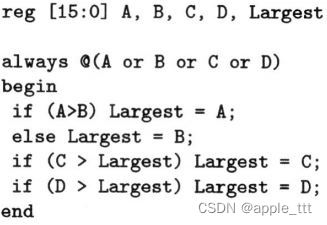

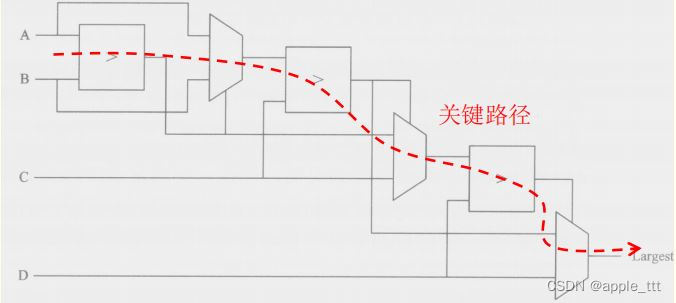

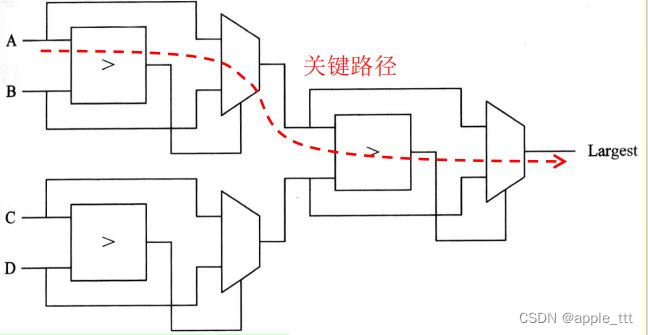

这里我们举一个简单的例子,我们需求是比较A、B、C、D四个输入,找到其中最大的一个作为输出Largest 。

方法一:递进法。逻辑深度为3个比较器和3个选择器,关键路径长,不同的输入到输出的延时不同

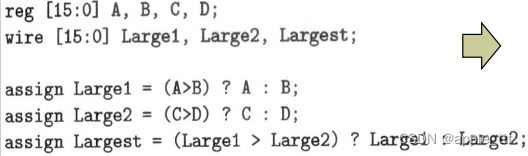

方法二:二分法,逻辑深度为2个比较器和2个选择器,关键路径短,速度比递进法提高了近30%,而所用部件总数未变。

1.3.2 算法改进缩小面积

假设我们的需求是:选择两个乘积之一

wire [15:0] A,B,C;

wire [7:0] In1,In2,In3;

wire MultSelect;assign A = In1 * In2;

assign B = In1 * In3;

assign C = MultSelect ? A : B;方案2:先根据MultSelect选择In2还是In3,然后与In1相乘,可得到相同的积到C。只需要1个8位乘法器和1个8位二选一选择器,面积比方案1小了很多。

wire [15:0] C;

wire [7:0] In1,In2,In3,InSelect;

wire MultSelect;assign InSelect = MultSelect ? In2 : In3;

assign C = In1 * InSelect;对于面积较大的复杂单元(加法器、乘法器、移位寄存器、选择器、比较器、有限状态机等),设计时可通过算法改进或结构优化来减少其使用数量和复杂度。

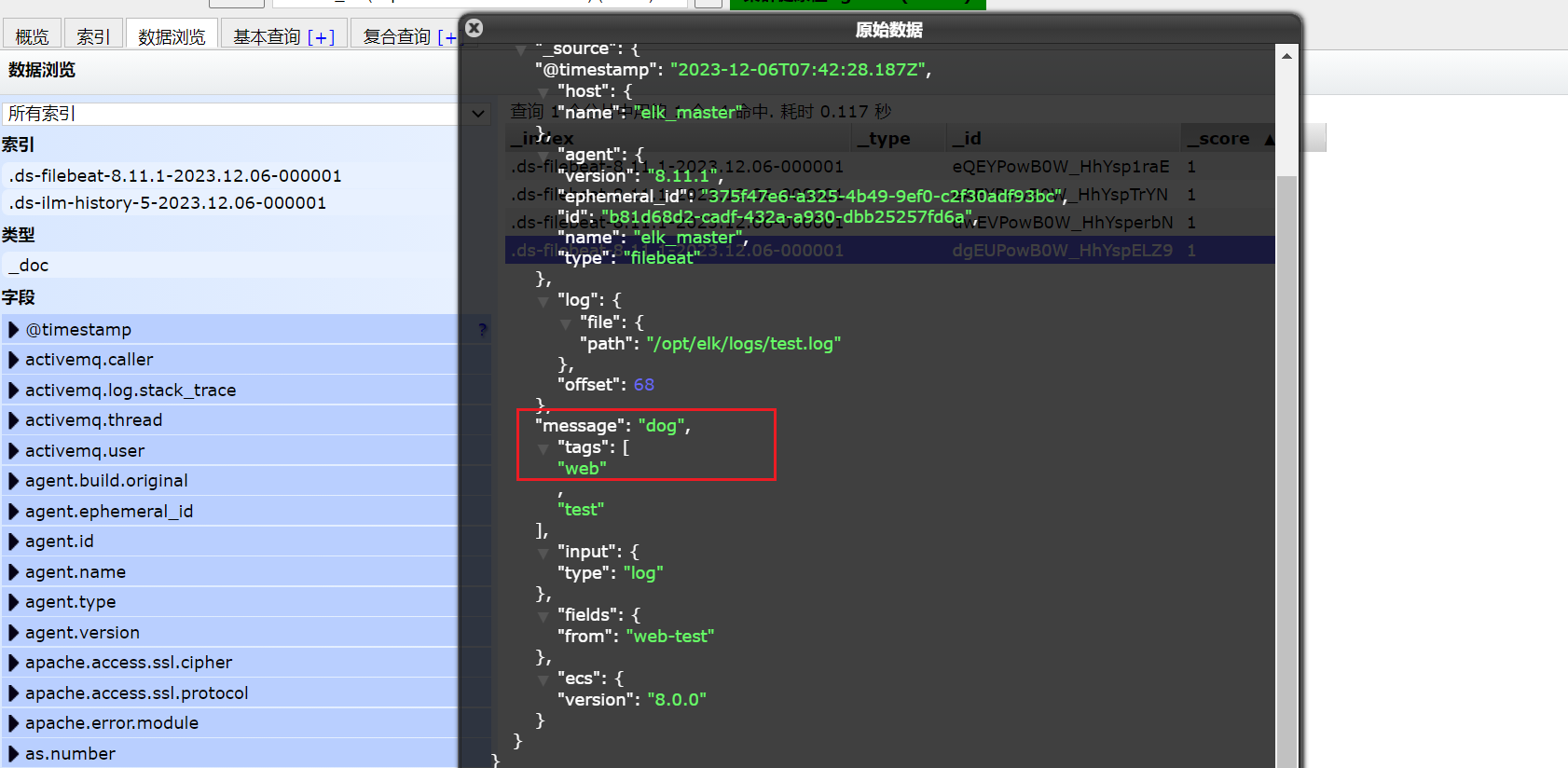

二、布线优化

在设计流程中,RTL设计距离布线阶段较远,但对布线仍然有着显著的影响。 这里我们介绍几种情况:

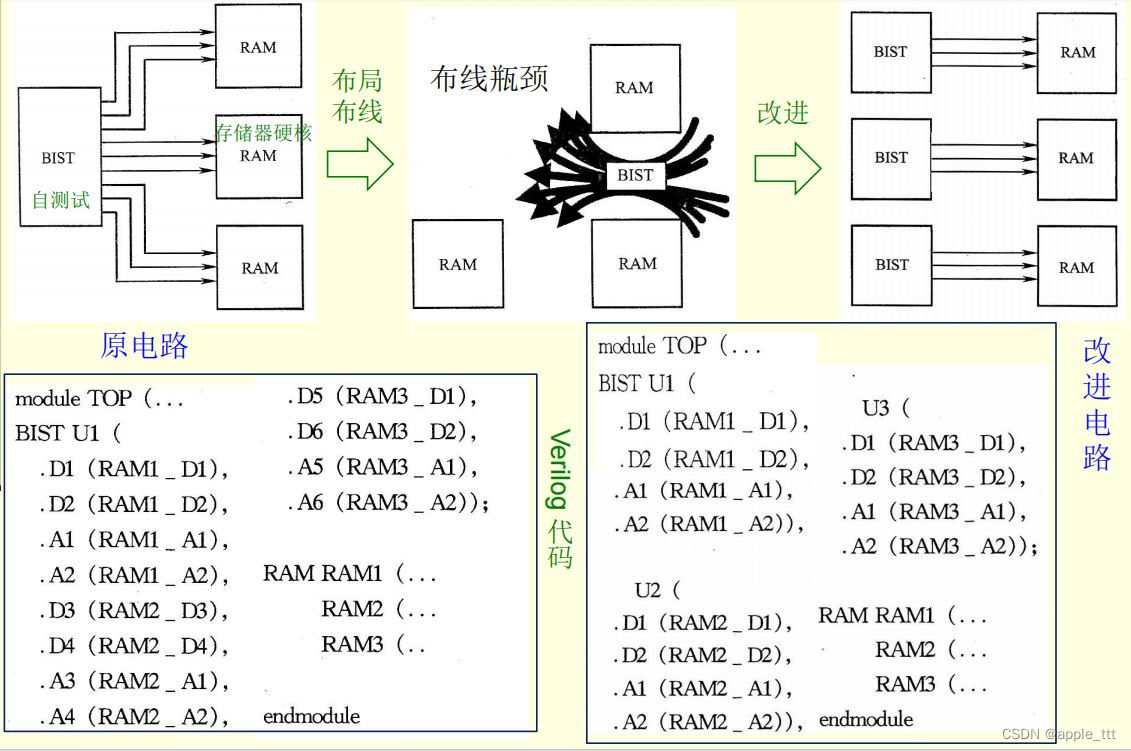

2.1 热点

对策如下:

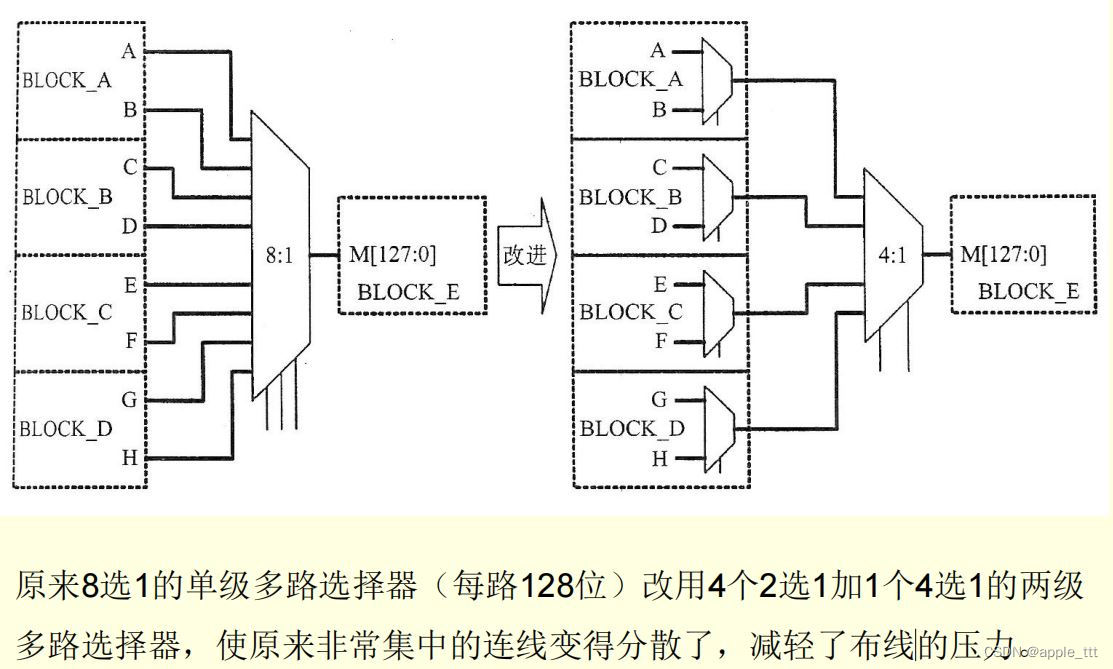

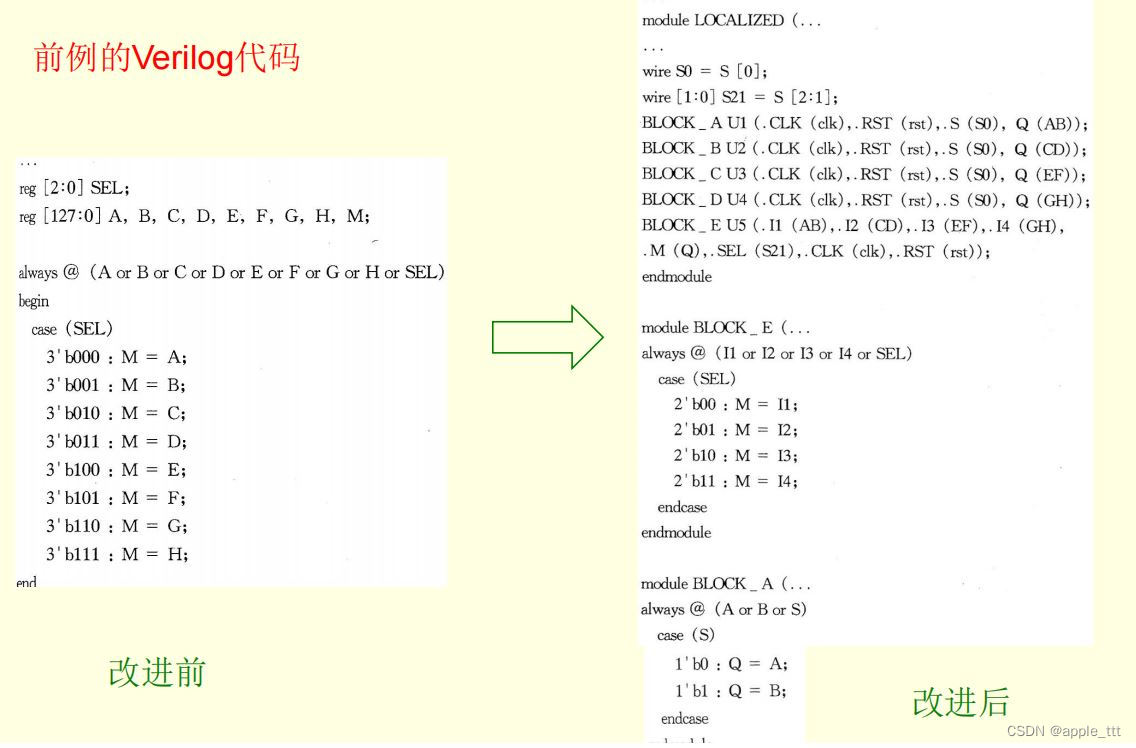

2.2 瓶颈

对策如下:

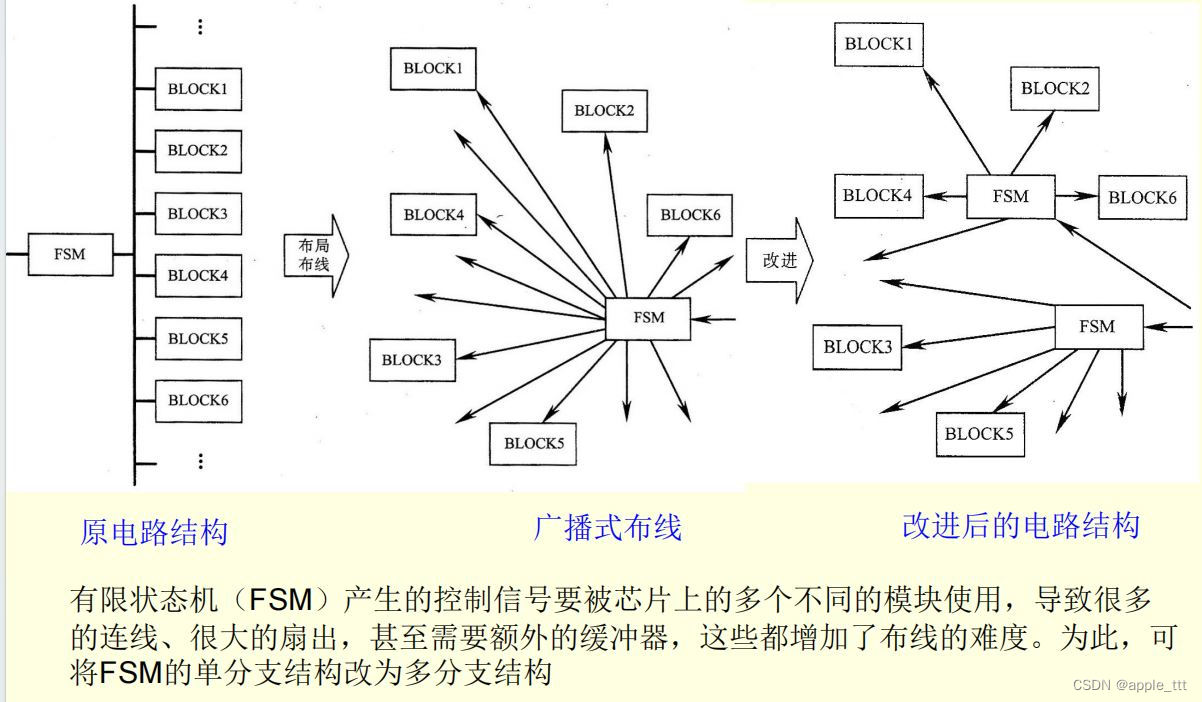

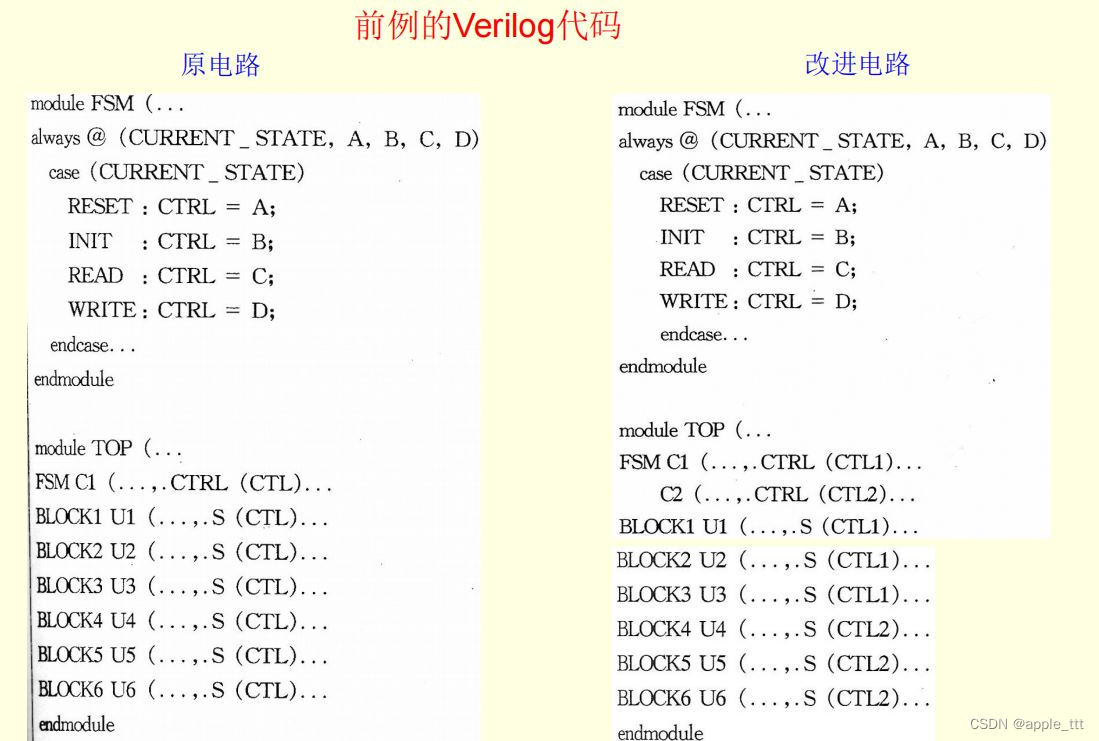

2.3 广播

对策如下:

三、总结

本文主要介绍了RTL编码过程中的语句优化和布线优化的内容,其中语句优化主要介绍了if和case语句使用的注意事项,阻塞与非阻塞语句的使用以及算法对于综合的影响。布线优化主要介绍了热点,瓶颈,广播三种情况及其解决方法。