专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

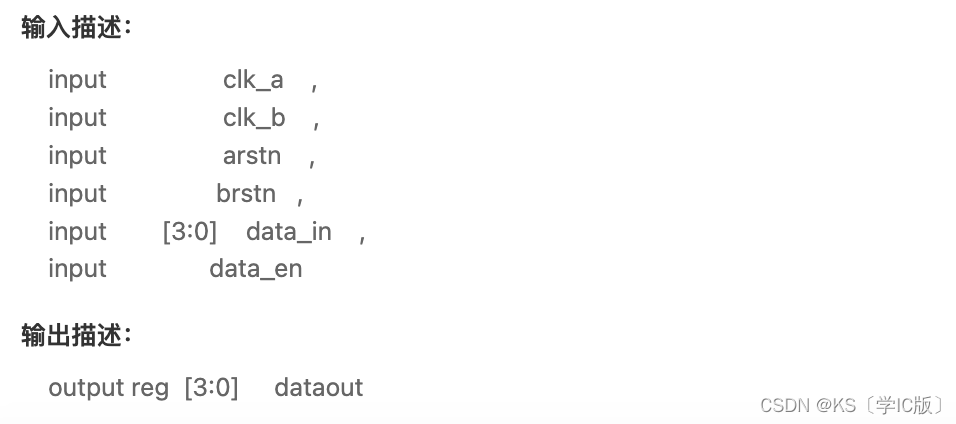

输入数据暂存在data_reg中,使能信号data_en用打两拍的方式跨时钟域传输到时钟域B,最后data_out根据使能信号更新数据。data_en信号在A时钟域用一个D触发器暂存,然后打两拍传输到B时钟域。根据同步到B时钟域的使能信号data_en_b1,更新输出。

`timescale 1ns/1nsmodule mux(input clk_a , input clk_b , input arstn ,input brstn ,input [3:0] data_in ,input data_en ,output reg [3:0] dataout

);reg [3:0] data_reg ; reg data_en_a, data_en_b0, data_en_b1 ; always @ (posedge clk_a or negedge arstn) begin if (~arstn) data_reg <= 0 ; else data_reg <= data_in ; endalways @ (posedge clk_a or negedge arstn) begin if (~arstn) data_en_a <= 0 ; else data_en_a <= data_en ; endalways @ (posedge clk_b or negedge brstn) begin if (~brstn) begin data_en_b0 <= 0 ; data_en_b1 <= 0 ; endelse begin data_en_b0 <= data_en_a ;data_en_b1 <= data_en_b0 ; endendalways @ (posedge clk_b or negedge brstn) begin if (~brstn) dataout <= 0 ; else dataout <= data_en_b1 ? data_reg : dataout ; endendmodule