基于Quartus件完成一个1位全加器的设计,分别采用:1)原理图输入 以及 2)Verilog编程 这两种设计方法。开发板基于Intel DE2-115。

在此基础上,用原理图以及Verilog 编程两种方式,完成4位全加器的设计,对比二者生成的 RTL差别;使用modelsim验证逻辑设计的正确性,并在DE2-115开发板上实际验证。

1位全加器可以用两个半加器及一个或门连接而成, 因此需要先完成半加器的设计。 下面将给出使用原理图输入的方法进行底层元件设计和层次化设计的主要步骤。

一,半加器设计

一,建立工程,

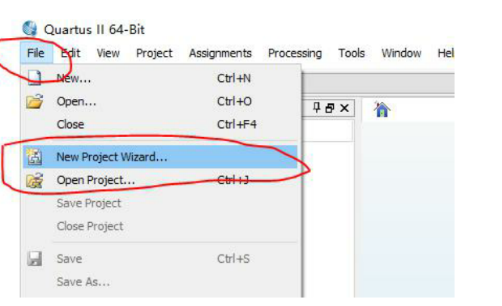

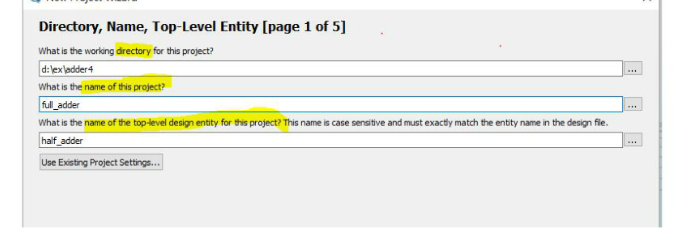

创建工程过程(

启动 Quartus II 软件,选择File->New Project Wizard,在出现的界面下先Next,填写工程的路径和名称,然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。

此时界面上会出现顶层文件名和项目名:

绘制过程实现

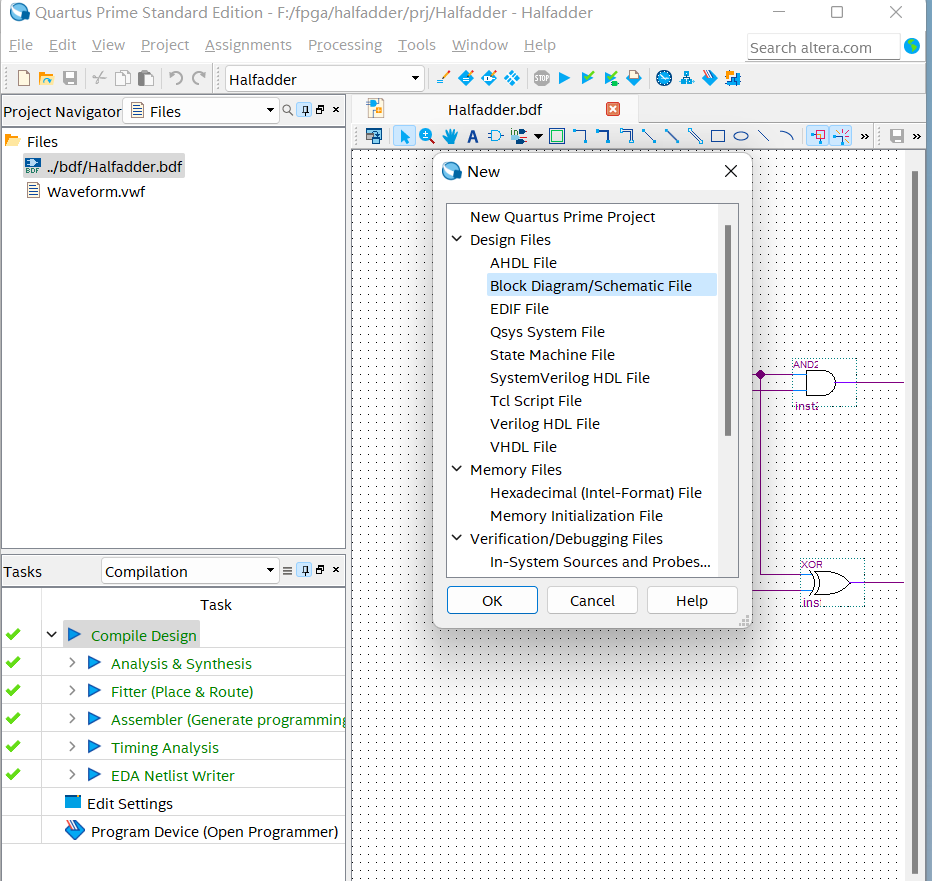

首先选择File->New,进入后选择Block Diagram/Schematic File

选择元件

添加输入输出,完成效果

保存文件,并且编译

选择菜单File——Save As,选择刚才建好的目录,F/fpag/halfadder/bdf,将已设计好的原理图文件取名为:halfadder.bdf(注 意默认的后缀是.bdf),并存盘在此文件夹内.

点击编译

发现没有问题

通过tool->Netlist Viewers->RTL Viewer,查看电路图

为了构成全加器的项层设计,必预将以上设计的半加器half_adder.bdf设置成可调用的元件。方法图所示,在打开半加器原理图文件half_adder1.bdf的情况下,选择菜中File中Create/Update→Create Symbol Files forCurrent File项,即可将当前文件h_adder. bdf变成一仿真实现

使用完全相同的方法也可以将VHDL文本文件变成原理图中的一个元件 符号,实现VHDL文本设计与原理图的混合输入设计方法。转换中需要注意以 下两点: 〔1)转换好的元件必须存在当前工程的路径文件夹中; (2)该方法只能针对被打开的当前文件。

5.仿真实现

创建一个向量波形文件,选择菜单项 File→New->VWF

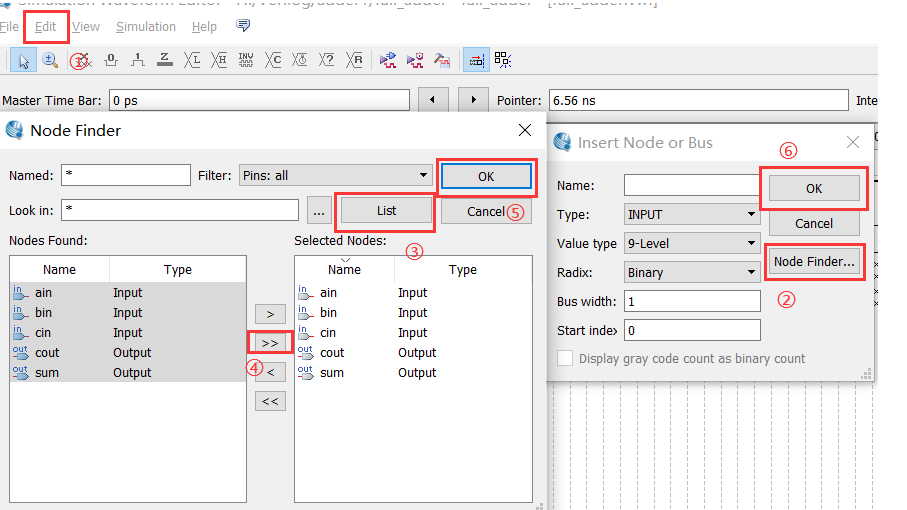

添加信号

最后点击ok

编辑信号

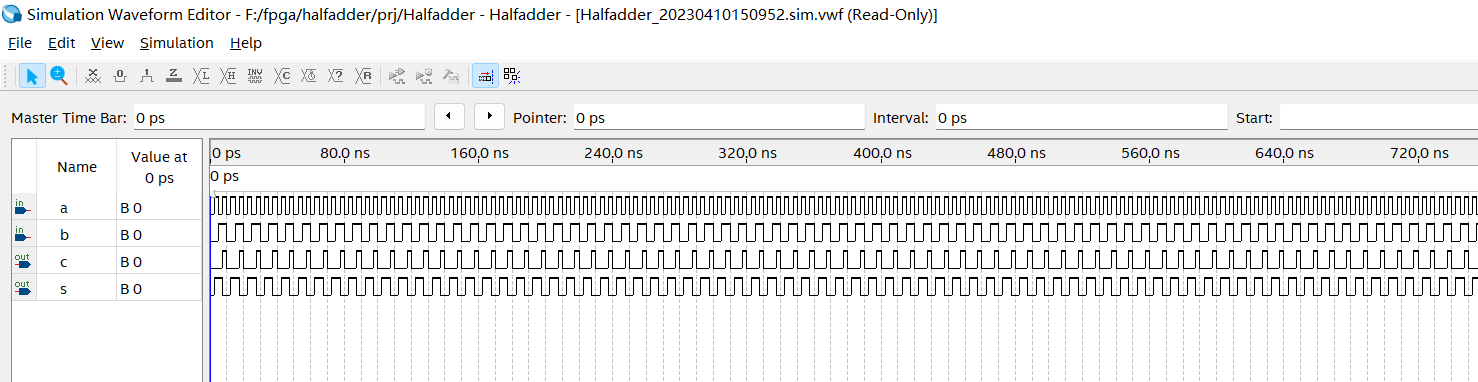

仿真。先保存文件为“Halfadder.vwf”,点击工具栏上功能仿 真按钮 ,完成后会自动跳出仿真后的文件。如图。从该图中可以分析半加器的逻 辑关系是否正确 。

功能仿真结果

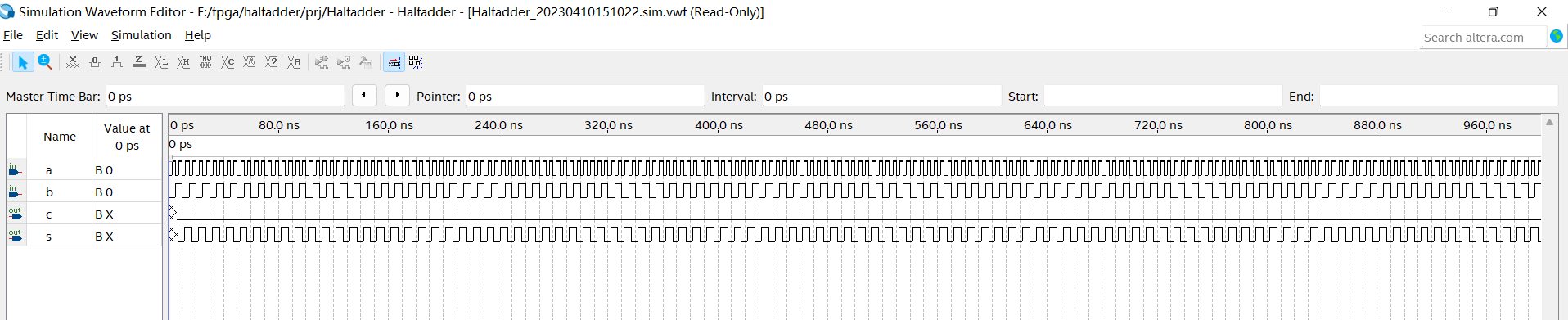

时序仿真结果

至此完成半加速设计。

二,全加器设计

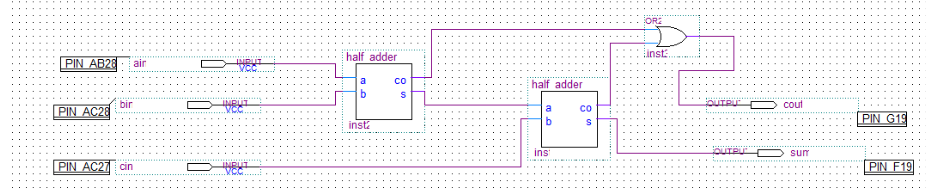

首用半加器元件实现全加器

先选择File->New,进入后选择Block Diagram/Schematic File

选择元件

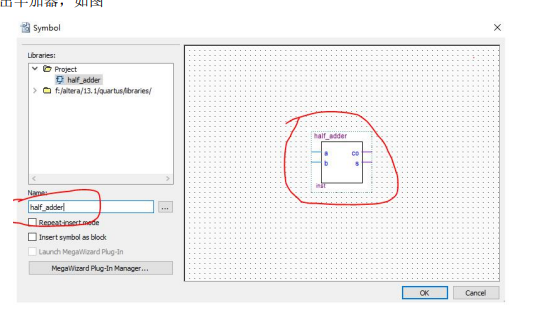

与调入元件的方法一样,即在新打开的原理图编辑窗双击鼠标,在弹出 的“symbol”窗的“name”栏输入底层文件半加器的存储名“halfadder” 调出半加器,如图

再调出其他需要的元件,连接好全加器的电路图。 以full_project1.bdf名将此全加器设计存在同一路径F/Fpga的文件夹中。

将设计项目设置成顶层文件并编译仿真,保存文件并且改名为fulladder。

将顶层文件fuddler.bdf设置为顶层文件的方法:project t→set astop_level entity。 如图:

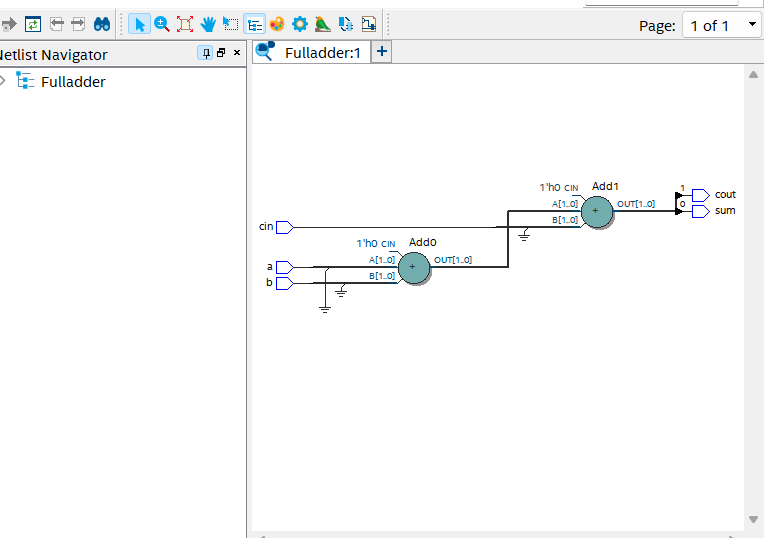

通过tool->Netlist Viewers->RTL Viewer,查看电路图

实现仿真

创建一个向量波形文件,选择菜单项 File→New->VWF

编辑信号

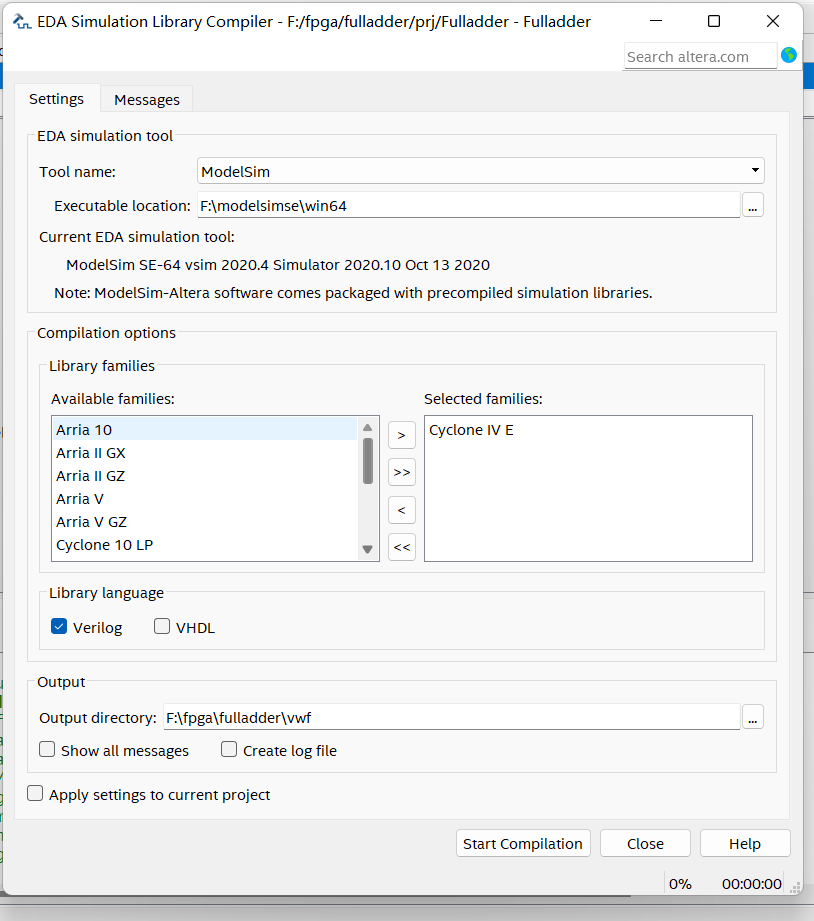

进行仿真配置,选择tool->launch simulation library complier

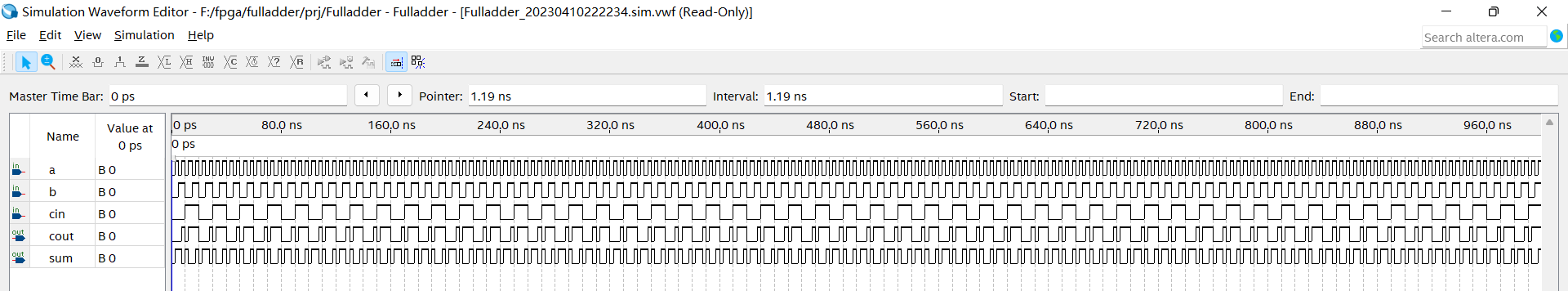

功能仿真结果

时许仿真结果

三,verilog实现一位半加速的实现

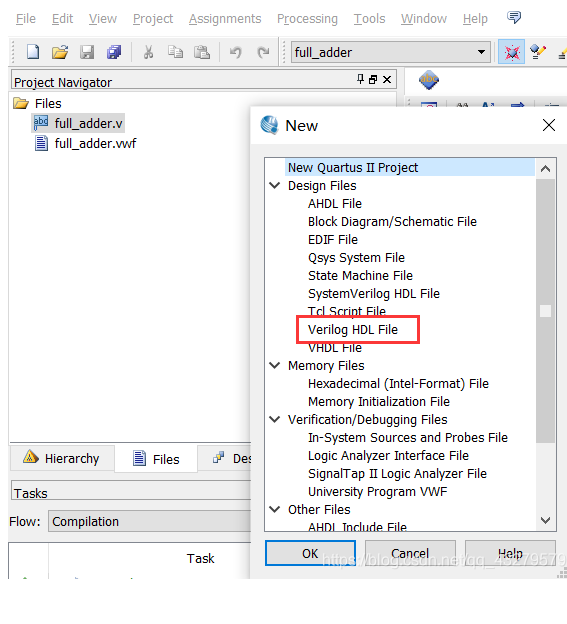

创建Verilog文件

代码实现

module Fulladder

(input a,b,output sum,output cout,input cin

);

assign{cout,sum} = a+b+cin;

endmodule保存并编译文件

通过tool->Netlist Viewers->RTL Viewer,查看电路图

3.写入仿真代码

`timescale 1ns/1ns

module TB_FUlladder(); // 设置仿真引脚reg tb_a ;reg tb_b ;reg tb_cin ;wire tb_sout ;wire tb_cout ;FUlladderu_FUlladder( // 绑定引脚,绑定仿真文件与源代码文件中对应的引脚.a (tb_a) ,.b (tb_b) ,.cin (tb_cin) ,.cout (tb_cout) ,.sum (tb_sout));parameter CYCLE = 40; // 设置周期always # 5 tb_a = ~tb_a ; // 设置输入变量always # 10 tb_b = ~tb_b ;always # 20 tb_cin = ~tb_cin ;initial begin // 初始化变量tb_a = 1'b0 ;tb_b = 1'b0 ;tb_cin = 1'b0 ;#(CYCLE * 4) ; // 设置到达指定周期停止$stop ;end

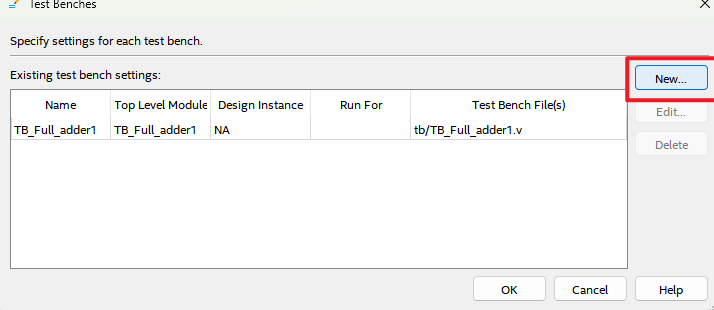

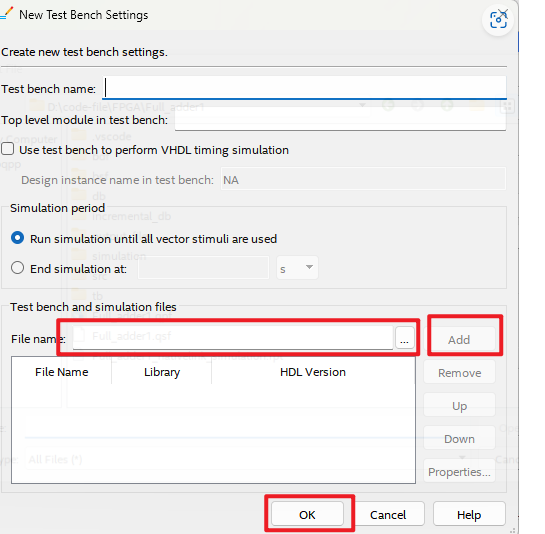

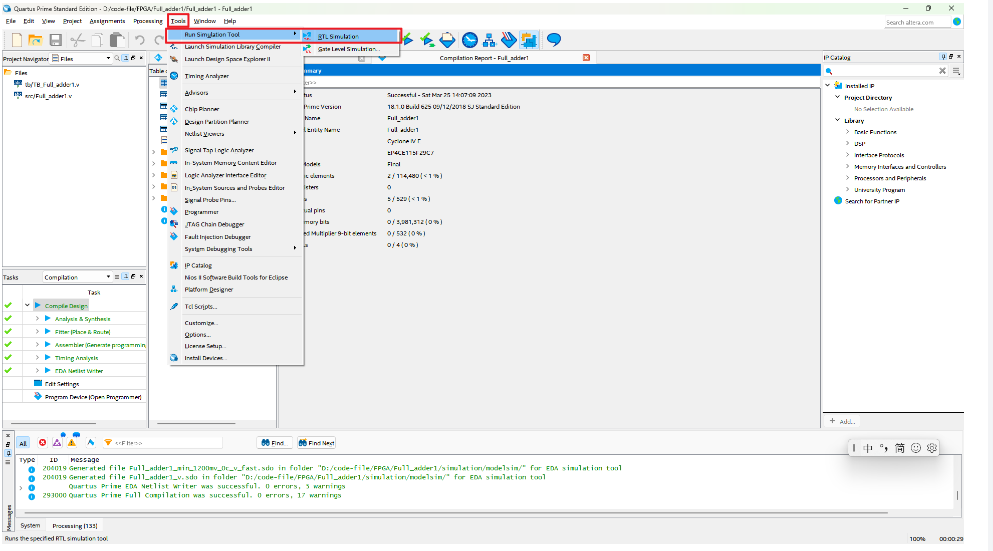

endmodule然后我们选择进行完整编译,编译成功后,我们在进行仿真之前,我们需要绑定仿真文件,下面给出完整步骤:

成功添加 testbench 仿真文件之后重新编译,然后就可以进行仿真了:

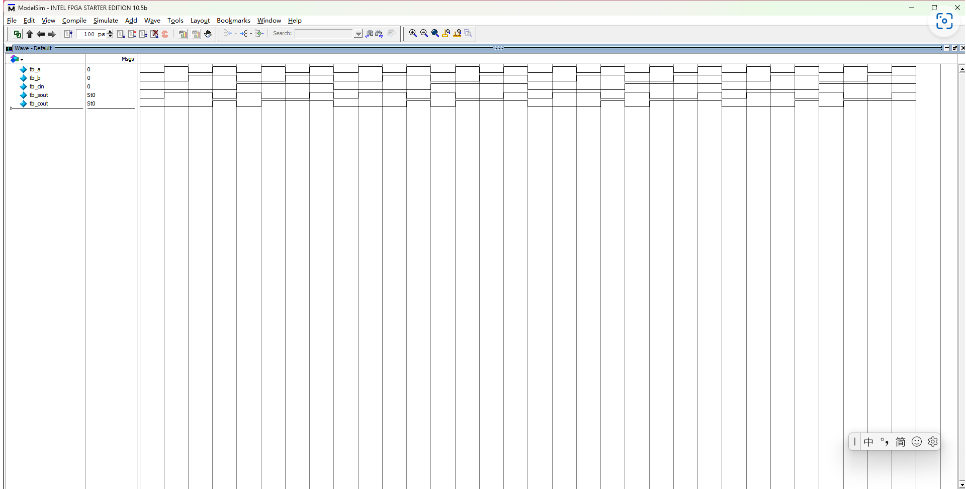

我们可以先点击运行,然后点击右面的缩放,最后我们只需要缩放到自己需要的大小即可,我们仿真后生成的波形如下:

三、Verilog实现1位加法器

1.创建Verilog文件

代码实现

module full_adder(//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位input ain,bin,cin,//输出信号,cout表示向高位的进位,sum表示本位的相加和output reg cout,sum);

reg s1,s2,s3;

always @(ain or bin or cin) beginsum=(ain^bin)^cin;//本位和输出表达式s1=ain&cin;s2=bin&cin;s3=ain&bin;cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule保存并编译文件

通过tool->Netlist Viewers->RTL Viewer,查看电路图

3.

仿真实现

创建一个向量波形文件,选择菜单项 File→New->VWF

添加信号

编辑信号

保存文件并启动功能仿真,出现错误,进行仿真配置,选择tool->launch simulation library complier功能仿真结果

时序仿真结果

通过仿真结果,可以发现得到的结果与真值表中是相吻合的。

四,下载测试

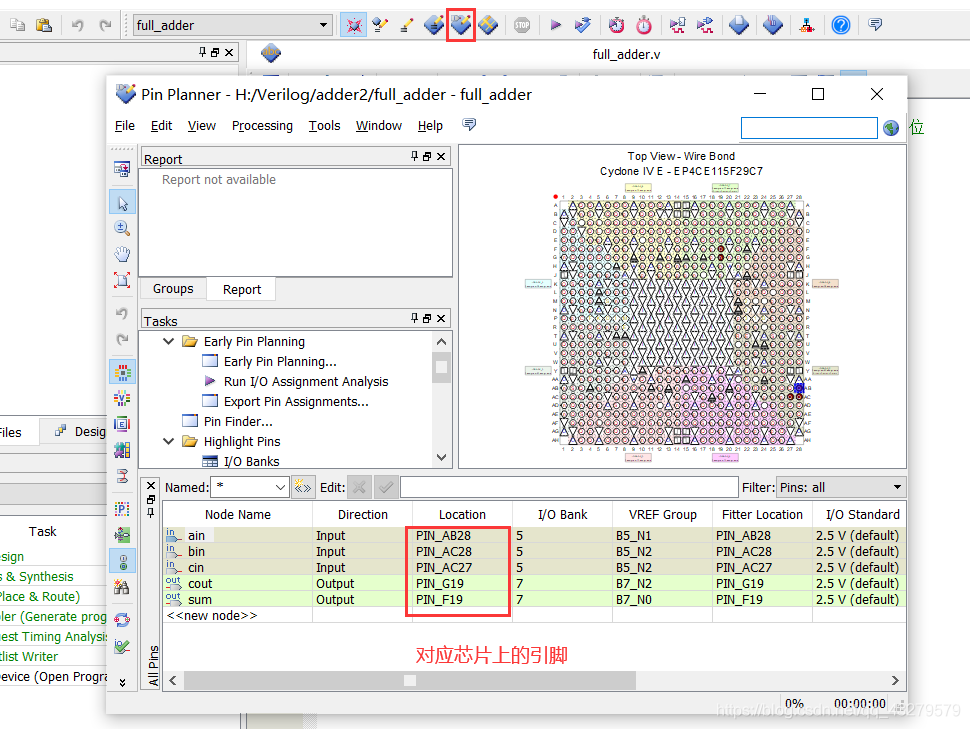

芯片引脚配置表

(一)输入原理图

1.

将设计项目设置为顶层文件

选中对应的设计文件

2.配置引脚

使用3个SW作为输入信号,2个LED作为输出信号

原理如下

下载

结果效果

通过拨动SW,观察LED的亮灭的效果,发现SW开表示1,关表示0,LED亮表示1,灭表示0。最终,验证的结果为跟其真值表相吻合。

(二)Verilog代码

配置引脚

使用3个SW作为输入信号,2个LED作为输出信号

下载

结果效果

通过拨动SW,观察LED的亮灭的效果,发现SW开表示1,关表示0,LED亮表示1,灭表示0。最终,验证的结果为跟其真值表相吻合。

1位全加器的实现完成后,可以根据多个1位全加器的级联实现多位全加器。