什么是组合逻辑电路

组合逻辑电路是由一些基本的逻辑门电路组成的,没有反馈,输出仅取决于输入。

组合逻辑电路是数字逻辑电路中一种重要的电路类型,它是由多个逻辑门(例如与门、或门、非门等)组成的电路。组合逻辑电路根据输入信号的状态,在不需要时钟脉冲的情况下直接产生输出。

因此,组合逻辑电路可以看成纯粹的布尔运算器。

组合逻辑电路有以下特点:

(1)只由逻辑门和电线构成,没有存储器件;

(2)输出仅与输入有关,不存在任何时序关系;

(3)逻辑门的输出可以直接连接到其他门的输入端;

(4)不会产生任何形式的反馈,每个输出信号只由与之直接相连的输入决定。

常用组合逻辑电路包括:

(1)算术运算电路(加法器减法器等等)

(2)编码器(Encoder)

(3)译码器(Decoder)

(4)数据选择器(MUX)

(5)数据分配器

(6)数值比较器

(7)其它

组合逻辑电路设计一般步骤:

(1)由实际逻辑问题列出真值表;

(2)由真值表写出逻辑表达式;

(3)化简、变换输出逻辑表达式;

(4)画出逻辑图。

设计组合逻辑的目的:

(1)从电路中获得所需的输出;

(2)经济电路意味着以最少的费用构建电路;

(3)必须尽可能地降低电路的复杂性;

(4)使用最少数量的门,数字电路应设计为最小化整体电路延迟。

加法器

参考大神的文章:

专题2-8:加法器 - 知乎

简要摘录内容如下:

半加器和全加器是算术运算电路中的基本单元,它们是完成1位二进制数相加的一种组合逻辑电路。

半加器

如果只考虑了两个加数本身,而没有考虑低位进位的加法运算,称为半加。

实现半加运算的逻辑电路称为半加器。

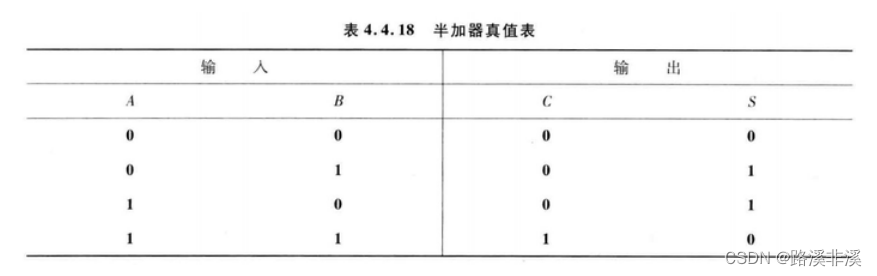

两个1位二进制的半加运算可用下面所示的真值表表示。

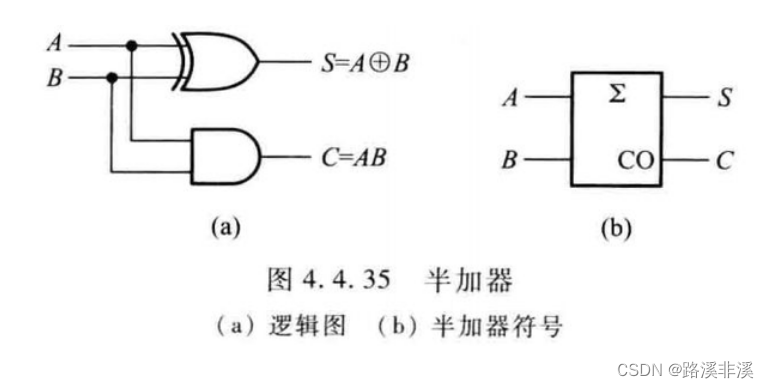

注意,半加器虽然没有进位输入,可是有进位输出。也就是说,它的进位可以传递给后级电路。下面是一个由异或门和与门组成的半加器,右边是半加器的电路符号。

对于算术运算来说,如果不考虑进位,显然是没法得到正确的结果的。

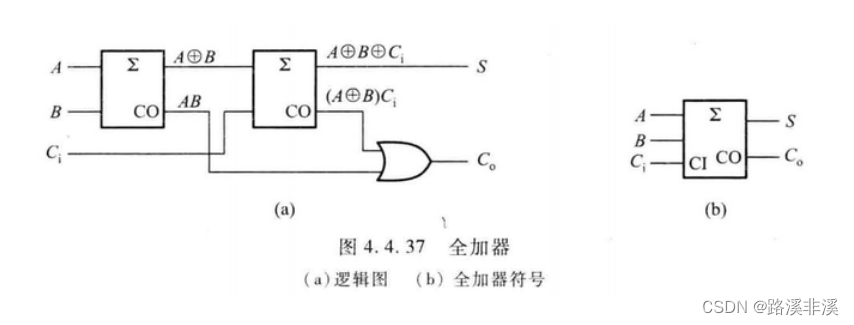

所以,将两个半加器结合,再加上一些其他的电路,就能组成一个全加器。

全加器

全加器能进行【被加数】、【加数】和【来自低位的进位】信号相加,并根据求和结果给出该位的【进位】信号。

根据全加器的功能,可列出它的真值表:

其中A和 B分别是被加数及加数,Ci为低位进位数,S为本位和数(称为全加和)以及C0为向高位的进位数。

下图是由两个半加器和一个或门构成的全加器

既能带进位相加,又能向上一级输出进位,这就和我们日常计算方式是类似的。

全加器是能得出正确求和结果的最小单位,能实现两个1位二进制数的求和。

但是仅实现两个1位二进制数的和还不够,现实中往往需要实现十几位甚至几十位的二进制运算。

串行进位加法器

若有多位数相加,则可采用【并行相加,串行进位】的方式来完成。

将低位的进位输出信号接到高位的进位输入端,因此,任1位的加法运算必须在低1位的运算完成之后才能进行,这种进位方式称为串行进位。

这种加法器的逻辑电路比较简单,但它的运算速度不高。为克服这一缺点,可以采用超前进位等方式。

超前进位加法器

由于串行进位加法器的速度受到进位信号的限制,人们又设计了一种多位数超前进位加法逻辑电路,使每位的进位只由被加数和加数决定,而与低位的进位无关。

超前进位加法器大大提高了运算速度。但是,随着加法器位数的增加,超前进位逻辑电路越来越复杂。超前进位级联方式提高了电路的工作速度,但也增加了电路结构的复杂程度。

具体参考大神的文章以及相关资料。

减法器

参考大神的文章:专题2-9:减法器 - 知乎

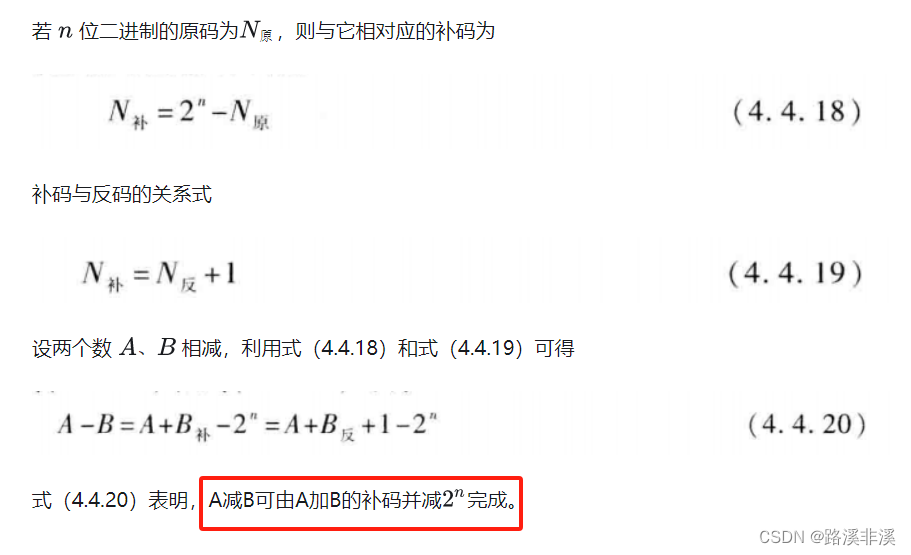

减法运算的原理是将减法运算转换成补码的加法运算进行的。

如果加法器既能实现加法运算,又可实现减法运算,就可以简化数字系统结构。

具体实现过程参考大神文章和相关资料。

当然还有其他各种可以算术运算的电路,可查阅相关资料学习。

编码器

参考大神文章:专题2-2:编码器 - 知乎

用代码表示特定信号的过程叫编码;实现编码功能的逻辑电路叫编码器。编码器的输入是被编码的信号,输出是与输入信号对应的一组二进制代码。

啥意思?

以前不懂编码器,现在倒是能稍微想明白一些。

想一想,键盘上那么多字符,怎么用电路来识别呢?

一种简单粗暴的方法就是给每个符号一个IO口,看哪个IO口被触发了就能知道是哪个符号按下了,假如有100种符号,就用100个IO口即可实现功能。

怎么样,简单粗暴吧

虽然能实现,但这不就是在纯纯地浪费资源嘛。

在计算机中,二进制的一个大亮点就是0和1可以有各种组合,100个字符,只需要7位二进制数就能表示完,如果是200个符号,也只需要8位二进制来表示,这样,我们就可以将这200个符号分别对应一个8位的二进制数的一种排列组合,此时,我们用8个IO口就能表示这200个符号了。

资源占用从200个IO口瞬间降到了8个IO口。

这就是编码器的思想和意义所在。

我们常见的8-3编码器,就是可以将8种状态编码成3位二进制数,从而便于MCU识别和处理。数字系统中存储或处理的信息,常常是用二进制码表示的。

用一个二进制代码表示特定含义的信息称为编码。具有编码功能的逻辑电路称为编码器。

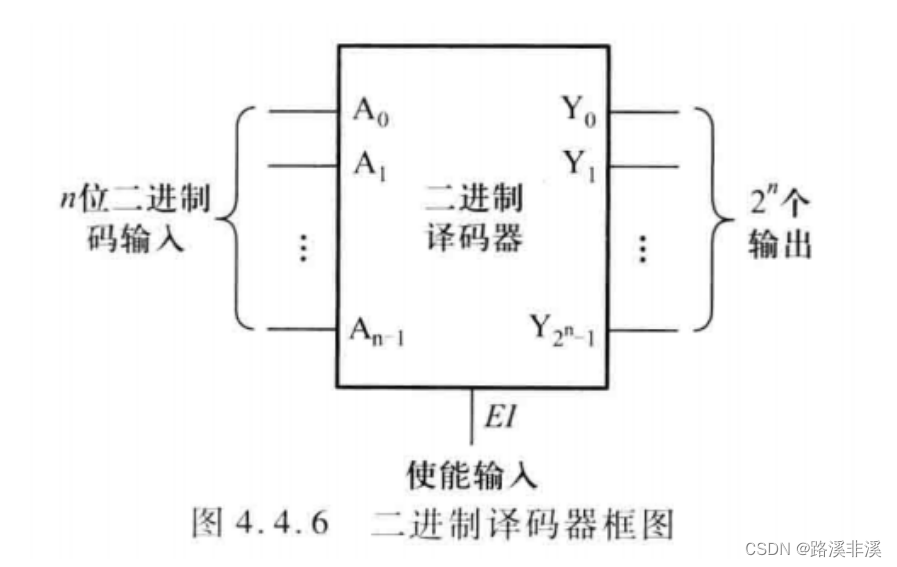

下图所示为二进制编码器的结构图,它有n位二进制码输出,与 2^n个输入相对应。

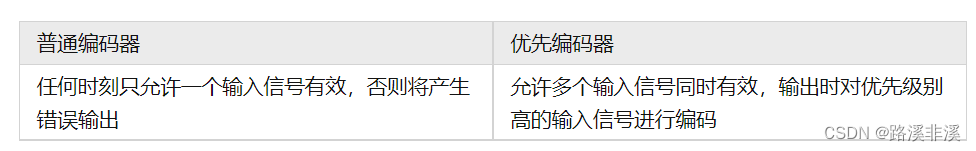

编码器有普通编码器和优先编码器之分。

优先编码器虽然允许多个输入信号同时有效,但是只会对优先级别最高的输入信号进行编码,其他优先级别低的就算输入有效,也会被忽略。

在实际应用中,经常会遇到两个以上的输入同时为有效信号的情况。因此,必须根据轻重缓急,事先规定好这些输入编码的先后次序,即优先级别。【识别】这类请求信号的优先级别并进行【编码】的逻辑电路称为优先编码器。

更多细节内容查看大神文章或者查阅相关资料。

译码器

参考大神文章:专题2-3:译码器 - 知乎

理解了编码器,译码器也相对容易理解。

译码器就是编码器的反向操作。

可以将某几位二进制数据“翻译”成对应的状态,比如计算机要将符号显示在显示屏上,就需要先对二进制数据进行识别,其对应的是哪个符号,然后在屏幕上显示相应的内容。我们常见的3-8译码器就是将3位二进制数转换成对应的8种状态中的某一种。

键盘到计算机是编码,计算机到显示器是译码。

译码器常用于计算机中对存储器单元地址的译码,即将每一个地址代码转换成一个有效信号,从而选中对应的单元。我们单片机的地址就需要通过译码器才能识别到是要访问那个单元。

其框图如下:

在使能输入端为有效电平时,对应每组输入代码,只有其中一个输出端为有效电平,其余输出端则为相反电平。输出信号可以是高电平有效,也可以是低电平有效。

译码器输出时只有一个输出端是有效电平,通过输出端有效电平的唯一性以识别不同的代码。

比如单片机驱动数码管通常就需要用到3-8显示译码器来控制位选和段选。

更多内容参考大神文章和相关资料。

数据选择器

参考大神文章:专题2-6:数据选择器 - 知乎

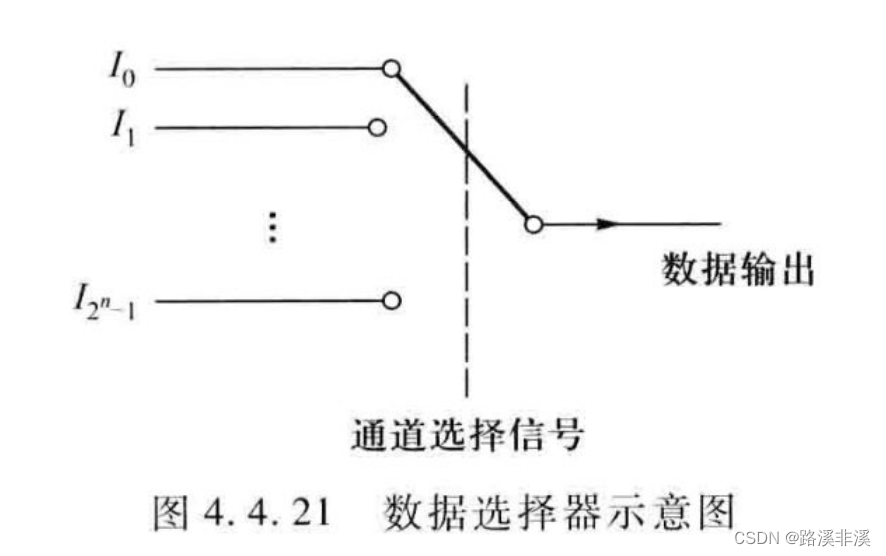

数据选择器(data selector) 根据给定的输入地址代码,从一组输入信号中选出指定的一个送至输出端的组合逻辑电路。有时也把它叫做多路选择器或多路调制器(multiplexer)。

数据选择器在单片机中很常见,比如时钟选择哪个分频系数,比如ADC选取哪个通道来采集等等,都是从多个选项中选择其中一个输出,其实就是一个信号传输的单刀多掷开关,跟哪个选项连接就选中了哪个通道输入。

数据选择是指经过选择,把多路数据中的某一路数据传送到公共数据线上,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下所示。

常用的数据选择器有2选1数据选择器、4 选1数据选择器、8 选1数据选择器、16 选1数据选择器等。还有一些数据选择器具有三态输出功能,除了正常的0或1输出之外,当使能输入端为无效信号时,输出为高阻状态。

更多内容参考大神文章或者相关资料。

数据分配器

参考大神文章:专题2-5:数据分配器 - 知乎

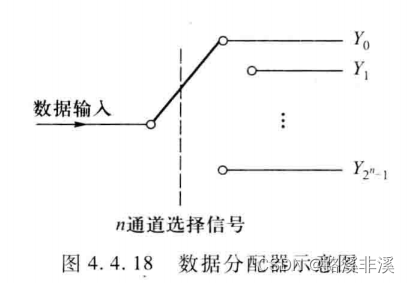

能够将1个输入数据,根据需要传送到m个输出端的任何一个输出端的电路,叫做数据分配器,又称为多路分配器,其逻辑功能正好与数据选择器相反。

它的作用相当于多个输出的单刀多掷开关

更多内容参考大神文章或者相关资料。

数值比较器

参考大神文章:专题2-7:数值比较器 - 知乎

在数字电路中,经常需要对两个位数相同的二进制数进行比较,以判断它们的相对大小或者是否相等,用来实现这一功能的逻辑电路就成为数值比较器。

在数字系统中,特别是在计算机中常需要对两个数的大小进行比较。

数值比较器就是对两个二进制数A、B进行比较的逻辑电路,比较结果有 A>B 、 A<B 以及 A=B 三种情况。

数值比较器基础的有1位、2位、4位数值比较器,更多的可以级联实现。

1位数值比较器是多位比较器的基础。

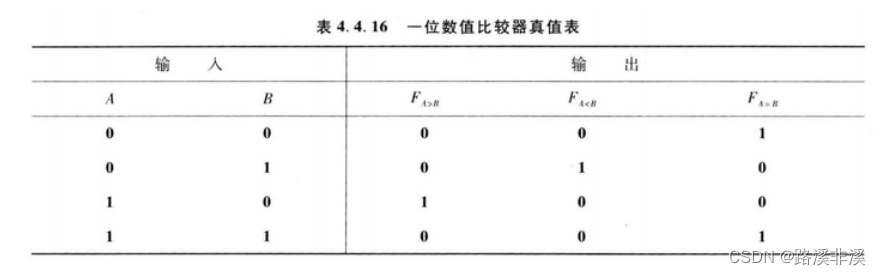

当 A和 B 都是1位二进制数时,它们只能取0或1两种值,由此可写出1位数值比较器的真值表,如下表所示。

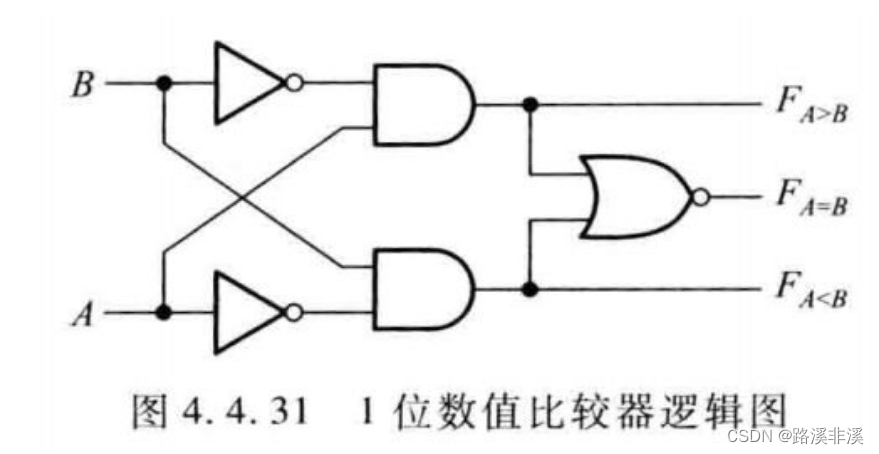

逻辑图

更多内容参考大神文章或者相关资料。

可编程逻辑器件

可编程逻辑器件(Programmable Logic Device,PLD)

PLD是通过程序控制门电路实现各种逻辑功能,等于是直接驱动硬件来实现各种运算,而不是通过软件然后让硬件的通用单元来执行。

还有个叫PLC,是可编程逻辑控制器,PLD可以看做是PLC的基本组件,PLC集成化更高。

理论上,各种逻辑需求都能通过逻辑器件搭出来。

当下高密度的是主流,又有CPLD和FPGA两种。

CPLD,全英文名称为Complex Programming logic device,中文为复杂可编程逻辑器件。

FPGA,全称为Field-ProgrammableGateArray,即现场可编程门阵列。

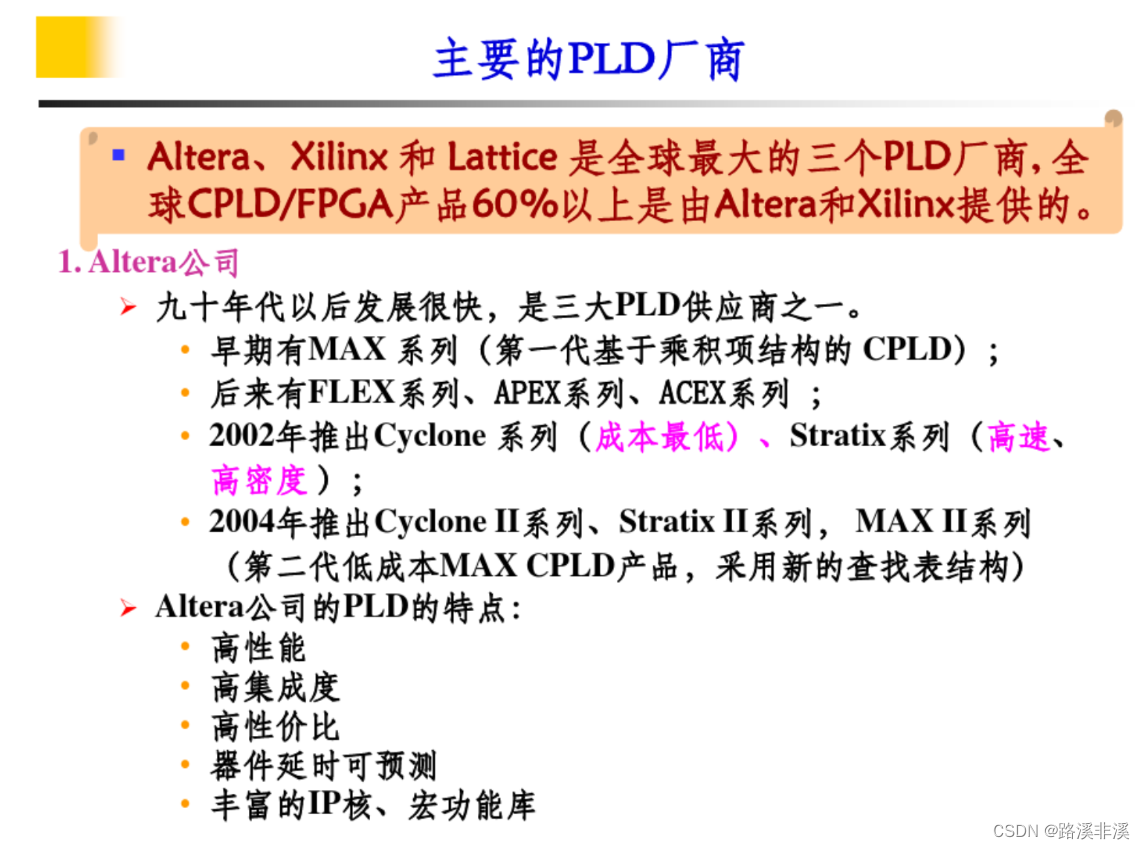

全球顶级的两家PLD厂商:

Altera公司 ➢ 九十年代以后发展很快,是三大PLD供应商之一;

Xilinx(赛灵思)公司 ➢ FPGA的发明者( Xilinx 公司于1985年首次推出FPGA ),老牌PLD公司,三大PLD供应商之一;

其他几家

具体参考:主要的PLD厂商

PLD结构框图

和计算机的处理思路都是相通的,无非就是数据输入,然后处理,然后输出和存储。

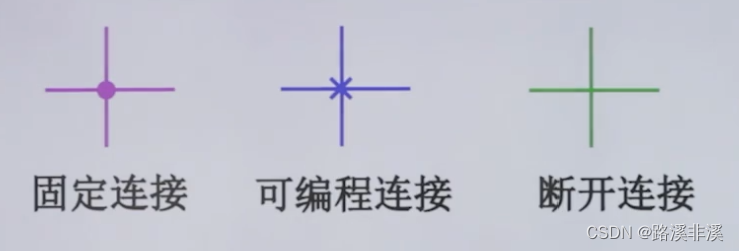

内部连接示意:

中间的可编程连接就是控制的精髓所在。

PLA

此小节了解即可。

理论上所有的逻辑都可以由与门、或门的组合电路实现。

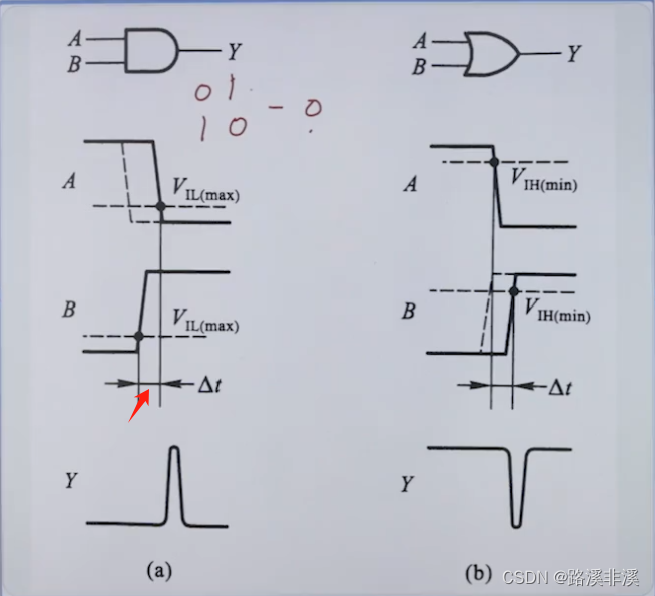

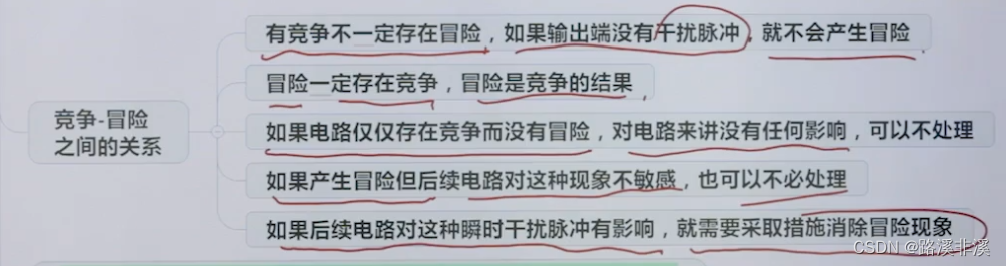

竞争冒险现象

其实就是两路信号向相反方向转换时,由于传输时延可能有差别,导致中间某个时刻可能出现不想要的电平状态。

二者之间的关系

产生原因

![[pytorch入门] 6. 神经网络](https://img-blog.csdnimg.cn/direct/5169ed7542c047f5b2968863f602063a.png)