接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(11)

4.2 PCIe体系结构的组成部件

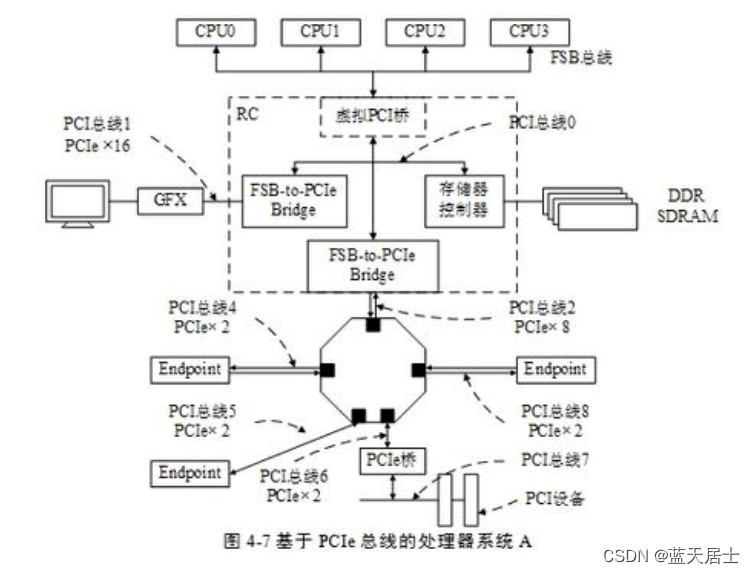

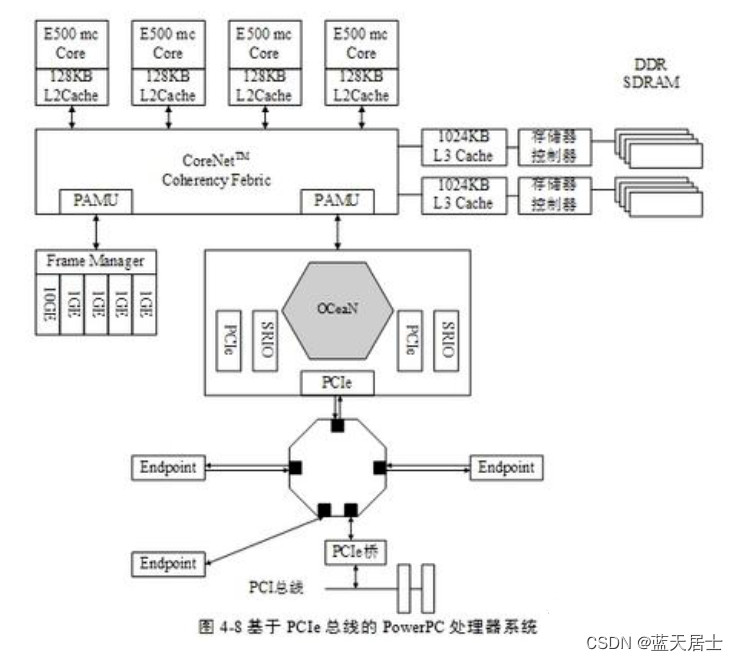

PCIe总线作为处理器系统的局部总线,其作用与PCI总线类似,主要目的是为了连接处理器系统中的外部设备,当然PCIe总线也可以连接其它处理器系统。在不同的处理器系统中,PCIe体系结构的实现方法略有不同。但是在大多数处理器系统中,都使用了RC、Switch和PCIe-to-PCI桥这些基本模块连接PCIe和PCI设备。在PCIe总线中,基于PCIe总线的设备,也被称为EP(Endpoint)。

4.2.2 RC的组成结构

RC是PCIe体系结构的一个重要组成部件,也是一个较为混乱的概念。RC的提出与x86处理器系统密切相关。事实上,只有x86处理器才存在PCIe总线规范定义的“标准RC”,而在多数处理器系统,并不含有在PCIe总线规范中涉及的与RC相关的全部概念。

不同处理器系统的RC设计并不相同,在图4-7中的处理器系统中,RC包括存储器控制器、两个FSB-to-PCIe桥。

而在图4-8中的PowerPC处理器系统中,RC的概念并不明晰。在PowerPC处理器中并不存在真正意义上的RC,而仅包含PCIe总线控制器。

在x86处理器系统中,RC内部集成了一些PCI设备、RCRB(RC Register Block)和Event Collector等组成部件。其中:RCRB由一系列“管理存储器系统”的寄存器组成,而仅存在于x86处理器中;而Event Collector用来处理来自PCIe设备的错误消息报文和PME消息报文。RCRB寄存器组属于PCI总线域地址空间,x86处理器访问RCRB的方法与访问PCI设备的配置寄存器相同。在有些x86处理器系统中,RCRB在PCI总线0的设备0中。

RCRB是x86处理器所独有的,PowerPC处理器也含有一组“管理存储器系统”的寄存器,这组寄存器与RCRB所实现的功能类似。但是在PowerPC处理器中,该组寄存器以CCSRBAR寄存器为基地址,处理器采用存储器映像方式访问这组寄存器。

如果将RC中的RCRB、内置的PCI设备和Event Collector去除,该RC的主要功能与PCI总线中的HOST主桥类似,其主要作用是完成存储器域到PCI总线域的地址转换。但是随着虚拟化技术的引入,尤其是引入MR-IOV技术之后,RC的实现变得异常复杂。

但是RC与HOST主桥并不相同,RC除了完成地址空间的转换之外,还需要完成物理信号的转换。在PowerPC处理器的RC中,来自OCeaN或者FSB的信号协议与PCIe总线信号使用的电气特性并不兼容,使用的总线事务也并不相同,因此必须进行信号协议和总线事务的转换。

在P4080处理器中,RC的下游端口可以挂接Switch扩展更多的PCIe端口,也可以只挂接一个EP。在P4080处理器的RC中,设置了一组Inbound和Outbound寄存器组,用于存储器域与PCI总线域之间地址空间的转换;而P4080处理器的RC还可以使用Outbound寄存器组将PCI设备的配置空间直接映射到存储器域中。PowerPC处理器在处理PCI/PCIe接口时,都使用这组Inbound和Outbound寄存器组。

在P4080处理器中,RC可以使用PEX_CONFIG_ADDR与PEX_CONFIG_DATA寄存器对EP进行配置读写,这两个寄存器与MPC8548处理器HOST主桥的PCI_CONFIG_ADDR和PCI_CONFIG_DATA寄存器类似,本章不再详细介绍这组寄存器。

而x86处理器的RC设计与PowerPC处理器有较大的不同,实际上和大多数处理器系统都不相同。x86处理器赋予了RC新的含义,PCIe总线规范中涉及的RC也以x86处理器为例进行说明,而且一些在PCIe总线规范中出现的最新功能也在Intel的x86处理器系统中率先实现。在x86处理器系统中的RC实现也比其它处理器系统复杂得多。深入理解x86处理器系统的RC对于理解PCIe体系结构非常重要。

更多内容请看下回。