VHDL函数和过程

对于在设计中多次使用的块,请使用VHDL函数和过程。这个内容类似于组合过程内容在中声明函数和过程:

•实体的声明性部分

•架构

•一个包

函数或过程由声明部分和主体组成。声明性部分规定:

•输入参数,可以不受给定界限的约束。

•输出和输入参数(仅限程序)

重要!除IEEE中定义的功能外,不支持分辨率功能std_logic_1164包。

包内声明的函数示例(VHDL)

文件名:function_package_1.vhd

从编码示例下载编码示例文件。

此编码示例声明了包中的ADD函数。ADD功能是单个位加法器,并被调用四次以创建一个4位加法器。以下示例使用了一个函数:

VHDL断言语句

-Assert合成选项支持断言语句。

小心!使用断言时应小心。Vivado只能支持不创建的静态断言或者是由行为创建的。例如,对常量或运算符的值执行断言/一般作品;然而,作为一种资产,if语句中信号的值是不起作用的。

VHDL预定义包

Vivado synthesis支持STD和IEEE中定义的VHDL预定义包标准库。这些库是预编译的,不需要用户编译,并且可以直接包含在HDL源代码中。

VHDL预定义标准包

默认情况下包括VHDL预定义的标准包,定义以下基本

VHDL类型:bit、bit_vector、integer、natural、real和boolean。

VHDL IEEE包

Vivado synthesis支持一些预定义的VHDL IEEE包,这些包在IEEE库和以下IEEE包:

•数字比特

○ 基于位的无符号和有符号矢量类型。

○ 重载的算术运算符、转换函数和这些的扩展函数类型。

•std_logic_1164

○ std_logic、std_ulogic、std_logic_vector和std_ulogic_vector类型。

○ 基于这些类型的转换函数。

•数字_std

○ 基于std_logic的无符号和有符号矢量类型。

○ 重载的算术运算符、转换函数和这些的扩展函数类型。相当于std_logic_arith。

•已修复_pkg

○ 用于固定变量和接点类型。

○ 使用ieee.fixed_pkg.all;

•浮动_pkg

○ 用于浮动变量和引脚类型。

○ 使用ieee.float_pkg.all;

VHDL旧版包

•std_logic_arith(Synopsys)

○ 基于std_logic的无符号和有符号矢量类型。

○ 重载的算术运算符、转换函数和这些的扩展函数类型。

•std_logic_sunsigned(Synopsys)

○ std_logic和std_logic_vvector的无符号算术运算符

•std_logic_signed(Synopsys)

○ std_logic和std_logic_vvector的有符号算术运算符

•std_logic_misc(Synopsys)

○ std_logic_1164包的补充类型、子类型、常量和函数,如and_reduce和or_reduce。

VHDL预定义的IEEE实型和IEEE数学

包装

VHDL预定义的IEEE真实类型和IEEE math_real包仅支持计算,例如泛型值的计算,并且不能用于描述可合成的功能。

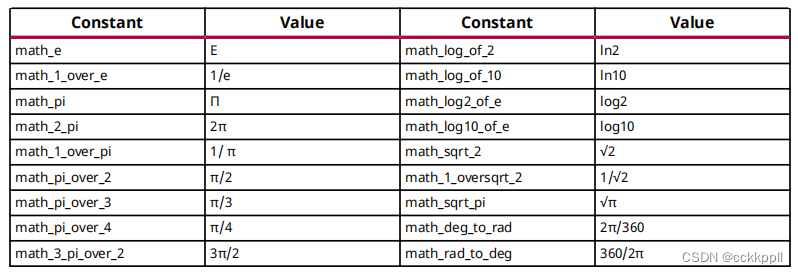

VHDL实数常量

下表描述了VHDL实数常量。

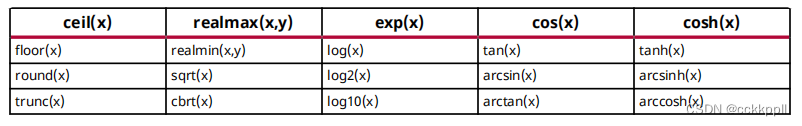

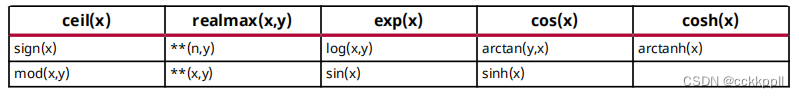

VHDL实数函数

下表描述了VHDL实数函数: