🔥博客主页:[PannLZ]

😘欢迎关注:👍点赞🙌收藏✍️留言

文章目录

- PCIe简介

- PCIe速度

PCIe简介

计算机内部有很多电子元器件,他们之间会有数据沟通和传输的需求。如果A元件想给B元件传输数据,那他就需要建立通路。在电脑里这种不同交互数据的通路就被我们称为总线。无论什么线路,都是基于目前的物理准则之上的,总线也是有一定承载能力的,不可能做到所有的数据秒传。总线单位时间内传输的数据量我们称之为带宽。

说了总线再简单说说协议,简单来说协议就是电脑内部的一种规矩,规定了两个设备通讯时如何识别对方,如何建立连接,使用的讯号类型,数据编码解码方式,数据传输的类型,数据传输的方式,物理层电压电流,保持和截止时间等等规定。两个设备只有协议一样或者相容才能够进行通讯。协议也可以说就是通讯双方提前约定好采用某种形式,以某种规格利用某种物体把数据传输出去,另一方在以同样的规则和流程去接受数据的约定制度。

**PCI-Express(peripheral component interconnect express),简称PCIE,**是一种高速串行计算机扩展总线标准,主要用于扩充计算机系统总线数据吞吐量以及提高设备通信速度。即是总线,也是协议。作为一种总线标准,PCIe定义了设备间的物理连接方式和电气特性。作为一种协议,PCIe定义了设备间数据传输的规则和格式12。PCIe协议包括物理层、数据链路层、事务层等多个层次,每个层次都有其特定的功能

PCIe速度

PCle 发展到现在,从 PCle 1.0、PCle 2.0,PCIe 3.0 -->PCIe 6.0 速度一代比一代快。如下表:

| 连接速度 | x 1 | x 2 | x 4 | x 8 | x 12 | x 16 | x 32 |

|---|---|---|---|---|---|---|---|

| PCIe 1.0带宽/(GB/s) | 0.5 | 1 | 2 | 4 | 6 | 8 | 16 |

| PCIe 2.0带宽/(GB/s) | 1 | 2 | 4 | 8 | 12 | 16 | 32 |

| PCIe 3.0带宽/(GB/s) | ~2 | ~4 | ~8 | ~16 | ~24 | ~32 | ~64 |

连接速度这一行的x1、x2、 x4等指PCIe连接的通道数(Lane)。就像高速公路有单车道、2 车道、4 车道一样(见图 8-1),PCIe 连接也可以有多个通道,只不过8车道及以上的公路不常见,而PCle最多可以有32个Lane。

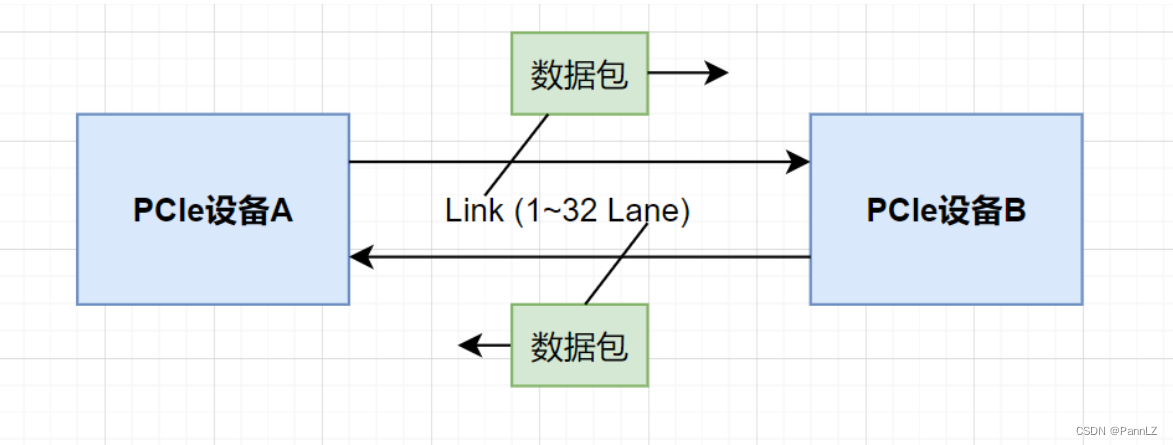

两个设备之间的PCIe连接称为**Link**。

两个PCIe设备之间,有独立的发送和接受数据通道,数据可以往两个方向传输。

表中的带宽,如PCIe 3.0 x 1,带宽为2 GB/s,是指双向带宽,即读写带宽。如果单独指读或者写,带宽应减半。

表中带宽是如何计算的:

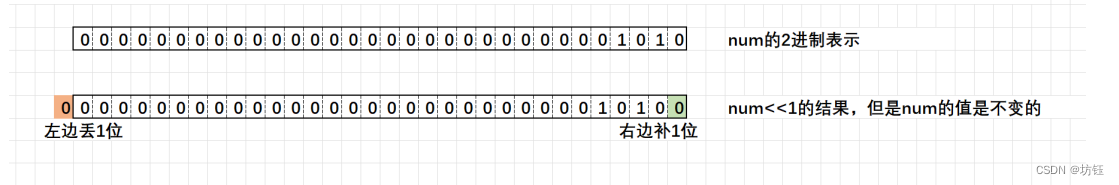

PCIe是串行总线,PCIe 1.0的线上位传输速率为2.5 Gb/s,物理层使用8/10编码,即8位的数据,实际在物理线路上是需要传输10位的,多余的2位用来校验。因此:

PCIe 1.0 ×1的带宽=(2.5 GB/s×2(双向通道))/10=0.5 GB/s

PCIe是从PCI发展过来的,PCIe中的“e”是express的简称,表示“快”。PCIe怎么能比PCI(或者PCI-X)快呢?那是因为PCIe在物理传输上跟PCI有着本质的区别:PCI使用并口传输数据,而PCIe使用串口传输数据。PCI并行总线单个时钟周期可以传输32 b或64 b数据,为什么比不了单个时钟周期传输1 b数据的串行总线呢?

在实际时钟频率比较低的情况下,并口因为可以同时传输若干比特位,速率确实比串口快。随着技术的发展,要求数据传输速率越来越快,要求时钟频率也越来越快,但是并行总线时钟频率不是想快就能快的。

在发送端,数据在某个时钟沿传出去,在接收端,数据在下个时钟沿接受。因此,要想使接收端能正确采集到数据,时钟 的周期必须大于数据传输的时间。受限于数据传 输时间(该时间随着数据线长度的增加而增加),时钟频率不能做得太高。另外,时钟信号 在线上传输的时候,也会存在相位偏移(Clock Skew), 影响接收端的数据采集。由于采用 并行传输,接收端必须等最慢的那个比特位数据到了以后才能锁住整个数据。

PCIe 使用串行总线进行数据传输就没有上述问题。它没有外部时钟信息,它的时钟信 息通过8/10编码或者128/130编码嵌在数据流中,接收端可以从数据流里面恢复时钟信息, 因此,它不受数据在线上传输时间的限制,导线多长、数据传输频率多快都没有问题。没有 外部时钟信息,自然就没有所谓的相位偏移问题。由于是串行传输,只有一位数据在传输, 所以也不存在信号偏移 (Signal Skew) 问题。但是,如果使用多条Lane 传输数据(串行中 又有并行),那么这个问题就又回来了,因为接收端同样要等最慢的那个Lane 上的数据到达 后才能处理整个数据。不过,PCle 自己能解决这个问题。