目录

1 .1配置模式

1.1.1 主模式

1.1.2 从模式

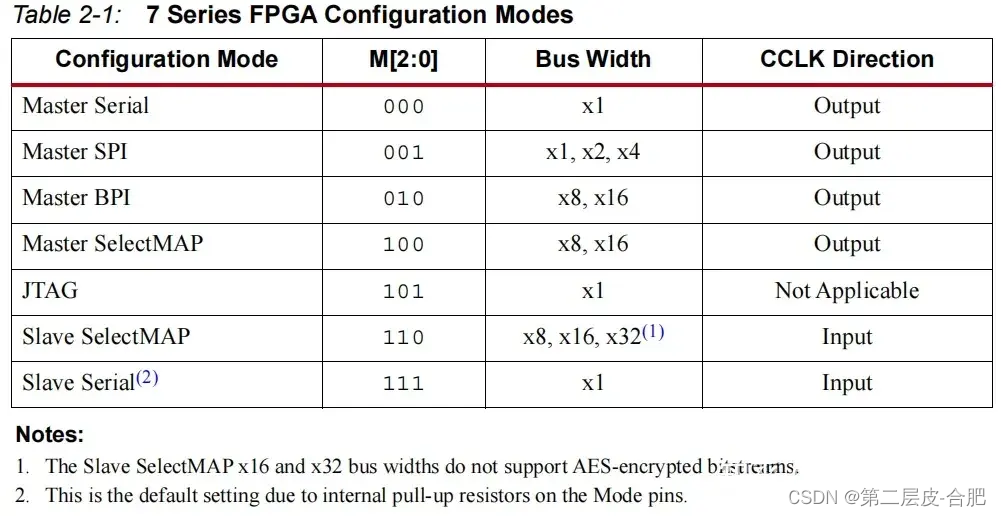

1.2 7种配置模式

1.2.1 主串配置模式

1.2.2 从串配置模式

编辑1.2.3 主并配置模式

1.2.4 从并配置模式

1.2.5 JTAG配置模式

编辑1.2.6 主SPI配置模式

编辑1.2.7 主BPI配置模式

1.2.8 FPGA BPI加载时间(参考xapp587)

2、BPI FLASH配置实例

3、BPI FLASH配置时序

4、配置时钟最大频率计算

1 .1配置模式

由于Xilinx FPGA配置数据存储在CMOS配置锁存器(CCL)中,因此必须在断电后重新配置。比特流每次都通过特定的配置引脚加载到器件中。常用的配置模式可以分为:

主模式:主串口、主SelectMAP(并行×8 ×16)、主SPI(×1 ×2 ×4)、主BPI(×8 ×16

从模式:从串口、从SeletMAP(并行×8 ×16 ×32)J

TAG模式(调试模式)

系统模式(多片配置模式)

通过在专用模式输入引脚M[2:0]上设置适当的电平来选择特定的配置模式。M2、M1和M0模式引脚应通过上拉或下拉电阻(≤1kΩ)或直接接地或VCCO_0设置为恒定直流电压电平。在配置期间和配置之后不应切换模式引脚。

无论模式引脚M[2:0]设置如何,JTAG/边界扫描配置接口始终可用。

主模式和从模式指的是配置时钟CCLK的方向,在主模式中CCLK为输出,从模式中CCLK为输入。

由于CCLK引脚存在容差,因此可以使用比CCLK更精准的时钟EMCCLK引脚。启用外部主配置时钟(EMCCLK)选项,全速加载配置程序,具体见UG470 2章节。

1.1.1 主模式

FPGA自加载配置模式,通常称为主模式,可用于串行或并行数据路径。主模式利用各种类型的非易失性存储器(如Flash、EEPROM等)来存储FPGA的配置信息。FPGA在驱动配置逻辑的内部振荡器中生成配置时钟信号,并在CCLK输出引脚上可见。

【UG470】的表1-1提供了7系列生成比特流长度,可以注意到不同型号的FPGA所需的最小配置Flash容量不同:

1.1.2 从模式

外部控制加载FPGA配置模式,通常称为从模式,也可用于串行或并行数据路径。在从模式下,处理器、微控制器、DSP处理器或测试仪等外部“智能代理”将配置映像下载到FPGA中,从配置模式的优势在于FPGA比特流几乎可以驻留在整个系统中的任何位置。

1.2 7种配置模式

1.2.1 主串配置模式

在该模式下,FPGA向外部的非易失性串行数据存储器或者控制器发出CCLK时钟信号,配置数据会以串行方式载入FPGA,在前几代的FPGA中,存储器通常选择Xilinx官方的XCF串行系列存储器,并给出了相应的设计原理图,但在7系列FPGA中,这种方式被放弃了,其官方的配置文档里并无主串配置模式的相关详细描述。

1.2.2 从串配置模式

如下图1所示,在该模式下,由外部的处理器提供CCLK时钟和串行数据,用户实现起来相对复杂,不够大众化,不做介绍。

1.2.3 主并配置模式

官方文档并无详细设计描述,无从参考。

1.2.4 从并配置模式

如下图所示,在该模式下,外部处理器提供配置时钟和并行的配置数据,该模式相对于串行方式来说,配置的速度快,但设计稍微复杂。下图为官方给出的详细配置原理图,该模式同样使用较少。

1.2.5 JTAG配置模式

如下图所示,该模式属于工程调试模式,咱们在设计FPGA时必带这种模式。该模式只能在线配置和调试FPGA,无法存储逻辑代码。最简单的操作方式是使用Xilinx官方提供的专用JTAG调试下载器,但同时也允许用户通过外部处理器自行设计JTAG的数据协议来配置FPGA逻辑代码。再次强调,该模式只是一个调试模式。

1.2.6 主SPI配置模式

这种模式应该算是咱们使用最广泛的配置模式了,通过外挂一个SPI存储器即可。通常该模式和JTAG配置模式一起设计。JTAG模式在线调试好逻辑代码后,将该逻辑代码存储在SPI存储器中,以后FPGA上电后就会自动载入存储器中的逻辑代码。下图为官方给出的详细配置原理图。

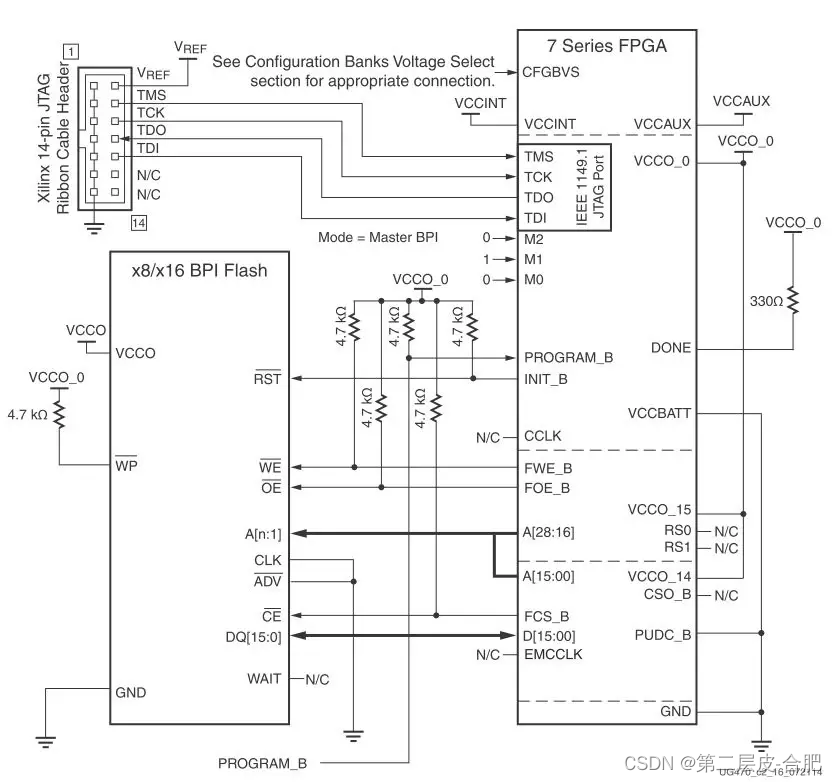

1.2.7 主BPI配置模式

该模式的时钟CCLK同样由FPGA提供,并行的数据比SPI模式的串行数据配置速度要快,但设计稍微复杂一点。下图为官方给出的详细配置原理图:

我们在设计FPGA时,基本上都是采用JTAG配置模式+主SPI配置模式或者JTAG配置模式+主BPI配置模式。前者用于一般的应用,后者用于对FPGA上电后逻辑代码载入速度有较高要求的应用。

1.2.8 FPGA BPI加载时间(参考xapp587)

并行NOR FLASH是存储和传输比特流的常用选择,因为×16的数据总线可提供比SPI FLASH更快的配置,此外,NOR FLASH还可提供更大的容量。

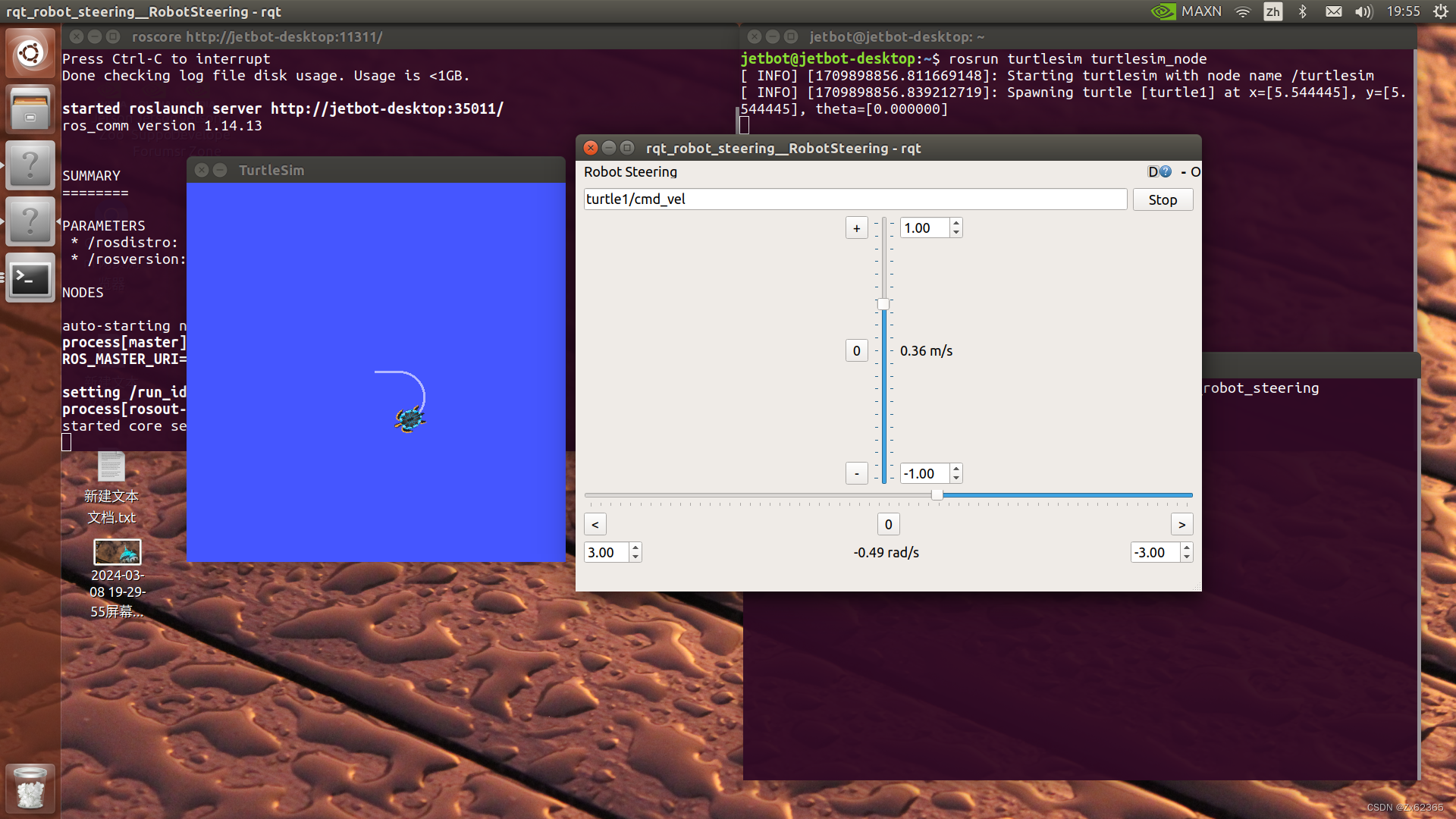

BPI配置接口

CCLK:该引脚是除JTAG之外的所有配置模式的初始配置时钟源。同步读取模式下CCLK必须与BPI FLASH相连接以便顺序输出数据;异步读取模式下CCLK悬空,不直接为BPI FLASH提供时钟,由FPGA内部使用来生成地址和采样数据。

EMCCLK:该引脚为外部主配置时钟输入。此输入提供外部时钟,FPGA配置控制器在从比特流标头读取EMCCLK命令后切换使用此时钟而不是CCLK(内部配置时钟)。EMCCLK可实现更可预测的配置时间,因为时钟容差由所选的外部振荡器决定。(与SPI FLASH相同)

RS[1:0]:预留引脚。用于多bit程序,以在多版本之间进行选择并提供回退功能。当检测到配置错误时,RS [1:0]被主动为低以加载回退bit文件。

2、BPI FLASH配置实例

下图中EMCCLK外部输入80MHz时钟,RS引脚为预留引脚,如不需要修订程序则悬空处理。

3、BPI FLASH配置时序

在BPI配置模式下,FPGA始终以异步读取模式从NOR flash开始读取。即从给定的起始地址递增地址总线,NOR flash发送回比特流数据。

当在比特流头中读取同步命令时,FPGA配置控制器对连接的BPI FLASH的读配置寄存器(RCR)执行异步写操作以设置同步模式和延迟位。

在成功写入RCR之后,FPGA控制器然后启动同步读取并读取比特流数据内容。配置完成后,保持同步读取模式。

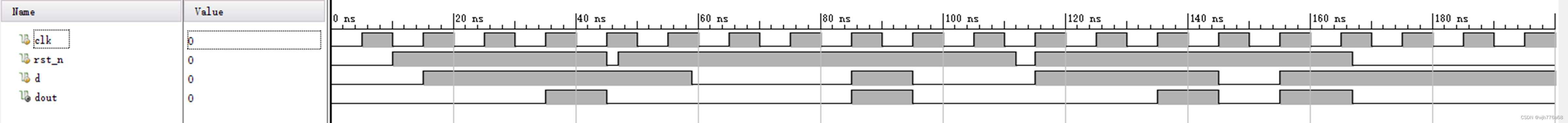

BPI配置时序波形图

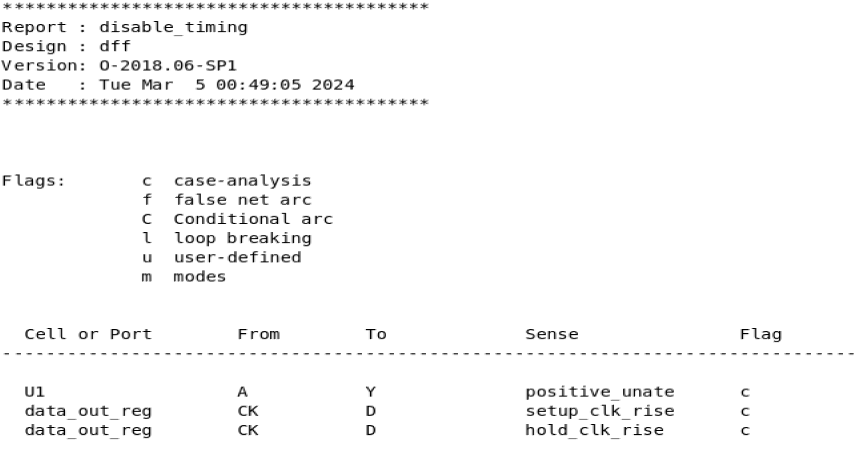

4、配置时钟最大频率计算

要计算传输的最大频率需要考虑到BPI FLASH输出时钟规范(BPI datasheet)及电路的延迟。公式如下:

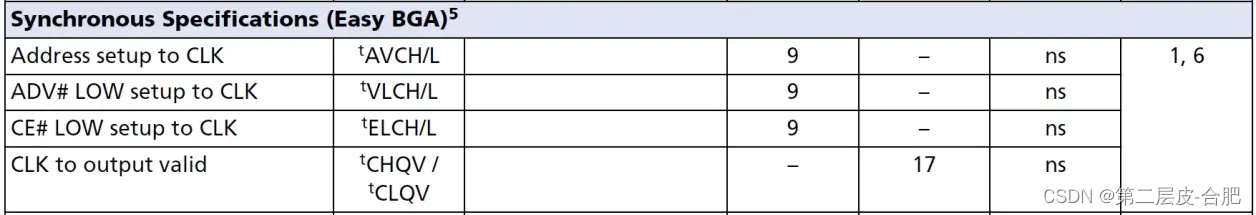

TCHQV(Flash clock to out):BPI FLASH手册中有明确说明该时钟的输出数值。如PC28F00AP30TF,其TCHQV为17ns,如下图: