目录

线网(net)

变量(variable)

线网和变量的区别

向量

数组

参考《Verilog 编程艺术》魏家明著

线网(net)

用于表示结构体(如逻辑门)之间的连接。除了 trireg 之外,所有其他的线网类型都不能保存值,线网的值是由driver决定的。例如由连续赋值驱动或由逻辑门驱动。如果driver没有驱动线网,那么线网的值是z,但是tri0,tri1,trireg除外。tri0将是0,tri1将是1,而trireg将保持之前driver的驱动值。

线网的类型:wire,wand,wor,tri,triand,trior,tri0,tri1,trireg,uwire,supply0,supply1。

wire和tri:

一样的,具有同样的语法和功能,提供两个名字是用于不同方面的建模:wire用于逻辑门的驱动或连续赋值的驱动,而tri同于多driver驱动。

当多个具有相同驱动强度的driver驱动同一个wire和tri线网出现逻辑冲突时,线网的值是x。

wor,wand,trior,triand:

属于线逻辑(model wired logic)类型。用于解决多个driver驱动同一个线网时出现的逻辑冲突。wor和trior实现线或逻辑,wand和triand实现线与逻辑。

tri0和tri1:

tri0用于表示带有下拉电阻的线网。当没有driver驱动tri0线网时,它的值是0,强度是pull。

tri1用于表示带有上拉电阻的线网,当没有driver驱动tri1线网时,它的值是1,强度是pull。

uwire:

只能被一个driver驱动,如果被多个driver驱动,编译会报错。

supply0,supply1:

用于模拟电源,就是只提供0和1值的线网,通常只在Vendor提供的标准单元库中使用,平常不用。

驱动强度(driver strength):

包括:

用于表示0的强度:highz0,supply0,strong0,pull0,weak0

用于表示1的强度:highz1,supply1,strong1,pull1,weak1

变量(variable)

是数据存储单元的抽象,具有如下特征:

1/变量会保持每次赋给它的值,直到下一次赋值给它。当过程快被触发时,过程块中的赋值就会改变变量的值。

2/reg,time和integer的初始化值是x,real和realtime的初始化值是0.0。

3/对reg的赋值是过程赋值(阻塞赋值和非阻塞赋值),reg能够模拟硬件寄存器。

4/可以把负值赋给线网和变量,只有integer,real,realtime,reg signed和net signed才能保持符号标志,而time,reg unsigned和net unsigned 则把赋给它们的值都当作无符号数处理。

5/integer等价于reg signed [31:0];time等价于reg unsigned[63:0]

6/real和realtime是等价的,都是64-bit双精度浮点数,只不过realtime变量常和$realtime函数一起用。

7/不能对real和realtime使用位索引和部分索引。

线网和变量的区别

任何过程赋值(procedural assignment)的左侧变量(LHS,left hand side)必须声明为reg,除此之外使用的变量必须声明为wire,没有例外。

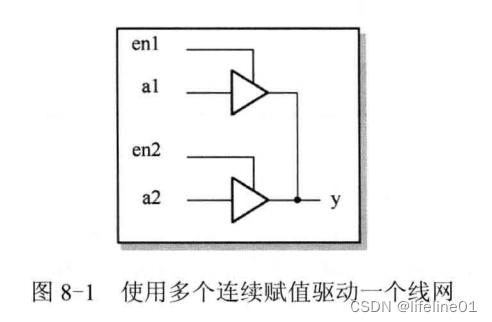

连续赋值设置线网的驱动,多个driver可以同时驱动同一个线网。例如:

module drivers1 (input a1, en1, a2, en2,output y

);assign y = en1 ? a1 : 1'bz;assign y = en2 ? a2 : 1'bz;endmodule

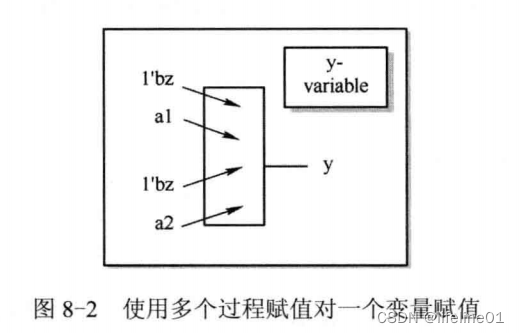

过程赋值(例如always块)使变量发生变化。

module drivers1 (input a1, en1, a2, en2,output reg y

);always @(a1 or en1) beginif (en1)y = a1;elsey = 1'bz;endalways @(a2 or en2) beginif (en2)y = a2;elsey = 1'bz;endendmodule

向量

标量(scalar)是没有范围声明的1-bit的线网(net)或reg。

向量(vector)是带有范围声明的multi-bit的线网(net)或reg。

例子:

wand w;

wire w1, w2;

tri [15:0] busa;

reg a;

reg [3:0] v;数组

1/数组的元素可以是标量也可以是向量。

2/数组的维数可以是一维,二维,多维。

3/数组的引用可以针对某一个元素或某一个元素的一部分(使用bit-select或part-select)

4/通常把一维数组称为memory。

例如:

reg x[11:0]; // 一维数组

reg [0:7] x[5:0]; // 八个一维数组,每个数组包含6个元素。

reg [31:0] x [127:0];

reg arrayb [7:0][0:255];

wire warray [7:0][0:255];二维数组表示图像

reg [23:0] image_data[0:800-1][0:800-1];

wire [23:0] piexl = image_data[x][y]; // (x,y)的像素

wire [7:0] color_r = image_data[x][y][23:16]; // rgb_r

wire [7:0] color_g = image_data[x][y][15:8]; // rgb_g

wire [7:0] color_b = image_data[x][y][7:0]; // rgb_b