文章目录

- 概述:

- 一、TXUSRCLK和TXUSRCLK2作用和关系

- 总结

- 二、TXUSRCLK和TXUSRCLK2产生

- 1、TXOUTCLK在2字节或4字节模式下驱动GTX/GTH收发器TX

- 2、TXOUTCLK 在 4 字节或 8 字节模式下驱动 GTX/GTH 收发器 TX

- 总结:

概述:

功能描述:

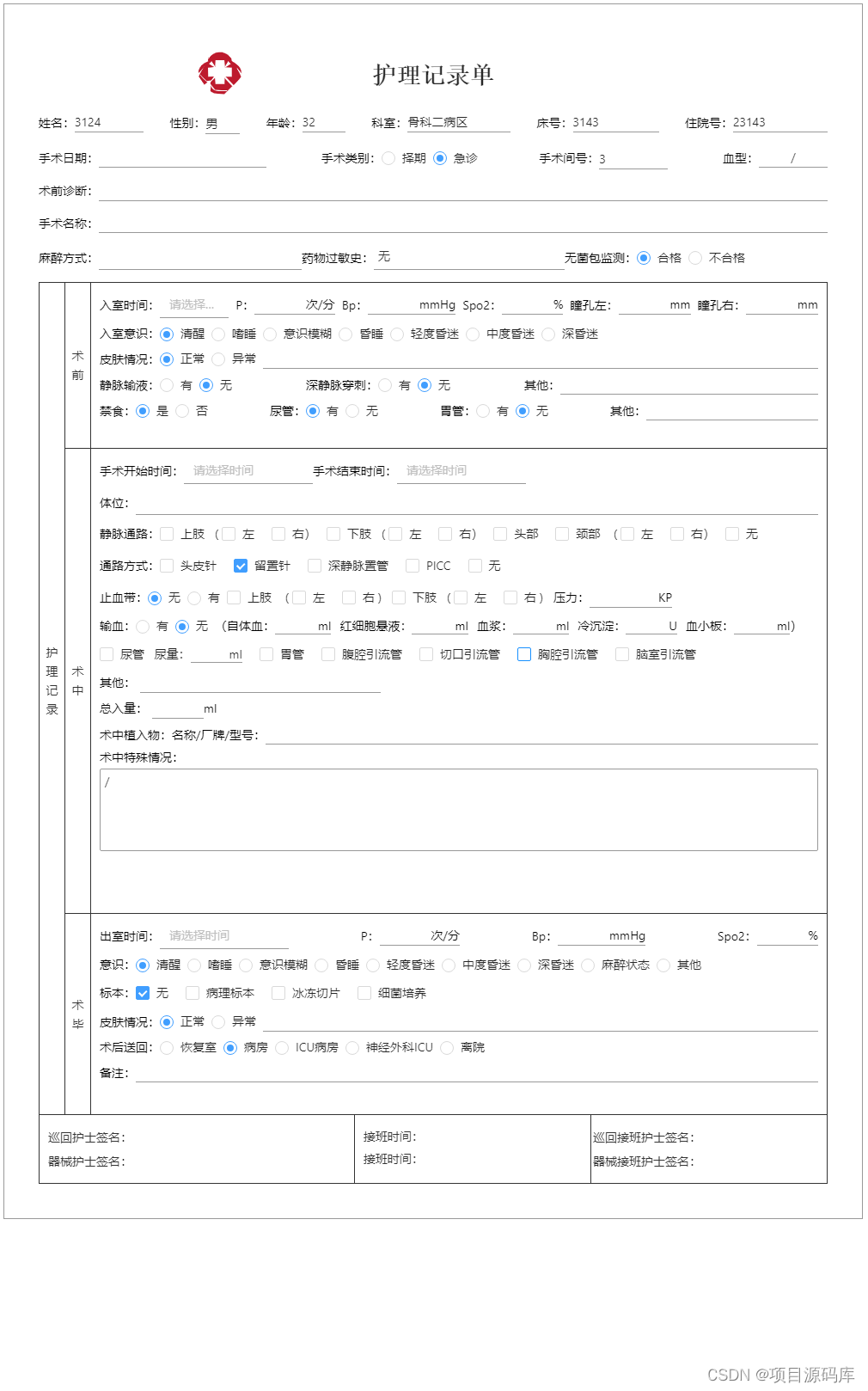

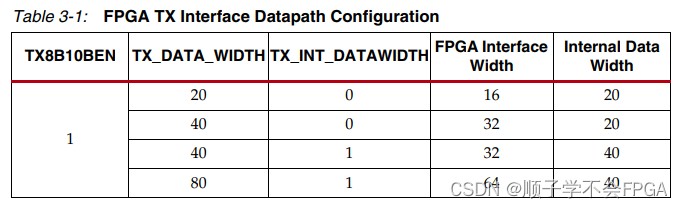

FPGA的TX接口是FPGA与GTX/GTH收发器TX数据路径的通道。应用程序通过在TXUSRCLK2的上升沿写入数据到TXDATA端口来通过GTX/GTH收发器传输数据。端口的宽度可以配置为两个、四个或八个字节宽。端口的实际宽度取决于TX_DATA_WIDTH和TX_INT_DATAWIDTH属性以及TX8B10BEN端口设置。端口宽度可以是16、20、32、40、64和80位。接口上的并行时钟(TXUSRCLK2)的速率由TX线速率、TXDATA端口的宽度以及是否启用8B/10B编码来确定。发送机内部的PCS逻辑需要提供第二个并行时钟(TXUSRCLK)。本节说明如何驱动并行时钟,并解释了这些时钟的正确操作的约束。最高的发送机数据速率要求有一个8字节的接口以实现指定操作范围内的TXUSRCLK2速率。

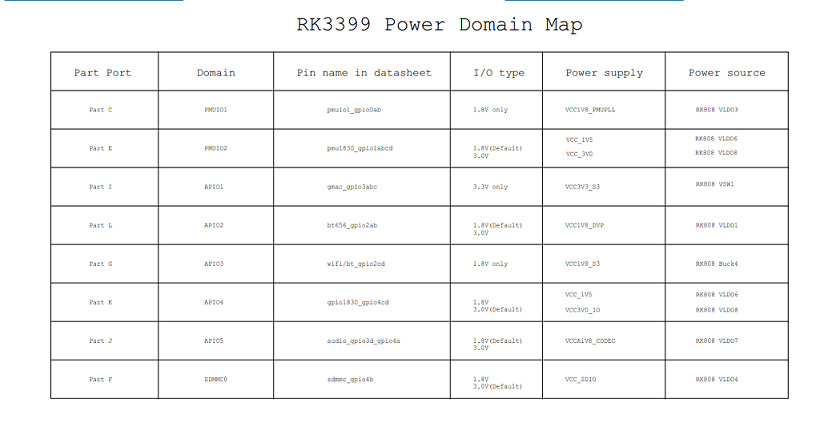

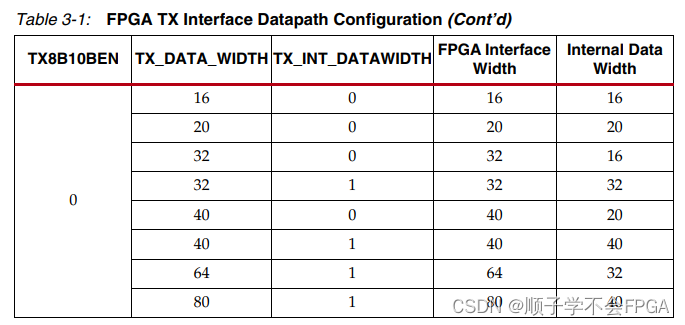

接口宽度配置:

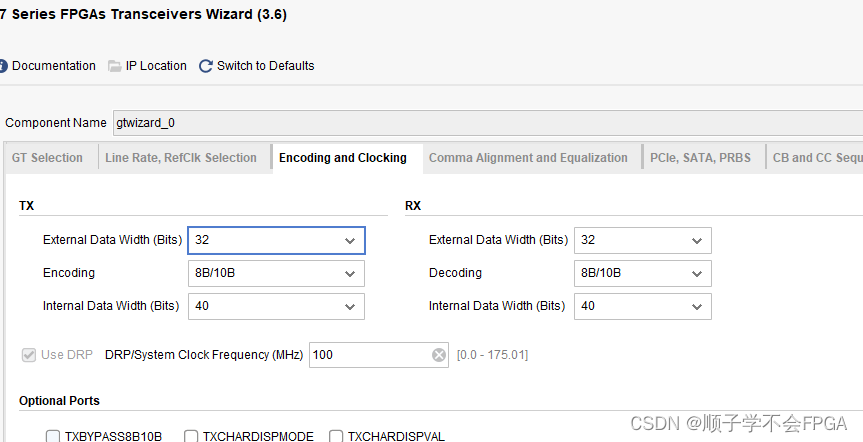

7系列FPGA GTX/GTH收发器包含2字节和4字节的内部数据路径,可以通过设置TX_INT_DATAWIDTH属性进行配置。FPGA接口宽度可以通过设置TX_DATA_WIDTH属性进行配置。当启用8B/10B编码器时,必须将TX_DATA_WIDTH属性配置为20位、40位或80位,在这种情况下,FPGA TX接口仅使用TXDATA端口。例如,当FPGA接口宽度为16时,将使用TXDATA[15:0]。当绕过8B/10B编码器时,TX_DATA_WIDTH属性可以配置为任何可用的宽度:16、20、32、40、64或80位。

个人理解:

我个人在使用的时候只用过开启8B10B情况,一般来说我们都应该要开启这个的,在表3-3当中介绍了TXUSRCLK和TXUSRCLK2频率之间的关系的描述,当我们开启8B10B后,FPGA用户侧接口为16的时候GT内部的数据接口就应该是16/8 * 10,所以为20,FPGA侧为4字节32bit时,GT应该为40,当然也可以为20,那么久相当于将32拆开为俩个16进行编码,那么用于GT PCS的时钟就应该是FPGA侧数据时钟的俩倍,所以就有表3-3当中的频率关系,这个是我个人理解,有误可以讨论。

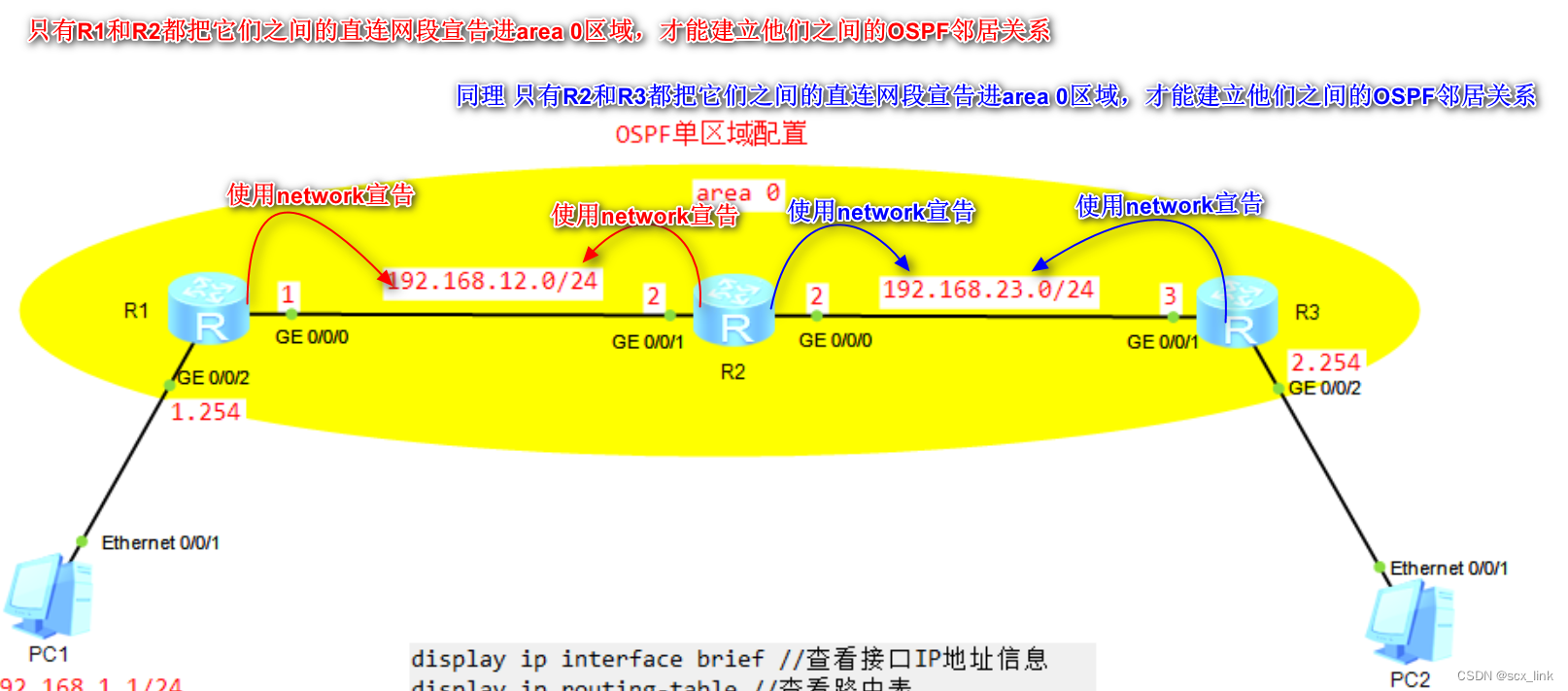

一、TXUSRCLK和TXUSRCLK2作用和关系

框图的最右边FPGA TX Interface,即FPGA TX接口,它是FPGA通往GT Transceiver TX数据通路的通道。FPGA TX 接口包含两个并行时钟,TXUSRCLK和TXUSRCLK2。

TXUSRCLK是GTX/GTH transceiver中PCS逻辑的内部时钟。TXUSRCLK所需的速率取决于GTXE2_CHANNEL/GTHE2_CHANNEL源的内部数据通路宽度和GTX/GTH发射器的TX线速率。

下面公式显示了如何计算TXUSRCLK的所需速率。

进入GTX/GTH Transceiver TX端的大多数信号都是在TXUSRCLK2的正沿上采样的。接口上的并行时钟(TXUSRCLK2)的速率由TX线路速率、TXDATA端口的宽度以及是否启用8B/10B编码决定。TXUSRCLK2和TXUSRCLK有一个基于TX_DATA_WIDTH和TX_INT_DATAWIDTH设置的固定速率关系。下显示了每个TX_DATA_WIDTH和TX_INT_DATAWIDTH值的TXUSRCLK2和TXUSRCLK之间的关系。当线路速率大于6.6 Gb/s时,通过将TX_INT_DATAWIDTH设置为1,需要一个4字节的内部数据路径。

对于TXUSRCLK和TXUSRCL2,必须遵守这些关于时钟之间关系的规则。

TXUSRCLK和TXUSRCLK2必须是正边对齐的,它们之间的偏移尽可能小。因此,低偏移的时钟资源(BUFG、BUFH、和 BUFR)应被用来驱动TXUSRCLK和TXUSRCLK2。即使它们可能以不同的频率运行,TXUSRCLK、TXUSRCLK2和 Transmitter参考时钟必须有相同的振荡器作为其来源。因此 TXUSRCLK和TXUSRCLK2必须是发射器参考时钟的倍频或分频版本。

总结

TXUSRCLK以及TXUSRCLK2的作用以及关系:

- TXUSRCLK是GTX/GTH transceiver中PCS逻辑的内部时钟。

- TXUSRCLK2是进入GTX/GTH Transceiver TX端所有信号的主要同步时钟。

对于TXUSRCLK和TXUSRCL2,必须遵守这些关于时钟之间关系的规则。

- TXUSRCLK和TXUSRCLK2必须是正边对齐的,它们之间的偏移尽可能小。因此,低偏移的时钟资源(BUFG、BUFH、和 BUFR)应被用来驱动TXUSRCLK和TXUSRCLK2。

- 即使它们可能以不同的频率运行,TXUSRCLK、TXUSRCLK2和 Transmitter参考时钟必须有相同的振荡器作为其来源。因此 TXUSRCLK和TXUSRCLK2必须是发射器参考时钟的倍频或分频版本。

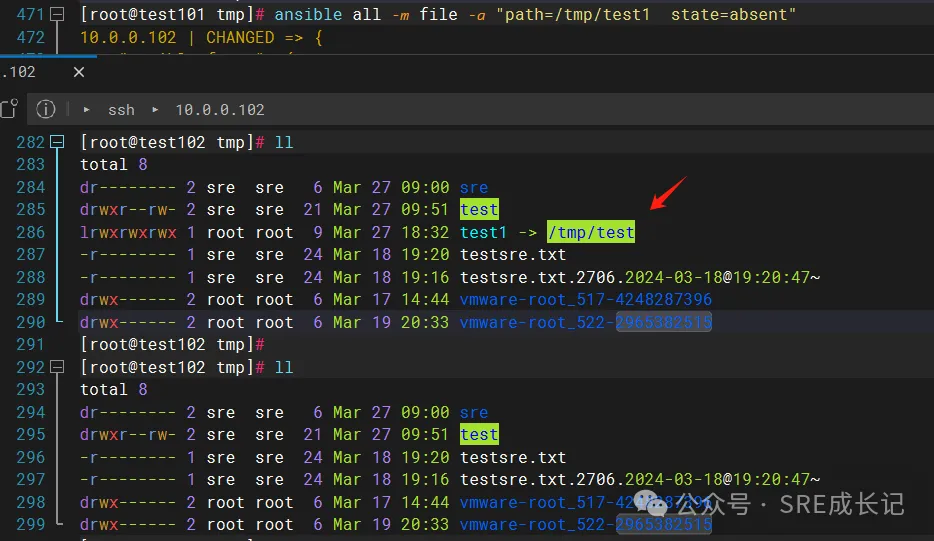

二、TXUSRCLK和TXUSRCLK2产生

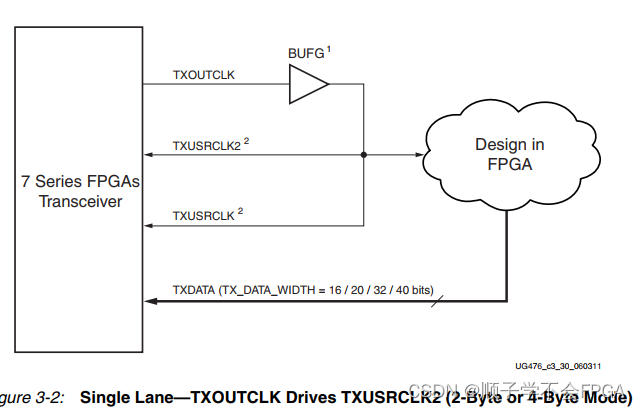

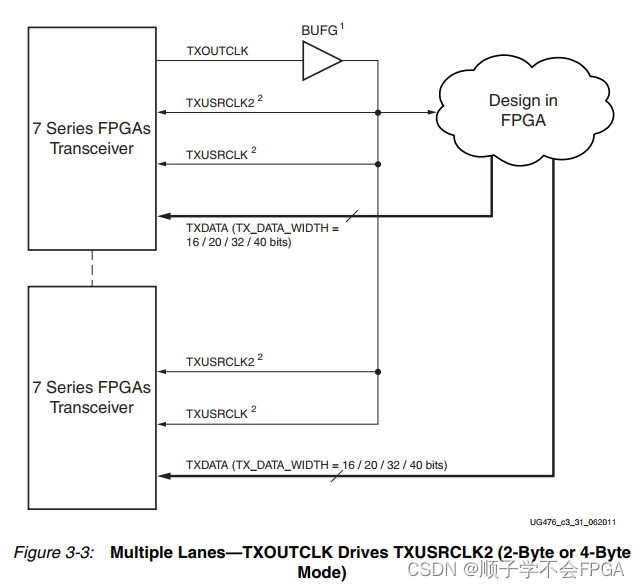

1、TXOUTCLK在2字节或4字节模式下驱动GTX/GTH收发器TX

TXOUTCLK用于驱动单通道配置中的2字节模式(TX_DATA_WIDTH=16或20,TX_INT_DATWIDTH=0)或4字节模式(TX_DATA_WIDTH=32或40,TX_INT_DATWIDTH=1)的TXUSRCLK和TXUSRCK2。在这两种情况下,TXUSRCLK2的频率都等于TXUSRCLK。

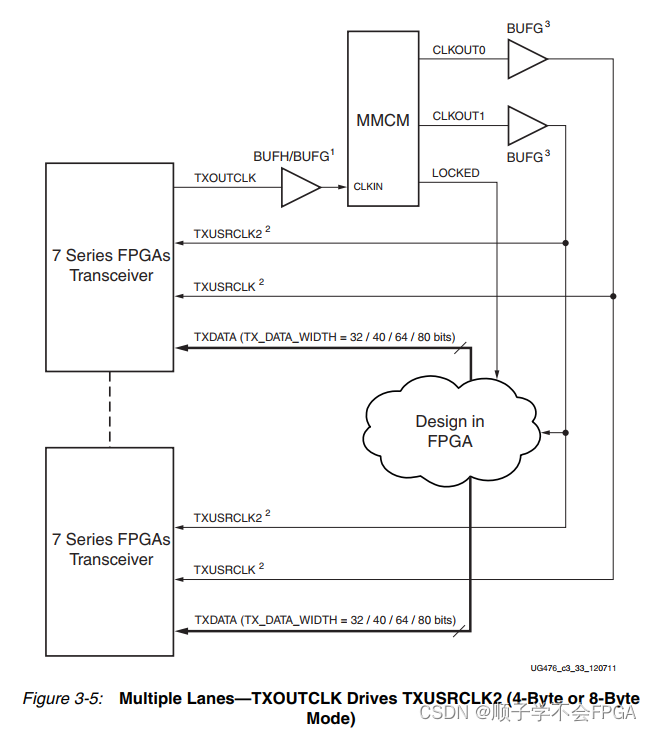

类似地,如下图

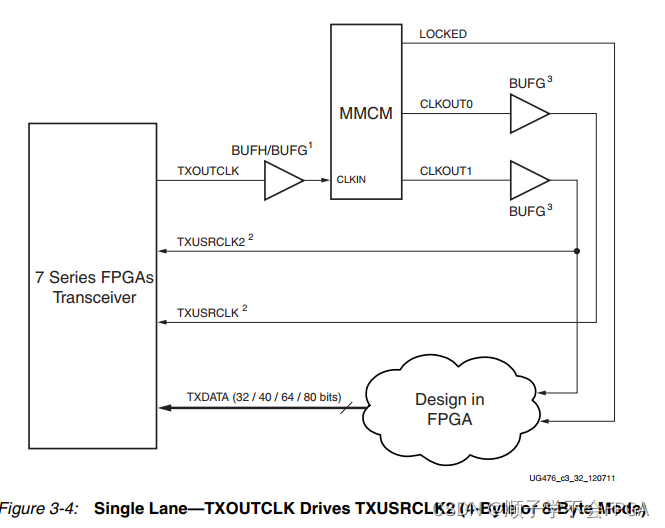

2、TXOUTCLK 在 4 字节或 8 字节模式下驱动 GTX/GTH 收发器 TX

TXOUTCLK用于驱动TXUSRCLK2的4字节模式(TX_DATA_WIDTH = 32或40,TX_INT_DATWIDTH = 0)或8字节模式(TX_DATA_WIDTH = 64或80,TX_INT_DATWIDTH = 1)。在这两种情况下,TXUSRCLK2的频率都等于TXUSRCLK频率的一半。MMCM是位于器件上半部的时钟管理单元(CMT)的一部分,它只能驱动器件上半部的BUFG。同样,位于下半部的MMCM也只能驱动下半部的BUFG

注:在Kintex™-7器件中,需要BUFH/BUFG。在Virtex-7器件中,BUFH/BUFG是不需要的。

总结:

在我们使用IP核的时候会选择数据通道位宽和是否开启8B/10B,然后我们直接使用example design当中的gtwizard_0_GT_USRCLK_SOURCE 模块即可,这个模块帮我们把TXUSRCLK和TXUSRCLK2频率什么的都算好了。

gtwizard_0_GT_USRCLK_SOURCE gt_usrclk_source

(.GT0_TXUSRCLK_OUT (gt0_txusrclk_i ),.GT0_TXUSRCLK2_OUT (gt0_txusrclk2_i ),.GT0_TXOUTCLK_IN (gt0_txoutclk_i ),.GT0_TXCLK_LOCK_OUT (gt0_txmmcm_lock_i ),.GT0_TX_MMCM_RESET_IN (gt0_txmmcm_reset_i ),.GT0_RXUSRCLK_OUT (gt0_rxusrclk_i ),.GT0_RXUSRCLK2_OUT (gt0_rxusrclk2_i ),.GT0_RXCLK_LOCK_OUT (gt0_rxmmcm_lock_i ),.GT0_RX_MMCM_RESET_IN (gt0_rxmmcm_reset_i )

);

![[机器学习]练习-KNN算法](https://img-blog.csdnimg.cn/direct/2c60f4dfbffd4815b1d39ab68827e28b.png)