本文主要介绍以下几点:

- 复位的作用及什么时候需要复位

- 复位的分类

- 全局复位、局部复位的目的

- 如何选择全局复位和局部复位

- 同步复位、异步复位及异步复位同步释放的原理、优缺点

注:参考文章在文末给出

目录

- 一、复位信号的作用和分类

- 1.复位信号的作用

- 2.复位信号的分类

- 二、全局复位和局部复位

- 1.全局复位

- 2.局部复位

- 3.如何使用全局复位和局部复位

- (1)全局复位

- (2)局部复位

- 三、同步复位和异步复位

- 1.定义

- 2.同步复位

- (1)同步复位实例

- (2)同步复位的优劣

- (3)不适合同步复位的情况

- 3.异步复位

- (1)异步复位实例

- (2)异步复位的优劣

- 4.Xilinx平台复位信号注意事项

- (1)高电平有效

- (2)综合注意事项

- 四、异步复位同步释放

- 1.为什么会出现异步复位同步释放

- 2.原理

- 3.实例

- 4.异步复位同步释放相比异步复位的优势

- 五、过滤复位信号的毛刺

一、复位信号的作用和分类

1.复位信号的作用

复位信号的作用主要如下:

(1)使电路在仿真时具有可知的初始值,避免出现不定态;

(1)为寄存器赋初值,使系统状态机在上电后能够进入初始状态;

(2)使系统能够在发生故障的时候恢复到初始状态;

2.复位信号的分类

复位信号的分类可以从两方面考虑:

①从复位信号驱动的寄存器数量来看

复位信号可以分为全局复位和局部复位

②从复位信号与时钟的关系来看

复位信号可以分为同步复位和异步复位

二、全局复位和局部复位

1.全局复位

全局复位是对整个FPGA芯片进行复位,将所有逻辑和寄存器重置为初始状态。

2.局部复位

局部复位是对FPGA中特定的逻辑模块或寄存器组进行复位,只影响选定的部分。对于需要多个时钟区域内独立复位的设计,可以采用局部复位。

因为局部复位信号的扇出小,所以可以使用布线延时相对较小的本地布线资源,这样局部复位信号就能够很容易的满足时序要求,避免Recovery违例。

3.如何使用全局复位和局部复位

(1)全局复位

全局复位通常作为一个外部引脚来实现,用于在加电时初始化设计。这个全局复位引脚与任何其他输入引脚类似,对FPGA来说是异步的。设计时可以使用这个信号在FPGA内部对自己的设计进行异步或者同步复位。

但Xilinx官方不推荐使用全局复位,因为全局复位会占用许多逻辑和布线资源,导致布线拥挤,不利于时序收敛;再者扇出过大,很难满足时序要求。

(2)局部复位

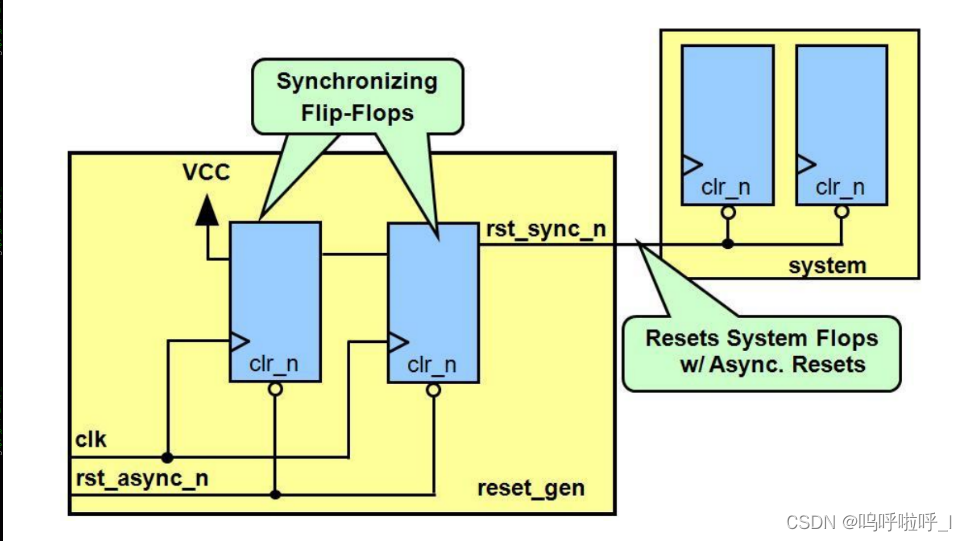

通过二级寄存器同步化外部的异步复位信号,然后复制不同的复位寄存器连到不同的模块来作为复位控制。如果单个模块的复位扇出太大,还可以在模块内部复制复位寄存器,减小单个扇出。需要注意的是,那些在数据路径上不需要复位的寄存器不要在代码中复位,因为这样会增加复位信号的扇出,并增加逻辑资源和降低逻辑速度

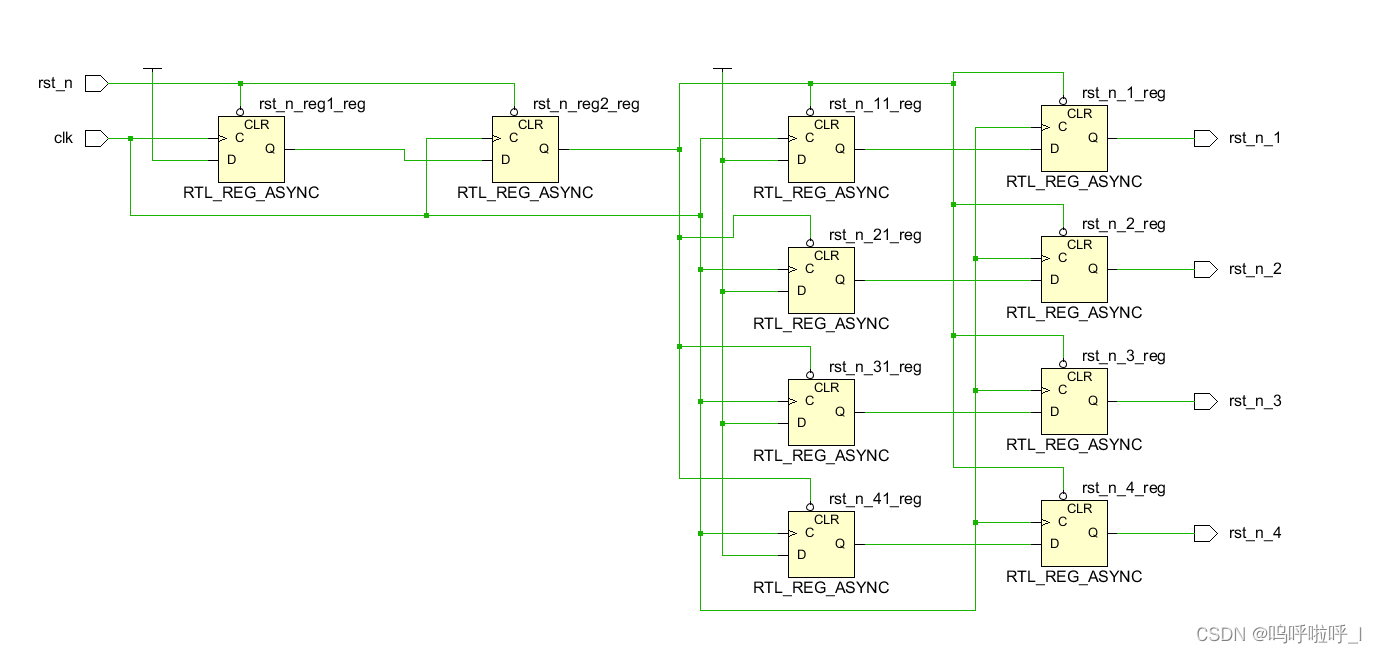

下面是一个局部复位的例子:

电路结构图如下:

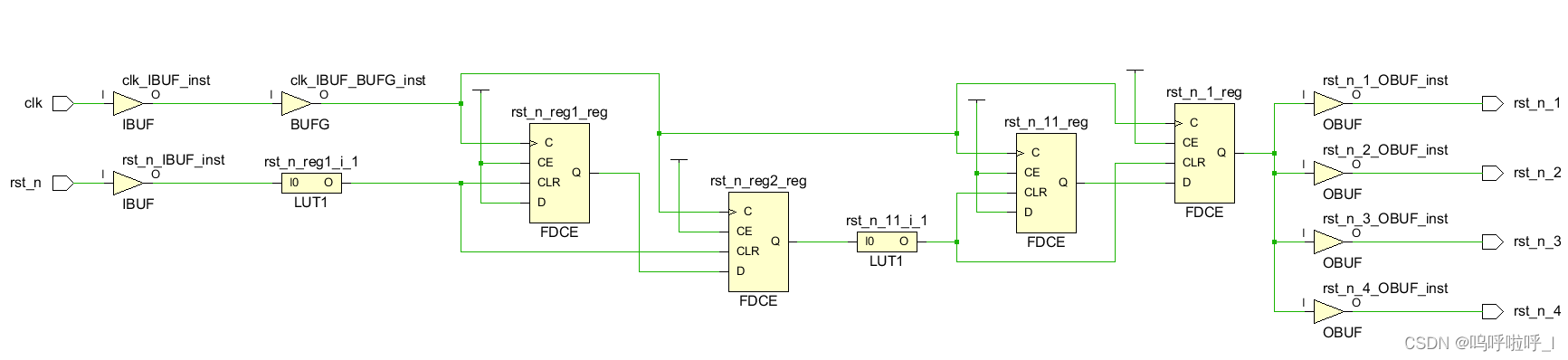

但是综合后的结果变成了通过一个寄存器加了四个OBUF来增加驱动能力。

三、同步复位和异步复位

1.定义

同步复位的复位和释放均在时钟边沿发生。

异步复位的复位信号与时钟无关,可以发生在任意时刻。

2.同步复位

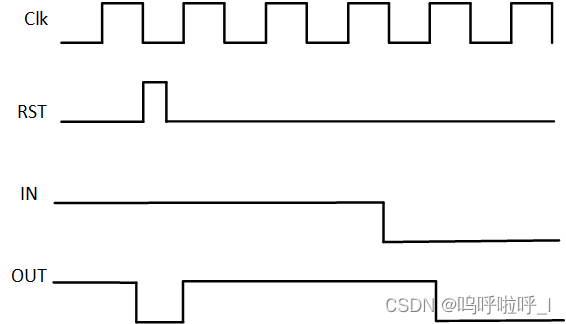

同步复位的示意图如下:

当复位信号为高电平有效时,在时钟上升沿到来后若复位信号为高电平,则D触发器复位,输出结果为0。

(1)同步复位实例

下面给出同步复位的Verilog示例、电路结构、综合结果:

module reset_test(input clk,input rst,input single_bit,output reg out);

always@(posedge clk)

beginif(rst)out<=1'b0;elseout<=single_bit;

end

endmodule

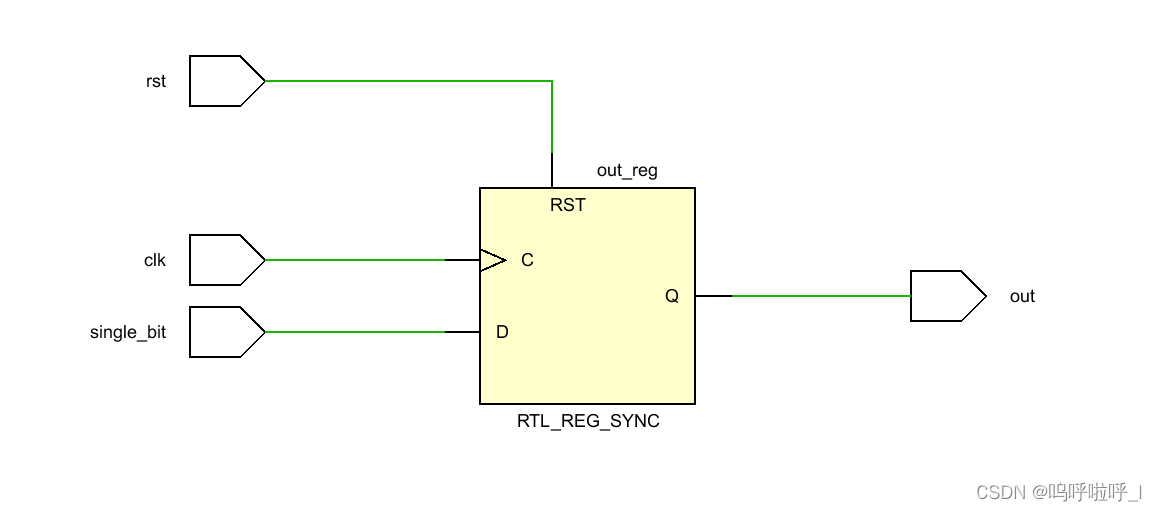

其电路结构如下,一个带同步复位的D触发器:

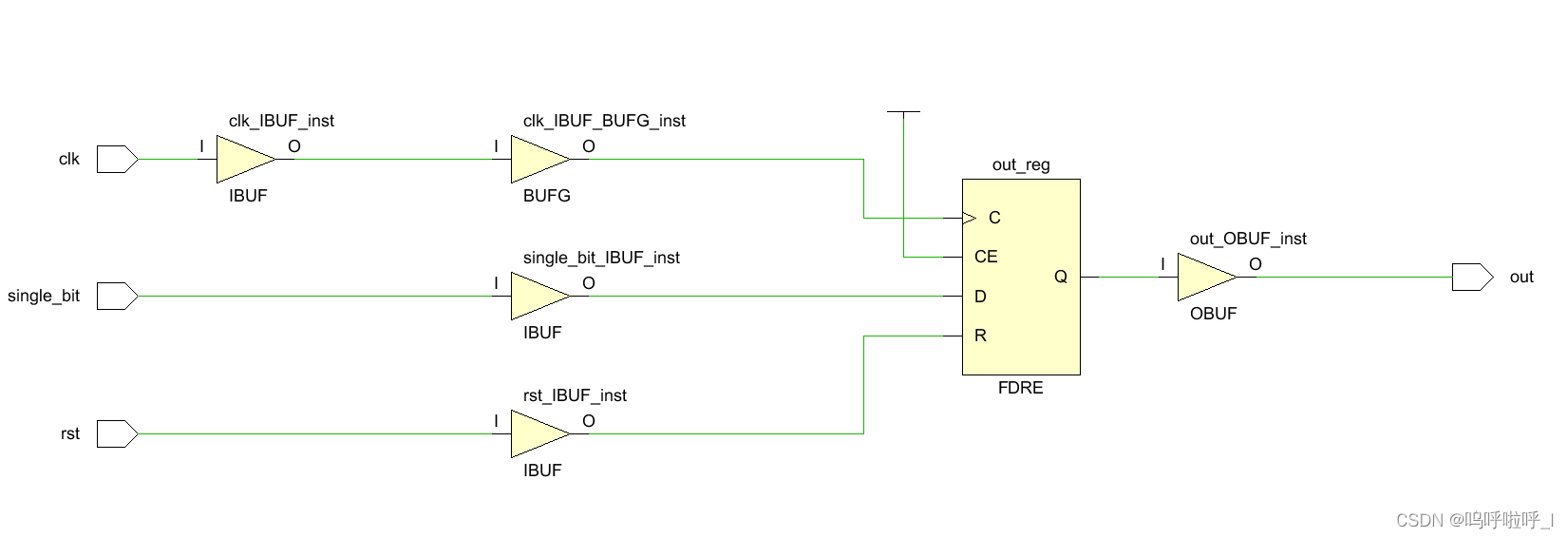

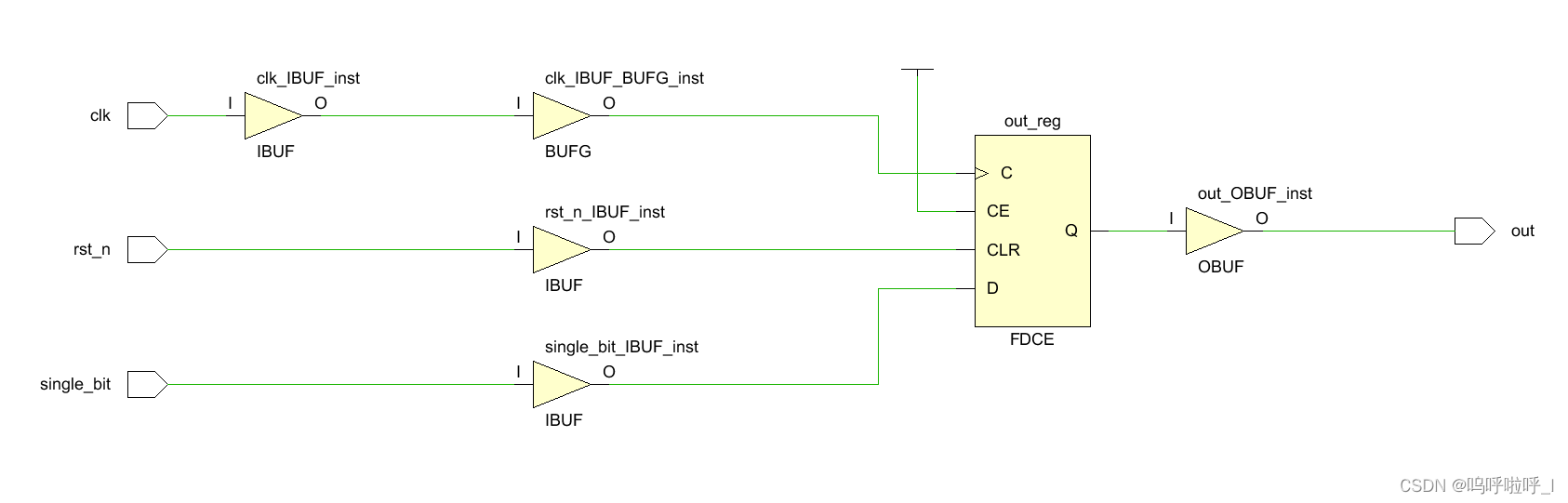

综合后的结果如下:

需要注意的是,上述的复位信号并非是直接由外部引脚接入,而是对其进行了同步操作后(一般为将其通过两级触发器),这样能够保证复位信号的宽度至少为一个时钟周期长度,复位信号能够被正确采样到。

(2)同步复位的优劣

同步复位的优势如下:

- 能够滤除高于时钟频率的毛刺,使系统更加稳定;

- 由于采用了同步复位,设计出来的电路均是同步电路,有利于时序分析

同步复位的劣势如下:

- 同步复位需要时钟参与;

- 复位信号的宽度要大于一个时钟周期,以免被当成毛刺率除掉

- 对于只有异步复位端口的DFF来说,需要额外的逻辑资源来实现同步复位

(3)不适合同步复位的情况

门控时钟电路并不适合用同步复位,因为同步复位与时钟息息相关,当门控时钟由于使能信号无效而关闭时,复位信号将不能正常工作。

3.异步复位

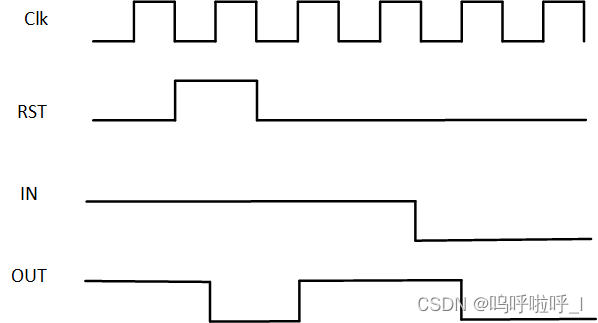

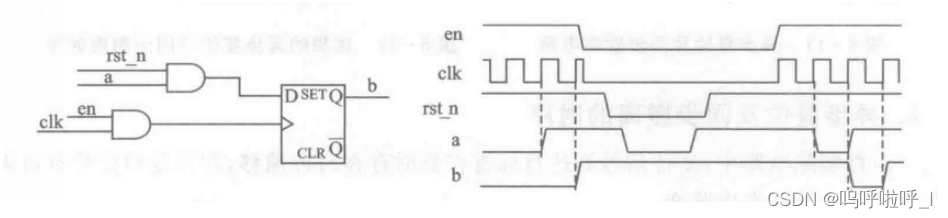

异步复位的示意图如下:

时序图

当复位信号为高电平有效时,复位信号只要有效,D触发器立刻复位,输出结果为0。

(1)异步复位实例

下面给出同步复位的Verilog示例、电路结构、综合结果:

module reset_test(input clk,input rst,input single_bit,output reg out);

always@(posedge clk or negedge rst)

beginif(rst)out<=1'b0;elseout<=single_bit;

end

endmodule

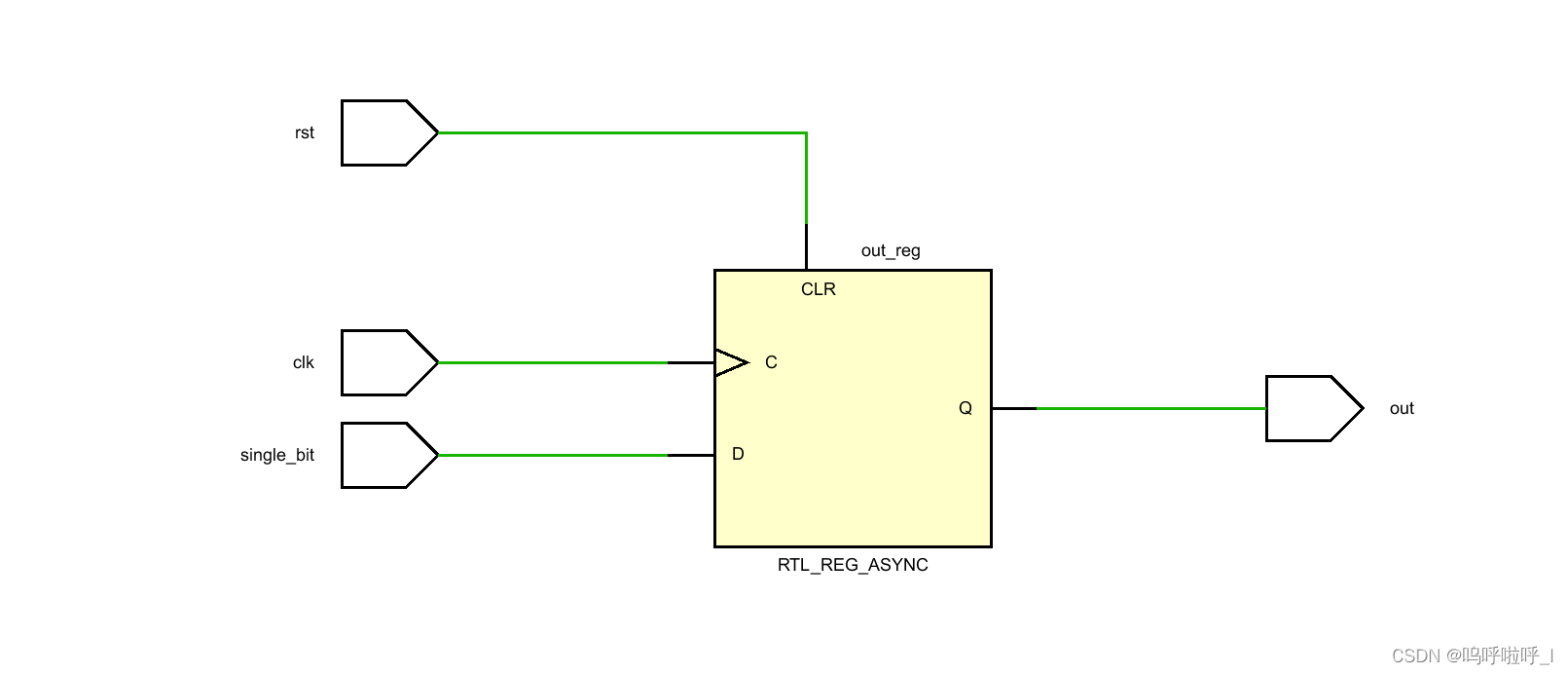

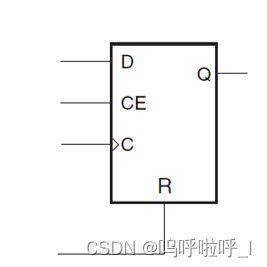

其电路结构如下,一个带同步复位的D触发器:

综合后的结果如下:

在异步复位中,对复位信号的长度没有要求。

观察同步复位和异步复位的电路结构及综合结果可以发现,Xilinx平台既有同步复位触发器也有异步复位触发器。

(2)异步复位的优劣

异步复位的优势如下:

- 对复位信号的持续时间没有要求

- 任何时候都可以复位,无需等到时候边沿到来;

异步复位的劣势如下:

- 容易受到毛刺影响,发生假复位

- 异步复位属于异步电路,无法避免亚稳态问题

- 难以进行静态时序分析

4.Xilinx平台复位信号注意事项

(1)高电平有效

xilinx 7系列触发器,其 R 端口既可用作同步置位/复位端口,也可用作异步预设/清除端口,但无论哪种方式,都是高电平有效。

上例中均采用高电平有效进行复位,下面给出利用低电平有效复位的实例:

module reset_test(input clk,input rst_n,input single_bit,output reg out);always@(posedge clk or negedge rst_n)

beginif(!rst_n)out<=1'b0;elseout<=single_bit;

end

endmodule

其电路结构如下,一个带同步复位的D触发器:

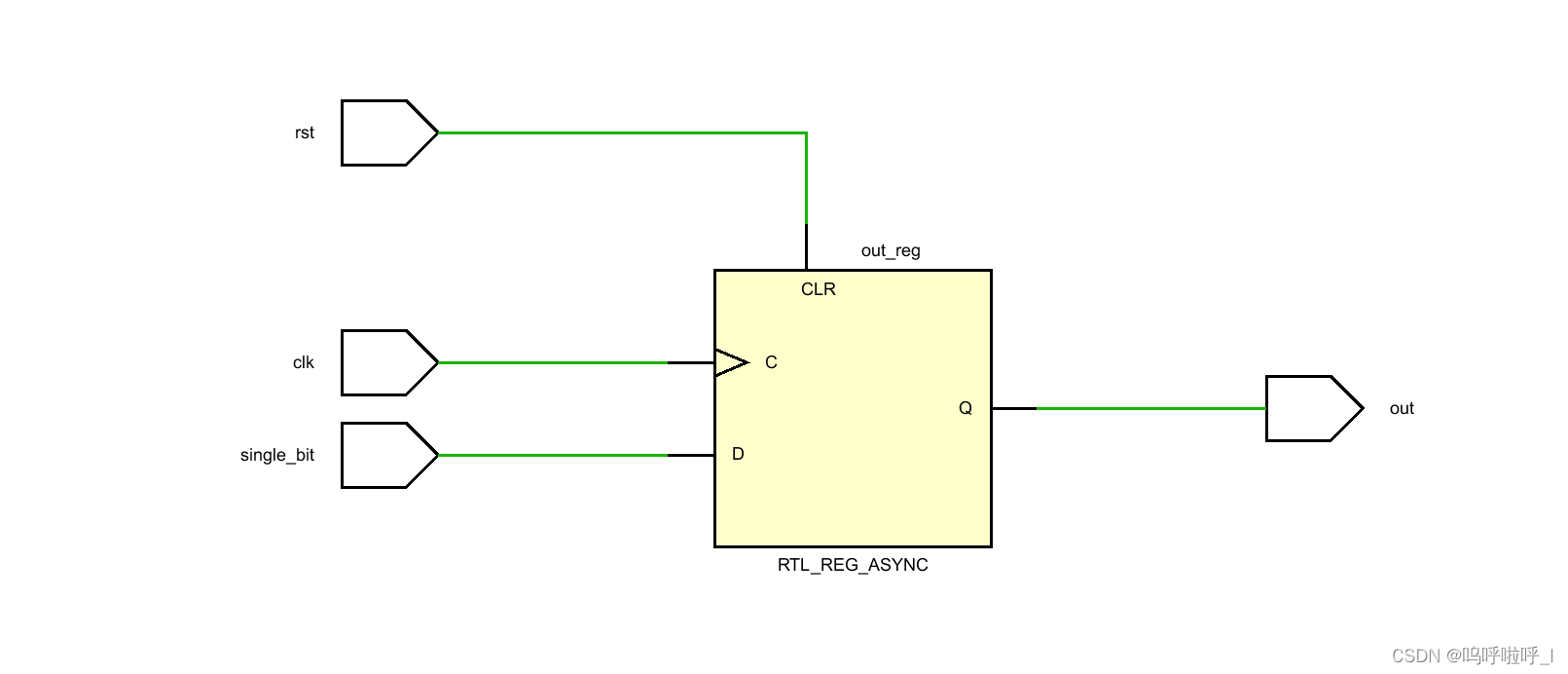

综合后的结果如下:

与采用高电平复位的综合电路相比,低电平有效复位的电路中在复位信号后紧跟了一个查找表。

如果RTL代码采用了低电平有效的复位模式,综合器将在复位信号驱动寄存器SR控制端之前的插入一个反相器(interver);综合时使用一个查找表(look up table)来实现反向器。因此低电平有效的控制信号带来的额外的逻辑可能拉长了执行时间(runtime),将导致更低的FPGA资源利用率,也将影响时序和功耗。

(2)综合注意事项

Xilinx FPGA综合规则中:有和没有异步复位的寄存器不能被包装在一个Slice,不同异步复位的寄存器不能被包装在一个Slice,这就导致在Slice中的资源无法充分利用从而造成资源浪费。

四、异步复位同步释放

1.为什么会出现异步复位同步释放

根据异步复位的时序图及原理我们可以知道,复位信号可以在任何时刻有效,也会在任何时刻撤销。如果当复位信号在时钟边沿附近撤销时,为了防止亚稳态的发生,复位信号也必须满足寄存器建立时间和保持时间的要求,这便是Recovery Time(恢复时间)和Removal Time(去除时间)。

恢复时间(Recovery Time)是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。去除时间(Removal)是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。

因此,对复位信号的处理就像处理亚稳态一样,对复位信号进行打拍操作。

2.原理

当复位信号有效时立即进行复位,但是当复位信号要释放时,通过对其进行同步化处理,这样可以防止发生亚稳态,有利于时序分析。

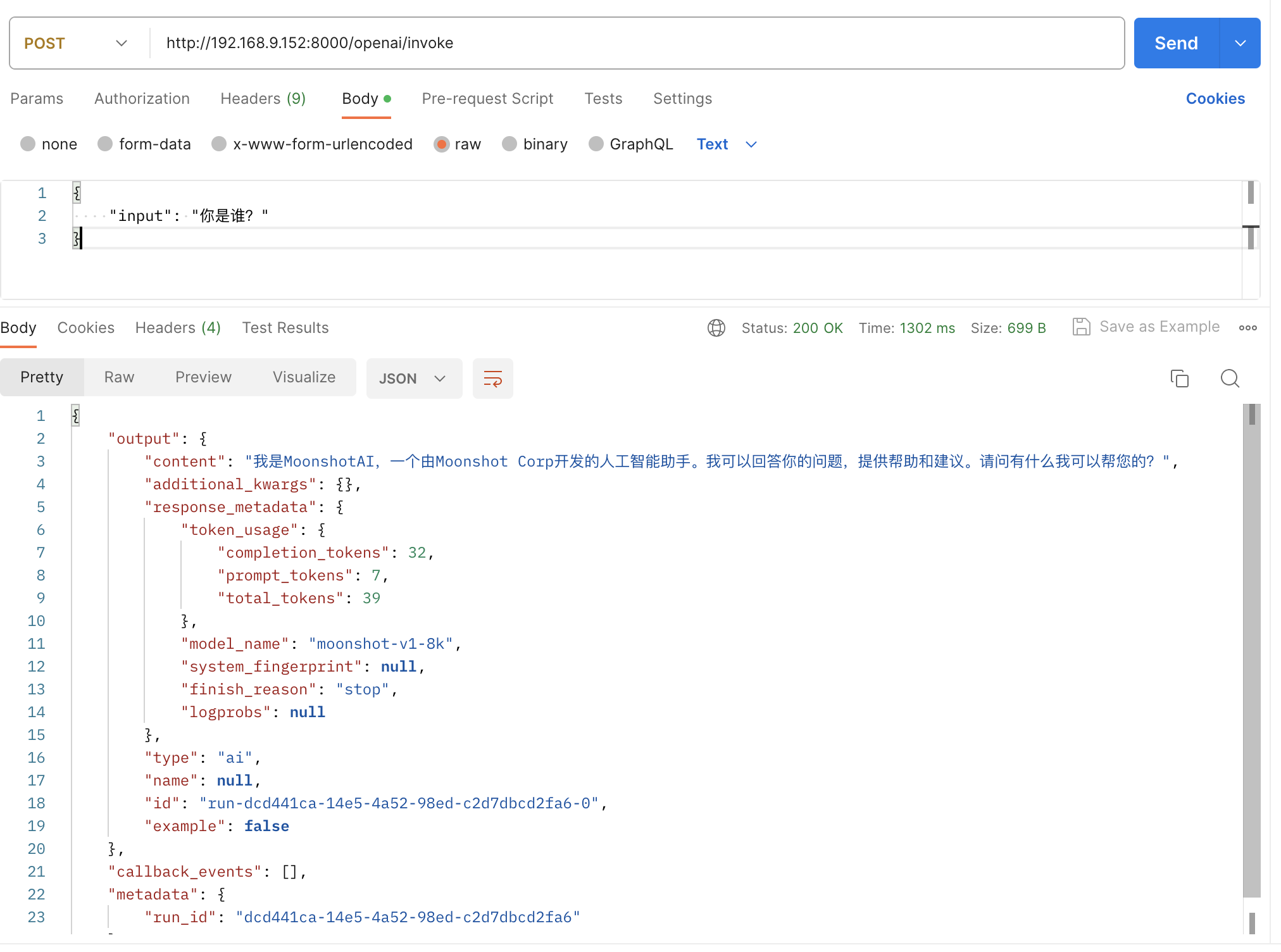

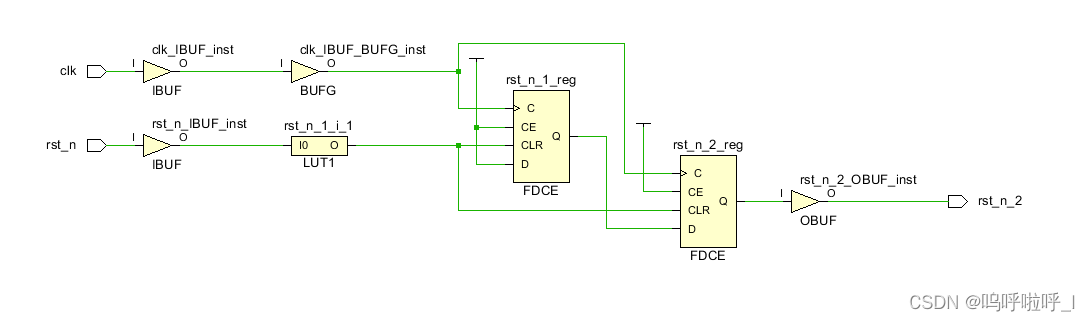

3.实例

module reset_test(input clk,input rst_n,output reg rst_n_2);reg rst_n_1;

always@(posedge clk or negedge rst_n)

beginif(!rst_n)beginrst_n_1<=1'b0;rst_n_2<=1'b0;endelsebeginrst_n_1<=1'b1;rst_n_2<=rst_n_1;end

end

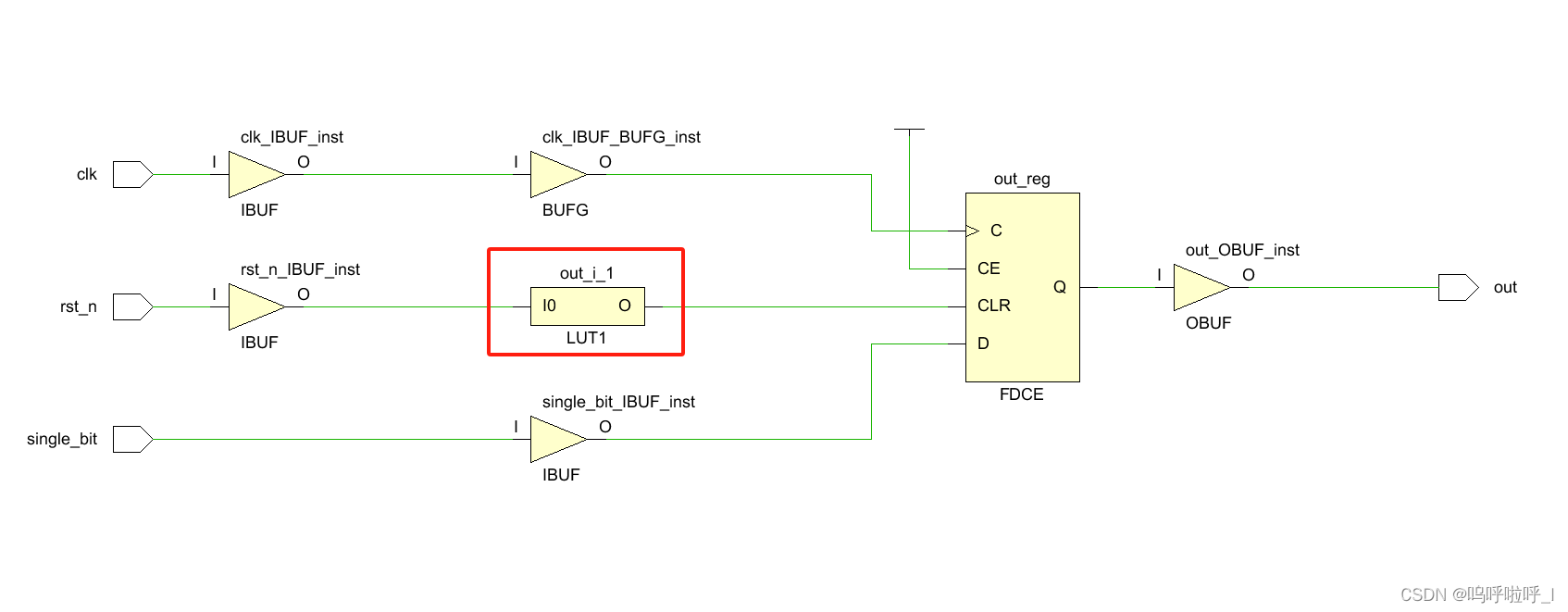

endmodule对应的Vivado综合结果如下:

4.异步复位同步释放相比异步复位的优势

异步复位同步释放的优势如下:

- 复位信号不依赖时钟,复位立即生效

- 复位释放时与时钟保持同步,有适当的恢复时间和移出时间,可以进行时序分析

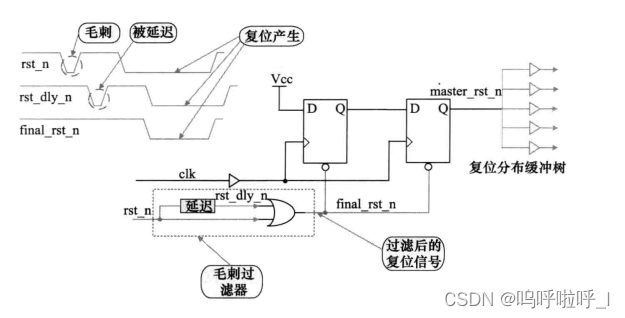

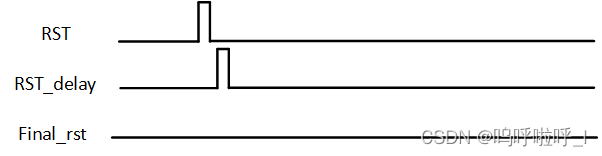

五、过滤复位信号的毛刺

由于异步复位信号对毛刺十分敏感,容易引起假复位,因此需要对毛刺进行滤除。下图给出了复位毛刺滤波器的电路:

将复位信号与经过一定延时的复位信号相与,这样对于脉冲宽度很窄的毛刺,可以做到有效滤除,其时序示意图如下:

复位输入引脚也必须是施密特触发器引脚才有助于毛刺过滤,原因是施密特触发器具有滞回特性,可以消除输入信号的噪声和干扰,从而过滤掉复位信号中的毛刺。施密特触发器是一种特殊的门电路,其输出状态仅由输入信号的当前状态决定,而与输入信号的变化过程无关。当输入信号从低电平向高电平变化时,只有当输入电压达到正向阈值电压时,输出电压才会发生跳变;而当输入信号从高电平向低电平变化时,只有当输入电压低于负向阈值电压时,输出电压才会发生跳变。这种滞回特性使得施密特触发器对输入信号的噪声和干扰具有较强的抑制能力,因此可以用于过滤复位信号中的毛刺

参考文章如下:

数字设计小思 - 谈谈复位那些事

深入理解复位

恢复和去除时间

Recovery和Removal分析