目录

1. 简介

2. 硬件电路

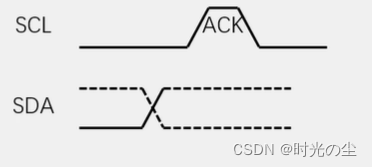

3. IIC时序基本单元

3.1 发送一个字节

3.2 接收一个字节

3.3 发送应答

3.4 接收应答

1. 简介

I2C(Inter-Integrated Circuit)总线是由NXP Semiconductors(前身为Philips Semiconductor)公司开发的一种串行通信总线。它是一种用于连接微控制器和外部设备的串行通信协议,常用于连接各种集成电路、传感器、存储器芯片等外围设备。

两根通信线:SCL(Serial Clock)、SDA(Serial Data)。SCL是时钟线,用于同步数据传输的时钟信号;SDA是数据线,用于传输实际的数据。

同步,半双工:I2C总线是同步通信的,意味着数据的传输是基于时钟信号的。它是半双工的,即在同一时间内,数据传输只能单向进行,但是可以在数据传输的过程中切换方向。

带数据应答:在I2C通信中,接收方需要给发送方一个应答信号,以确认数据是否成功接收。这种数据应答的机制有助于保证通信的可靠性。

支持总线挂载多设备(一主多从,多主多从):I2C总线支持一主多从的架构,即一个主设备(通常是微控制器或者处理器)可以同时控制多个从设备(外部器件)。此外,它也支持多主多从的架构,允许多个主设备依次控制总线上的从设备。

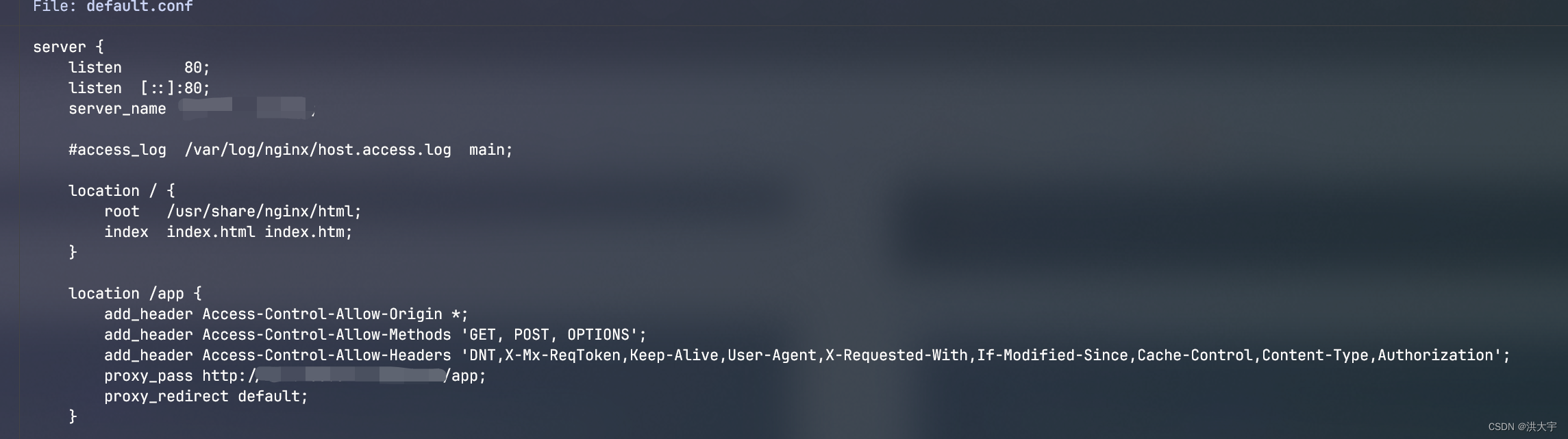

2. 硬件电路

所有IIC设备的SCL连在一起,SDA连在一起,这是I2C总线的基本连接方式。所有I2C设备的时钟线(SCL)都被连接在一起,以同步数据传输的时钟信号。同样,所有设备的数据线(SDA)也连接在一起,用于实际的数据传输。

设备的SCL和SDA均要设置成开漏输出模式。这意味着设备可以将线拉低(输出低电平),但是只能释放线,而不能将线拉高(输出高电平)。这种模式使得多个设备可以共享总线,避免冲突。

SCL和SDA各添加一个上拉电阻,电阻一般为4.7KΩ左右。为了确保在总线上没有设备发送数据时,SCL和SDA线保持高电平,通常会在每条线上连接一个上拉电阻。

主机完全掌控SCL,在空闲状态下主机可以主动发起对SDA的控制,只有在从机发送数据和从机应答的时候,主机才会转交SDA的控制权给从机。

3. IIC时序基本单元

起始条件:SCL高电平期间,SDA从高电平切换到低电平

终止条件:SCL高电平期间,SDA从低电平切换到高电平

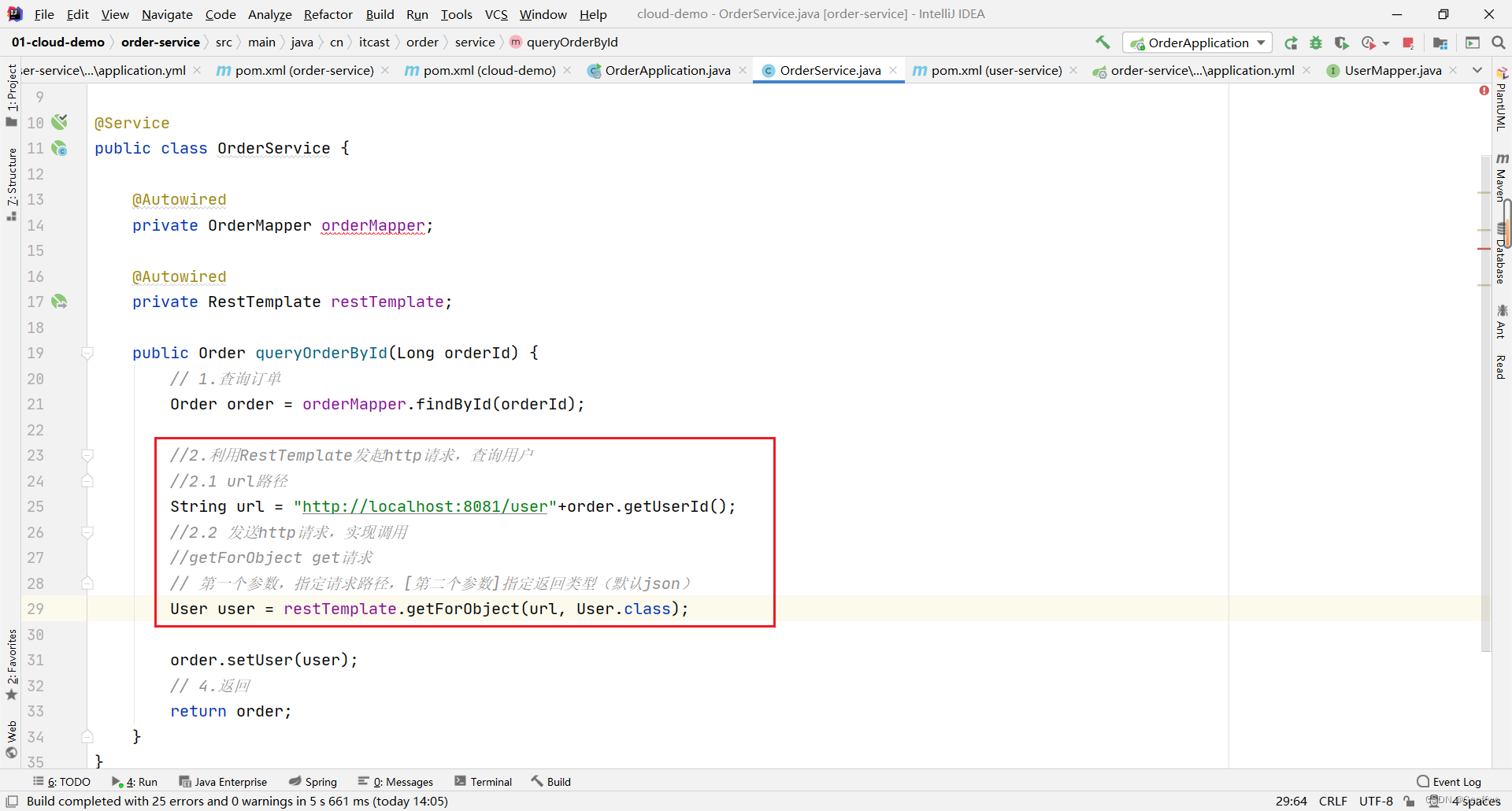

3.1 发送一个字节

发送一个字节: SCL低电平期间,主机将数据位依次放到SDA线上(高位先行) ,然后释放SCL,从机将在SCL高电平期间读取数据位,所以SCL高电平期间SDA不允许有数据变化,依次循环上述过程8次,即可发送一个字节。

主机首先在SCL低电平,主机如果想发送0,就拉低SDA到低电平,主机如果想发送1,就放手,SDA回弹到高电平,在SCL低电平期间允许改变SDA的电平,如图黄色部分:

在SCL高电平期间不允许改变SDA的电平,从机需要尽快读取SDA,一般在上升沿从机就已经读取完成了。

高位先行:具体来说,对于每个字节,数据的最高有效位(MSB,Most Significant Bit)会先被发送或接收,然后是次高位、中间位,直到最低有效位(LSB,Least Significant Bit)。这种顺序被称为"高位先行",因为数据的高位先被处理。

3.2 接收一个字节

接收一个字节:SCL低电平期间,从机将数据位依次放到SDA线上(高位先行),然后释放SCL,主机将在SCL高电平期间读取数据位,所以SCL高电平期间SDA不允许有数据变化,依次循环上述过程8次,即可接收一个字节(主机在接收之前,需要释放SDA)。

3.3 发送应答

发送应答:主机在接收完一个字节之后,在下一个时钟发送一位数据,数据0表示应答,数据1表示非应答

3.4 接收应答

接收应答:主机在发送完一个字节之后,在下一个时钟接收一位数据,判断从机是否应答,数据0表示应答,数据1表示非应答(主机在接收之前,需要释放SDA)

![[Algorithm][二分查找][在排序数组中查找元素的第一个和最后一个位置][x 的平方根]详细讲解](https://img-blog.csdnimg.cn/direct/6cac6e560ef84eb68453386d6de3368a.png)