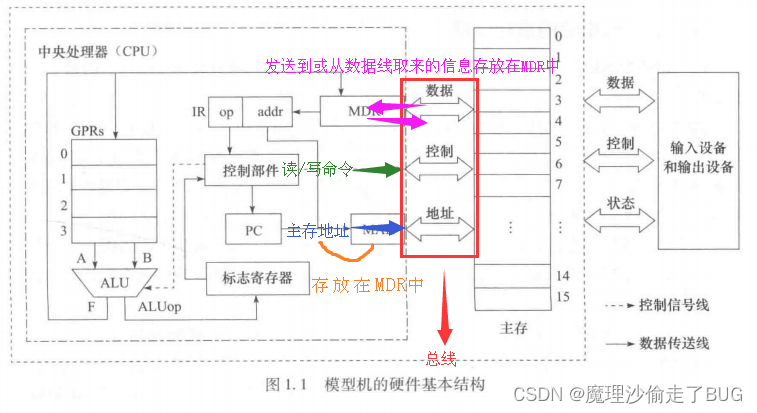

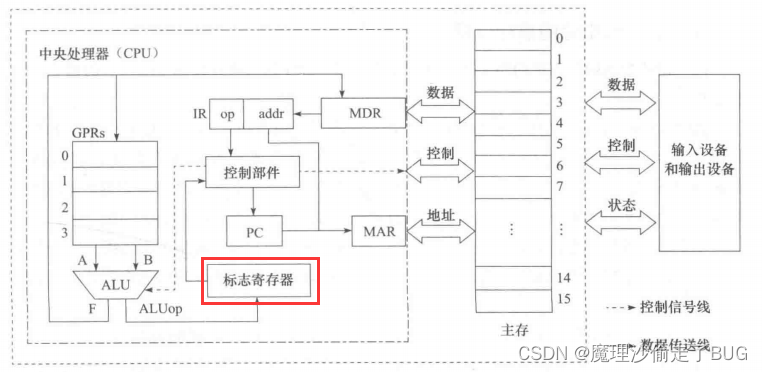

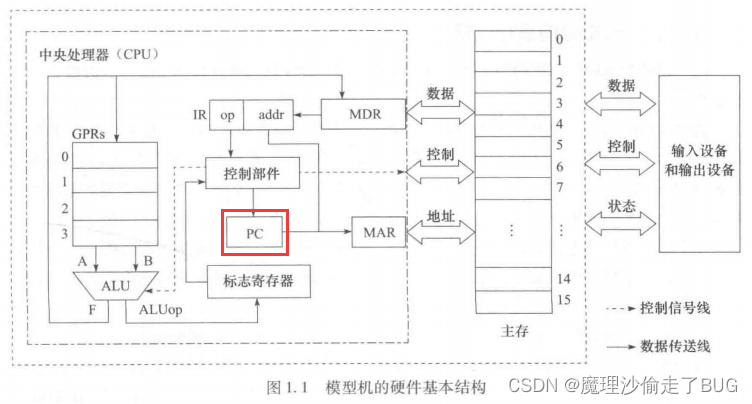

1.1.2 冯诺依曼机基本结构

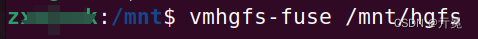

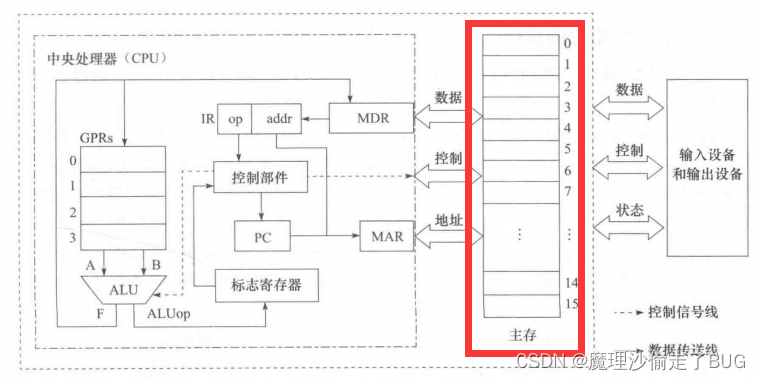

冯诺依曼机基本结构如图所示:

模型机中主要包括:

-

主存储器:用来存放指令和数据,简称主存或内存;

-

算数逻辑部件(Arithmetic Logic Unit,简称ALU):用来进行算数逻辑运算的部件,在ALU操作控制信号ALUop的控制下,ALU可以对输入端A和B进行不同的运算,得到结果F;

-

控制部件(Control Unit,简称CU):用于自动逐条读取指令并进行译码的部件,也称控制器;

-

I/O:用来和用户交互的输入设备和输出设备。

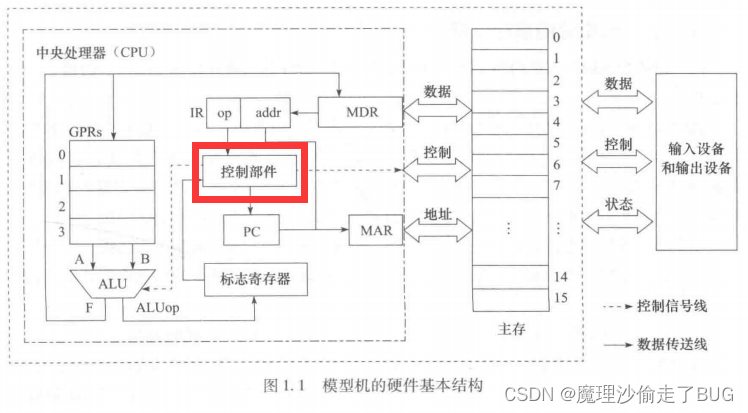

除了这些主要的部件,还有寄存器部件,为了临时存放从主存取来的数据或运算的结果,还需要若干通用寄存器(General Purpose Register),组成通用寄存器组(GPRs),ALU 两个输入端A和B的数据来自通用寄存器;

ALU运算的结果会产生标志信息,例如,结果是否为0(零标志ZF)、是否为负数(符号标志SF)鞥,这些标志信息需要记录在专门的标志寄存器中;

从主存读取来的指令需要临时保存在指令寄存器(Instruction Register,简称IR)中;

CPU为了自动按序读取主存中的指令,还需要有一个程序计数器(Program Counter,简称PC),在执行当前指令过程中,自动计算出下一条指令的地址并送到PC中保存;

通常把控制部件、运算部件和各类寄存器互联组成的电路称为中央处理器(Central Processing Unit,简称CPU),简称处理器。

CPU需要从通用寄存器中取数据到ALU运算,或把ALU运算的结果保存到通用寄存器中,因此,需要给每个通用寄存器编号;

同样,主存中每个单元也需要编号,称为主存单元地址,简称主存地址。

通用寄存器和主存都属于存储部件,通常,计算机中的存储部件从0开始编号,例如,图1.1中4个通用寄存器编号分别为0~3,16个主存单元编号分别为0~14.

CPU为了从主存取指令和存取数据,需要通过传输介质与主存相连,通常把连接不同部件进行信息传输的介质称为总线,其中,包含了用于传输地址信息、数据信息和控制信息的地址线、数据线和控制线。CPU访问主存时,需先将主存地址、读/写命令分别送到总线的地址线、控制线,然后通过数据线发送或接受数据。CPU送到地址线的主存地址应先存放到主存地址寄存器(Memory Address Register,简称MAR)中,发送到或从数据线取来的信息存放在主存数据寄存器(Memory Data Register,简称MDR)中。