树莓派点亮FPGA小灯

引言:

本次实验的目的是通过树莓派和FPGA之间的串口通信,控制FPGA开发板上的小灯。实验将展示如何使用树莓派发送特定的字符信号,通过串口传输至FPGA,并在FPGA上实现逻辑解析,以点亮指定的小灯。这不仅验证了树莓派与FPGA之间的通信能力,也展示了数字逻辑设计在实际应用中的灵活性。

希望你在本次学习过后,能够有一定的收获!!!

推荐歌曲—雨爱-杨丞琳

冲啊!!!! ٩(͡๏̯͡๏)۶ ٩(͡๏̯͡๏)۶ ٩(͡๏̯͡๏)۶

文章目录

- 树莓派点亮FPGA小灯

- 一、任务介绍

- 二、树莓派介绍

- 一、树莓派

- 二、树莓派图片

- 三、实验流程

- 1、树莓派设置

- 2、FPGA相关

- 四、实验效果

- 五、实验总结

一、任务介绍

- 了解树莓派的相关内容

- 实现树莓派与FPGA开发板之间的通信

- 使用树莓派点亮FPGA开发板上面的小灯

二、树莓派介绍

一、树莓派

a.简介:树莓派(Raspbreey Pi,RPi),慈善组织“Raspberry Pi 基金会”开发,为学生计算机编程教育而设计,基于Linux系统的单片机系统。随Windows 10 IoT的发布,有可以用运行Windows的树莓派。只有信用卡大小,却有视频、音频等功能。

c. 硬件:是一款基于ARM的微型电脑主板

内存硬盘:SD/MicroSD卡

四类接口:有1/2/4个USB接口;

一个10/100 以太网接口(A型没有网口);

视频模拟信号的电视输出接口;

和HDMI高清视频输出接口。

可连接键盘、鼠标和网线.,具备所有PC的基本功能只需接通电视机和键盘,就能执行如电子表格、文字处理、玩游戏、播放高清视频等诸多功能。Raspberry Pi B款只提供电脑板,无内存、电源、键盘、机箱或连线。

d.语言:树莓派基金会提供了基于ARM的Debian和Arch Linux的发行版供大众下载。还计划提供支持Python作为主要编程语言,支持Java、BBC BASIC (通过 RISC OS 映像或者Linux的"Brandy Basic"克隆)、C 和Perl等编程语言。

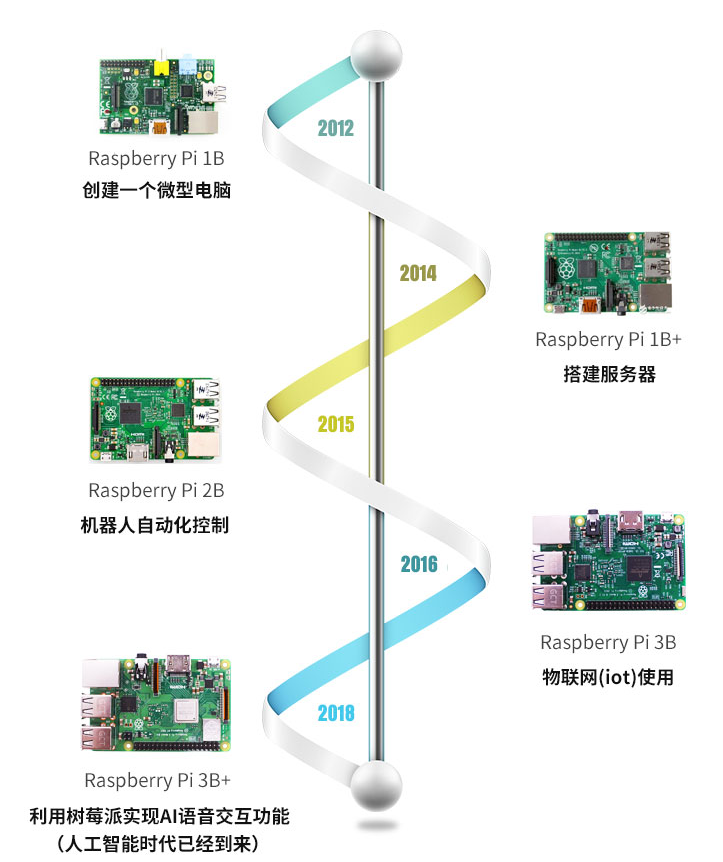

e. 发展以及应用(亚博官网摘)

二、树莓派图片

a.板子图片(亚博官网摘)

b.树莓派3b与树莓派3b+参数对比:

b.树莓派3b+引脚图:

三、实验流程

1、树莓派设置

- 首先确认波特率设置正确,是否为115200。(当然,其他波特率也可以的,不过代码得改一下

- 向microSD卡中烧录树莓派官方的镜像后,先不要急着把它插入树莓派中。

- 在电脑上打开microSD卡,按如下方式修改config.txt和cmdline.txt这两个文件,在config.txt文件中附加

dtoverlay=pi3-miniuart-bt

在电脑里直接打开比在树莓派里打开要好操作,不用获取权限

然后把cmdline.txt中的内容换成

dwc_otg.lpm_enable=0 console=tty1 console=serial0,115200 root=/dev/mmcblk0p2 rootfstype=ext4 elevator=deadline fsck.repair=yes rootwait

修改完成之后,我们打开树莓派

进入到树莓派的命令行当中进行如下操作

在命令行中输入如下命令

sudo chmod 777 /dev/ttyAMA0

这里要先获取权限,否则后面代码会报错

接着进入python3中,输入如下代码,这里一定一定要注意,不要安装serial库!!!因为这个是安装好的,再安装会提示serial中无Serial!

树莓派发送数据代码

import serial

import time

ser = serial.Serial('/dev/ttyAMA0',115200)while ser.isOpen() :ser.write(b"A") # 点亮第一个小灯time.sleep(1)ser.write(b"B") # 点亮第二个小灯time.sleep(1)

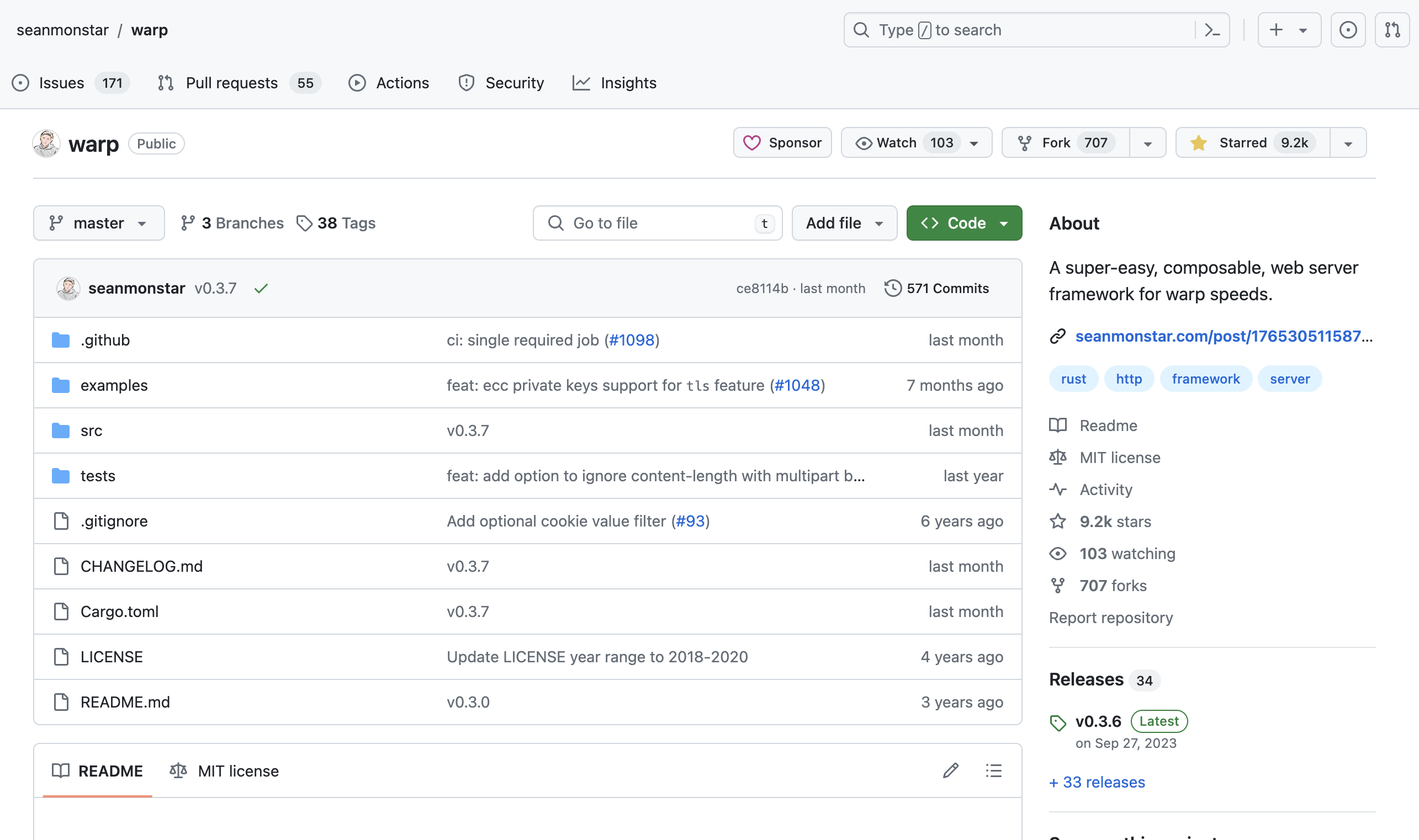

2、FPGA相关

led.v

module led (input clk,input rst_n,input tx,output reg[7:0] led

);wire [7:0] dout;wire dout_vld;uart_rx uart_rx_inst (.clk (clk),.rst_n (rst_n),.din (tx),.dout(dout),.dout_vld (dout_vld));always @(posedge clk or negedge rst_n) beginif(!rst_n) beginled <= 8'b0;endelse if (dout_vld) beginif (dout == 8'h41) beginled <= 8'b0000_0001;endelse if (dout == 8'h42) beginled <= 8'b0000_0010;endelse if (dout == 8'h43) beginled <= 8'b0000_0100;endelse if (dout == 8'h44) beginled <= 8'b0000_1000;endelse if (dout == 8'h45) beginled <= 8'b0001_0000;endelse if (dout == 8'h46) beginled <= 8'b0010_0000;endelse if (dout == 8'h47) beginled <= 8'b0100_0000;endelse beginled <= led;endendend endmodule

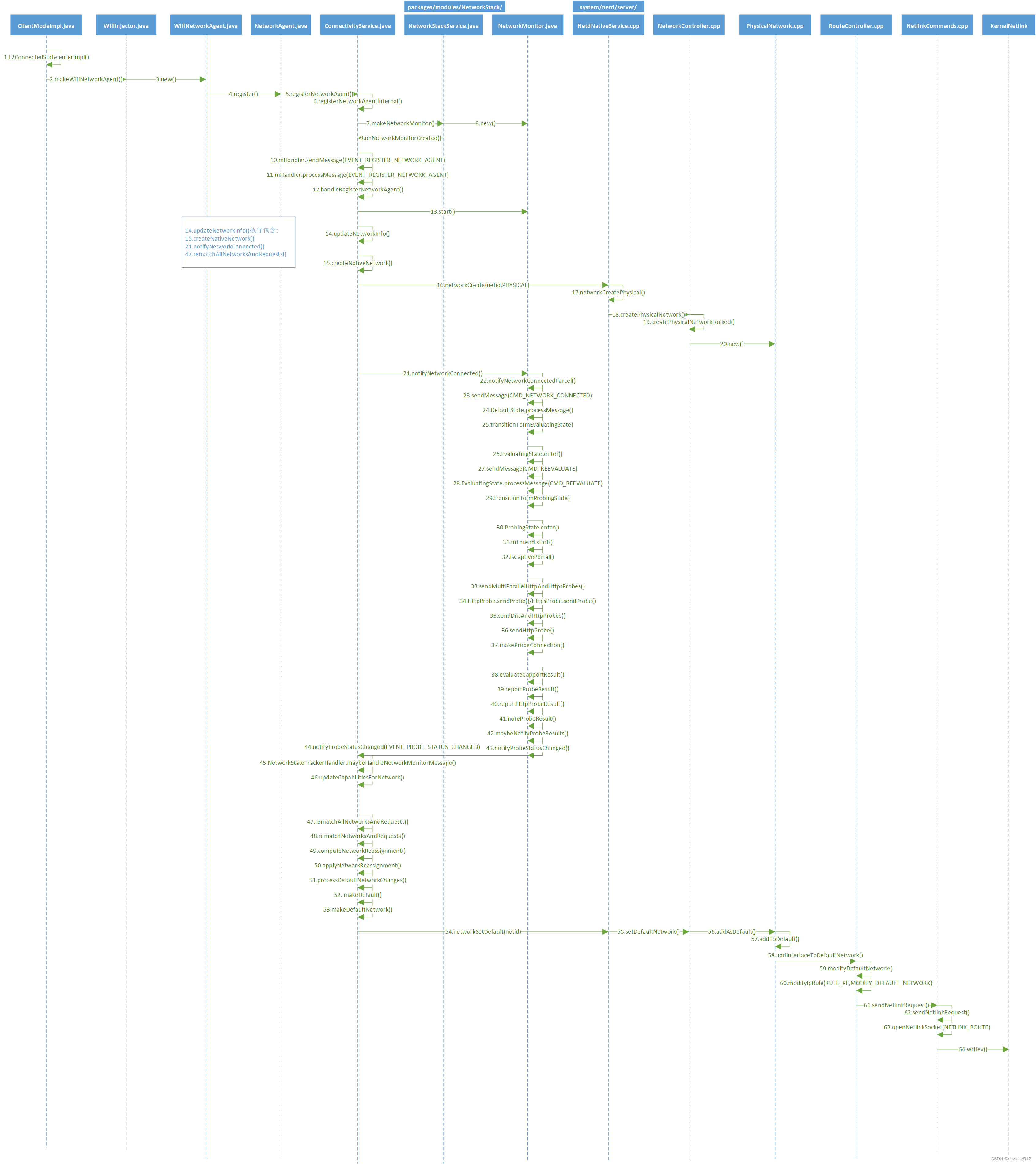

uart_rx.v

module uart_rx (input clk,input rst_n,input din, // pc 发送给 FPGA 的数据output reg[7:0] dout, // 发送给 tx 让他串行的传输出去output reg dout_vld // 当这一次 8bit 接收完成 再传递给tx

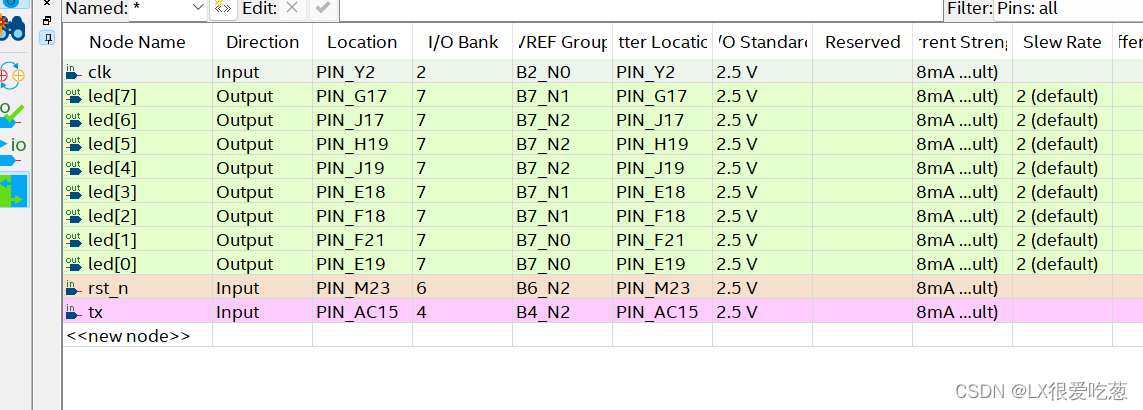

);parameter BAUD = 5207; // 使用波特率 115200 发送1 bit 需要的时钟周期reg din_r0; // 同步到时钟上升沿 reg din_r1; // 打拍 延时一个时钟周期 wire nedge; // 下降沿reg flag; // 计数器计数标志 下降沿到来之后开始计数 传输数据完成停止计数reg [8:0] data; // 寄存 数据always @(posedge clk or negedge rst_n) beginif (!rst_n) begin din_r0<= 1; din_r1<=1; endelse begin din_r0<= din; din_r1<= din_r0; endendassign nedge = din_r1 && !din_r0; // 下降沿// 计数一个bit发送需要的时钟周期reg [20:0] cnt_bsp; wire add_cnt_bsp; wire end_cnt_bsp; always @(posedge clk or negedge rst_n) beginif (!rst_n) cnt_bsp <= 0;else if (add_cnt_bsp)if (end_cnt_bsp) cnt_bsp <= 0;else cnt_bsp <= cnt_bsp + 1; else cnt_bsp <= cnt_bsp;endassign add_cnt_bsp = flag;assign end_cnt_bsp = add_cnt_bsp && (cnt_bsp == BAUD - 1);// 计数当前到了哪一 bitreg [3:0] cnt_bit; wire add_cnt_bit;wire end_cnt_bit;always @(posedge clk or negedge rst_n)beginif (!rst_n) cnt_bit <= 0;else if (add_cnt_bit)if (end_cnt_bit) cnt_bit <= 0;else cnt_bit <= cnt_bit + 1;else cnt_bit <= cnt_bit;endassign add_cnt_bit = end_cnt_bsp;assign end_cnt_bit = add_cnt_bit && (cnt_bit == 8); // 起始位 1bit 数据位 8bit always @(posedge clk or negedge rst_n) beginif (!rst_n) flag <= 0;else if(nedge) flag <= 1;else if(end_cnt_bit) flag <= 0;else flag <= flag;endalways @(posedge clk or negedge rst_n) beginif(!rst_n) data <=0;else if(cnt_bsp == BAUD>>1 && flag) data[cnt_bit] <= din; // 串并转换 LSBelse data <= data; endalways @(posedge clk or negedge rst_n) beginif(!rst_n) begindout <= 8'b0;dout_vld <= 0;endelse if(end_cnt_bit)begindout <= data[8:1]; // 第0位起始位 被舍去 dout_vld <= 1;endelse begindout <= dout;dout_vld <= 0;endendendmoduleFPGA引脚图

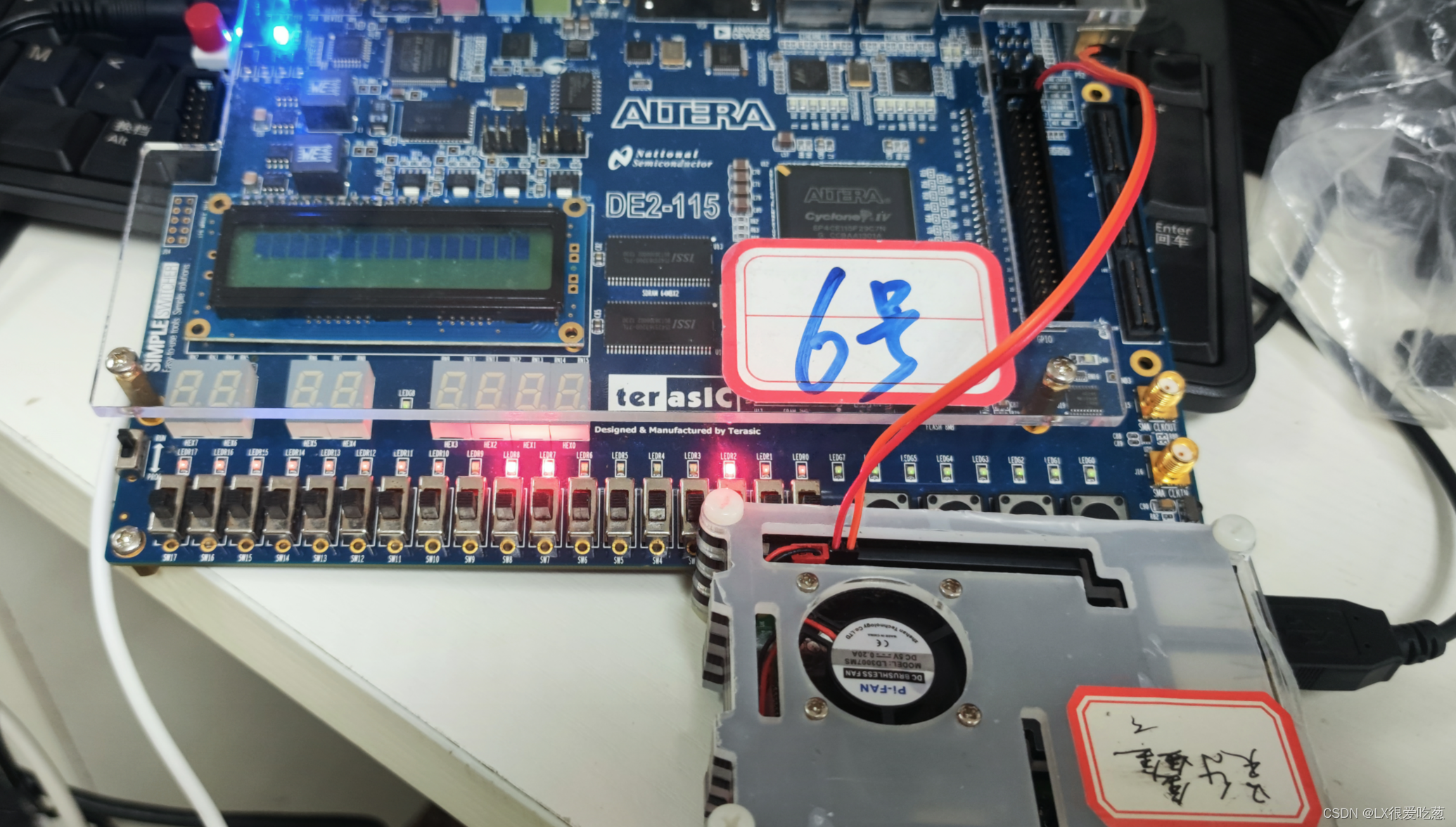

四、实验效果

五、实验总结

实验成果

本次实验成功实现了通过树莓派与FPGA之间的串口通信控制FPGA开发板上的小灯。实验中,树莓派作为上位机,通过发送特定的字符信号,点亮了FPGA板上的LED灯。这验证了树莓派与FPGA之间的通信能力,并且展示了数字逻辑设计在实际应用中的实用性和灵活性。

技术要点

- 串口通信:实验中使用了树莓派的串口功能来与FPGA进行数据交换,这是实现控制的关键技术点。

- 信号解析:FPGA端的逻辑设计能够正确解析树莓派发送的信号,这是实现特定功能的基础。

- 硬件连接:确保树莓派与FPGA之间的物理连接正确无误,包括串口线和电源连接。

遇到的问题及解决方案

- 串口通信不稳定:在实验过程中,遇到了串口通信不稳定的问题,通过调整波特率和检查串口线路解决了这一问题。

- FPGA逻辑设计错误:在FPGA逻辑设计中出现了解析信号错误的问题,通过反复检查和调试逻辑电路得到了解决。

实验心得

通过本次实验,我们不仅学习了树莓派和FPGA的基本知识,还掌握了它们之间的通信方法。实验过程中遇到的问题和挑战提高了我们解决实际问题的能力。此外,实验也加深了我们对数字逻辑设计和微控制器编程的理解。

最后感谢大佬友情链接:

- 树莓派3B+串口通信(超详细简单版)_树莓派3b串口通信-CSDN博客

- 树莓派3B+ 引脚图说明_树莓派3b+引脚图-CSDN博客

- 树莓派介绍&树莓派3代B+型开发板_树莓派开发板-CSDN博客

![[240512] x-cmd 发布 v0.3.6: (se,wkp,ddgo...)x( kimi,gemini,gpt...)](https://img-blog.csdnimg.cn/direct/f09b4b037c3d4fc69ce82f7278a79382.gif#pic_center)