基本概念

DDS(Direct Digital Synthesizer),即数字合成器,是一种把一系列数字信号通过D/A转换器转化成模拟信号的数字合成技术

DDS的实现有两种方式:查表法和计算法,下面将主要介绍DDS查表法的FPGA实现

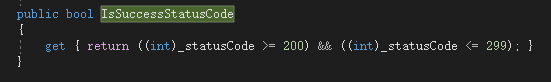

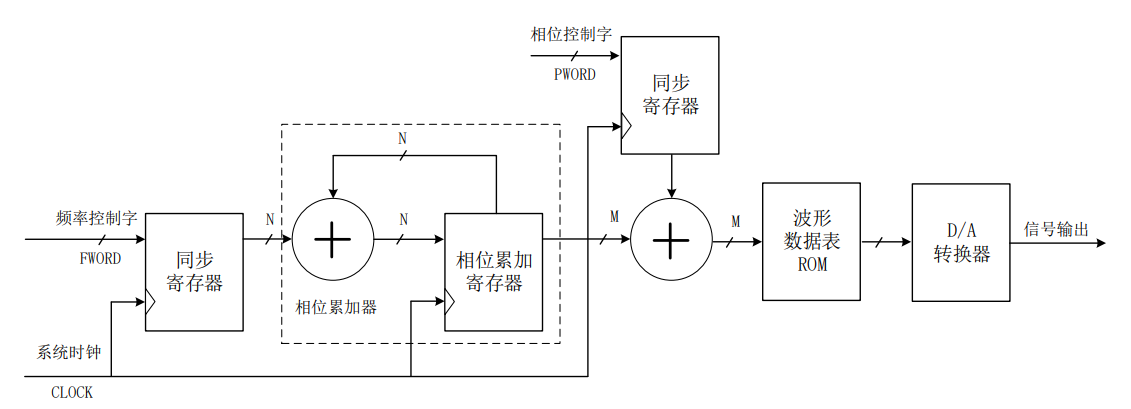

查表法:预先在ROM中存放不同相位对应的幅度序列,通过相位累加器的输出对其进行寻址,经过D/A转换与低通滤波器即可得到所需要的模拟信号

输入:频率控制字、相位控制字、系统时钟、复位信号

输出:幅度数据

关系:如果一个波形能用M个点完全采样,则:

Tout = M*Tclk

Fout = Fclk/M

原理分析

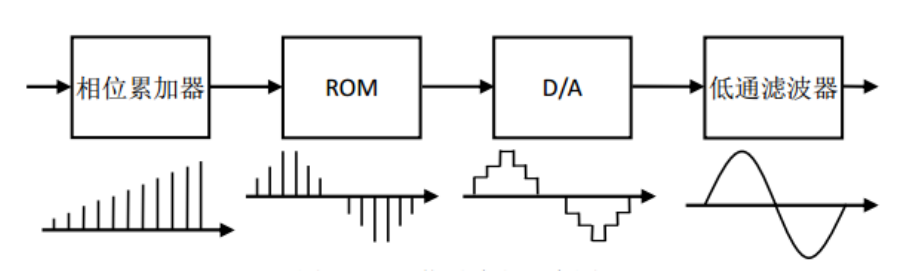

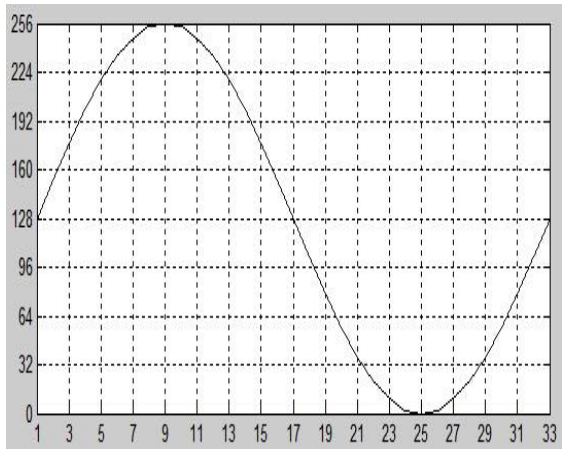

当FPGA控制DAC输出一个周期的正弦信号时,从图中可看到共32个采样点(最后一个点和第一个重合),若每1ms输出一个数值且每个点都输出,则输出一个完整的周期需要32ms,因此该信号的频率为1000/32(f=1/T)

现在若需要这样一组数据输出一个频率为2x(1000/32)的信号,即输出一个完整的周期为16ms,此时只能输出16个点来表示一个完整的周期,我们可以每隔一个点输出一个数据来完成,效果图如上所示,这样输出信号的时间缩短了一半,即频率增加了一倍

若现在需要输出一个频率为(1/2)x(1000/32)的信号,即输出一个完整的周期为64ms,此时我们可以每2ms输出一个值,即第1ms与第2ms都输出第一个点,第3ms与第4ms都输出第二个点,以此推例,即可实现周期加倍,频率减半的效果

通过上述分析,其中的计算过程如下:

Fclk=1000Hz(周期为1ms)

1.取点间隔为1

Fout=1000/32=1000/(2N) N=5

2.取点间隔为2,即频率翻倍

Fout=2000/32=1000/(2N/2) N=5

3.取点间隔为0.5,即频率减半

Fout=(1000/2)/32=1000/(2N/0.5) N=5

频率控制字Fword,也常写作B(步进)

故输出频率Fout=Fclk/M=BxFclk/2N

相位累加器位数N,相当于将一个正弦信号在相位上的精度定义为N位,因此其分辨率为1/2N

式中M是对一个波形取的所有的点数,受到ROM容量的影响

相位控制字:只需要在每个取样点的序号上加一个偏移量,即可实现对相位的控制,如上述将一个正弦的周期32等分,若我们在第1ms时从第9个点开始输出,则就将相位左移了90度,这就是相位控制的原理

后续这里工程代码讲的实在太难接受了,抱歉

![洛谷P3128 [USACO15DEC] Max Flow P 树上差分](https://img2024.cnblogs.com/blog/3503483/202409/3503483-20240907100651943-766084038.png)