目录

1.建立时间与保持时间

2.从寄存器的内部结构理解建立时间与保持时间

2.1寄存器的结构

2.2主从锁存器构成的寄存器

2.3传输门构成的寄存器

3.查看寄存器的建立时间和保持时间

文章内容为博主学习记录,如有错误,欢迎在评论区指正。

1.建立时间与保持时间

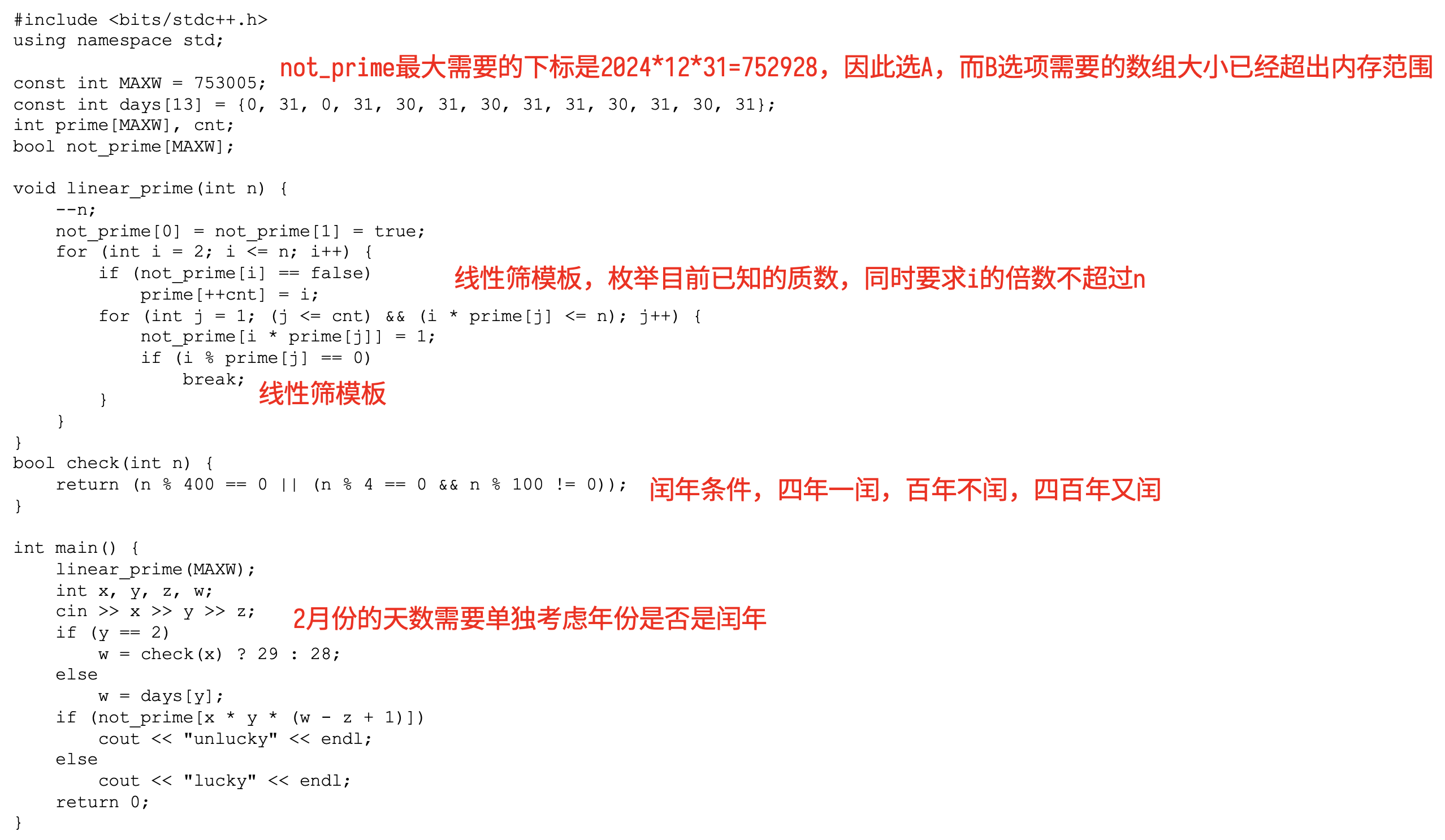

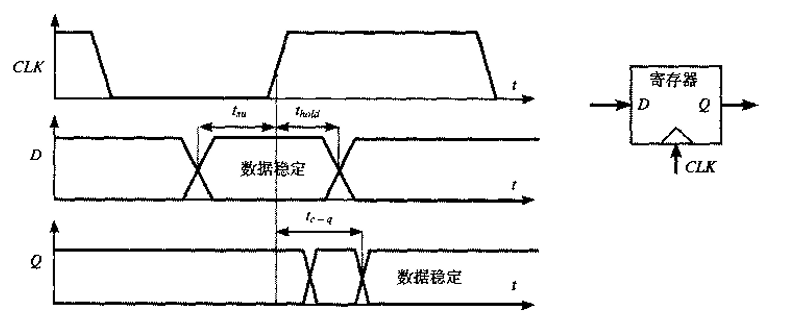

寄存器的建立时间和保持时间是时序逻辑中的重要概念。首先,我们来复习一下这两个基本概念。如图1。

- 建立时间(tset-up):在时钟上升沿之前,需要数据保持稳定的时间。

- 建立时间(thold):保持时间是在时钟上升沿之后,需要数据保持稳定的时间。

图1 寄存器的建立时间和保持时间[1]

如果不满足这两个时序约束,即数据在该稳定的时候没有稳定,寄存器就会出现不定态。

为了满足寄存器的建立时间和保存时间,电路的频率会受到限制。现代高性能系统的特点是逻辑深度很低,因此寄存器的传播延时和建立时间在时钟周期中占很大一部分。例如,DEC Alapha EV6微处理器的最大逻辑深度是12个门,它的寄存器时间开销大约占据了时钟周期的15%。[1]

那么,为什么会有这两个约束,建立时间和保持时间又是如何计算出来的呢?这就需要我们进一步观察寄存器的内部电路结构。

2.从寄存器的内部结构理解建立时间与保持时间

2.1寄存器的结构

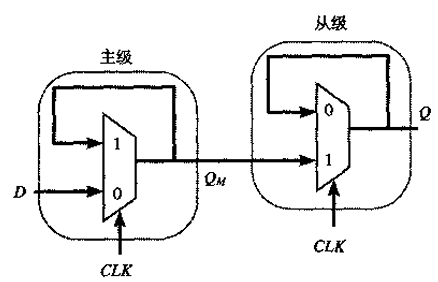

构成一个边沿触发寄存器的最普通方法是采用主从结构,如图2所示。寄存器用一个负锁存器(低电平透明,高电平维持)作为主级,串联一个作为从级的正锁存器(高电平透明,低电平维持)构成。它们在不同电平下的行为如图3所示。

图2 主从结构示意图[1]

图3 主从锁存器行为

2.2主从锁存器构成的寄存器

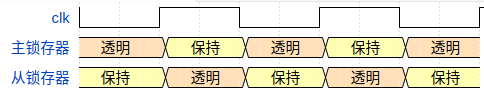

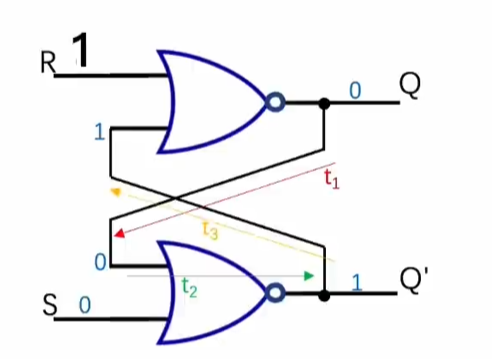

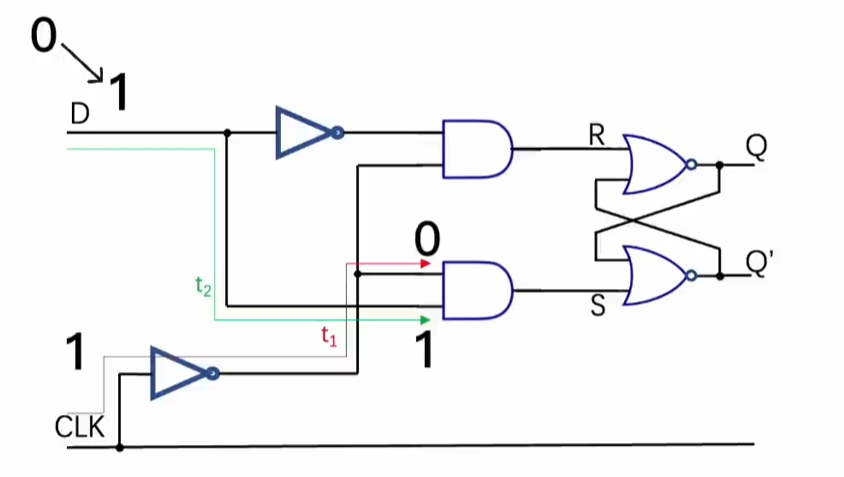

首先我们以两个串联的D锁存器构成的寄存器为例,示意图见图4。D锁存器由具有正反馈结构的或非门SR锁存器构成,由时钟信号进行门控。

图4 D锁存器构成的寄存器[2]

我们观察其中的主锁存器。

D信号在经过反相器、与门和或非门的时候都需要一定的延迟。因此,从D信号的变化,传播到Qm并在Qm保持稳定是需要时间的。如果在Qm的信号稳定之前,时钟信号由低变高,主锁存器进入保持状态,那么Qm将进入不定态。Qm保持稳定需要经过t1+t2+t3的时间,如图5所示。

图5 Qm保持稳定需要的时间[2]

同样,观察主锁存器分析保持时间。

时钟信号需要经过一个反相器到达与门。因此,当时钟信号由0变1时,也即主锁存器从透明状态变为保持状态时,与门不能被立刻关闭。如果这个时候D信号发生变化,那么该变化将会被错误地向后传播。数据需要在时钟上升沿后保持t1-t2的时长,如图6所示。

图6 时钟上升沿后的数据保持时间[2]

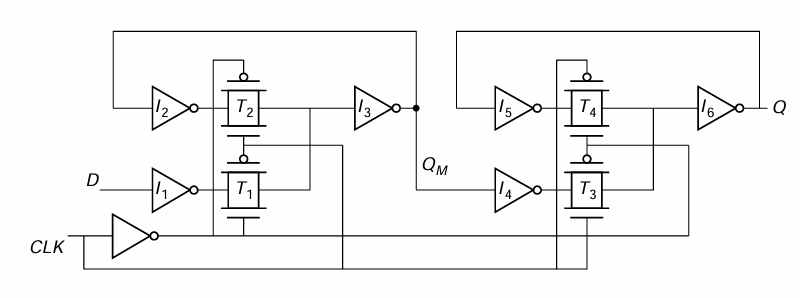

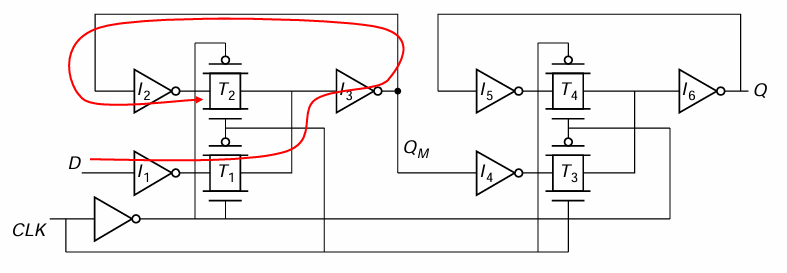

2.3传输门构成的寄存器

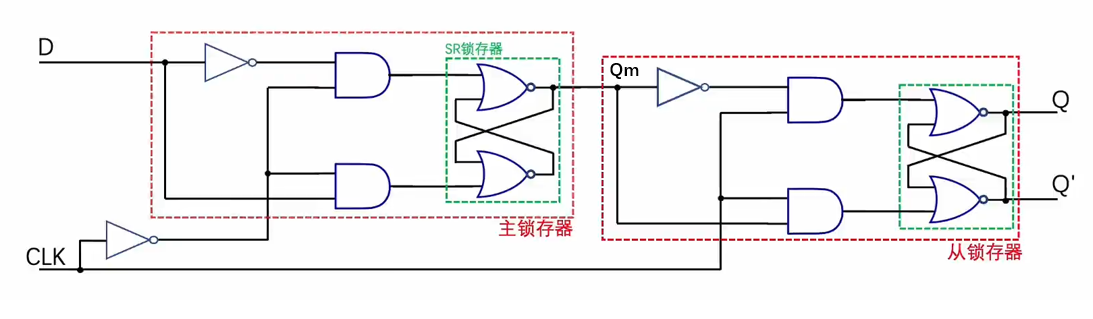

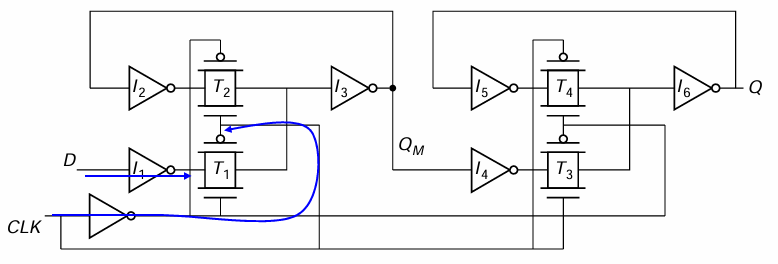

接下来我们再看一个例子。图 7是一个多路开关采用传输门来实现的寄存器。当时钟处于低电平时(CLK=0),T1导通T2关断,输入D被采样到节点Qm上。在此期间,T3关断T4导通。交叉耦合的反相器(I5,I6)保持从锁存器的状态。当时钟为高电平,主级停止采样输入并进入保持状态。T1关断T2导通,交叉耦合的反相器(I2,I3)和保持Qm状态。同时,T3导通T4关断,Qm被复制到输出Q上。[1]

图7 传输门构成的寄存器[3]

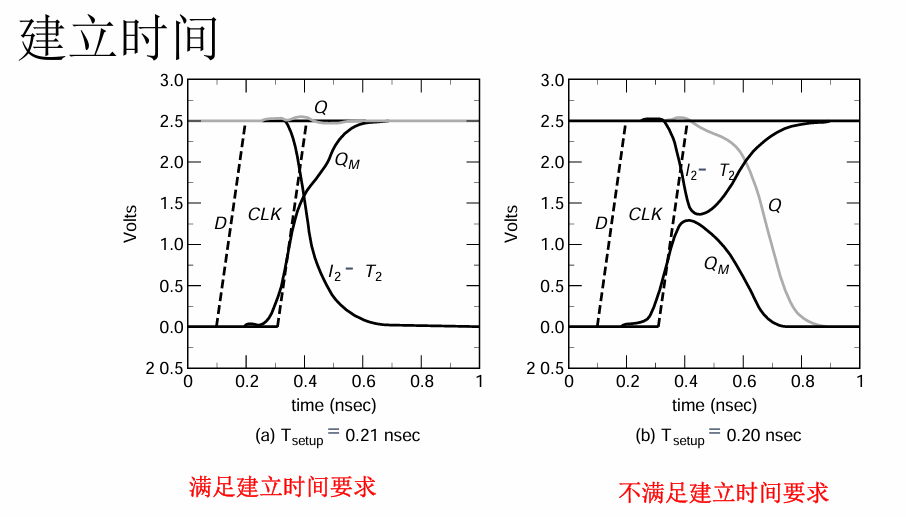

同样,我们观察主级。如图8所示,CLK上升(T2导通)之前D端数据必须传递到T2的两端,否则会引起竞争。

图8 建立时间[3]

如图9使用了SPICE 进行仿真,假设输入与时钟边沿分别相差210ps和200ps。对于210ps的情况,输入D 的采样值是正确的(在这一情况下,输出Q维持在VDD的值 )。对于偏差200ps的情况,传送到输出的值是错误的,因为输出Q变化到了0。

节点Qm开始上升时,I2的输出(传输门T2的输入)开始下降。然而时钟在传输门T2两端的节点稳定到同一个值之前就已升高,因此造成不正确的值写入主锁存器。

图9 对不满足建立时间情况的仿真[3]

接下来是保持时间。D的数据必须维持到CLK把T1完全关闭后,否则会写入错误的值,即最少维持CLK输入到T1的传播时间。

图10 保持时间[3]

3.查看寄存器的建立时间和保持时间

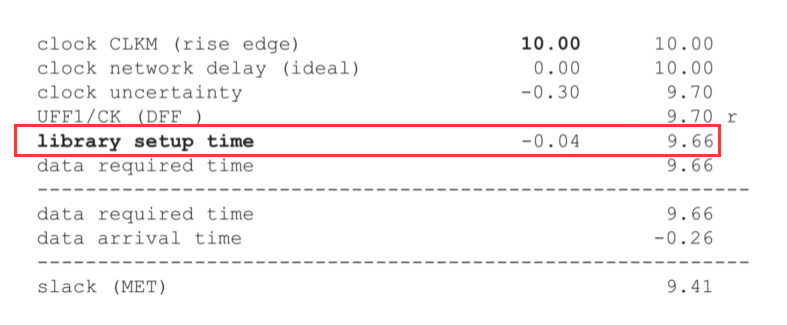

在PT进行时序分析时,我们能看到一个寄存器的建立时间和保持时间。

图11 时序分析报告中的建立时间[6]

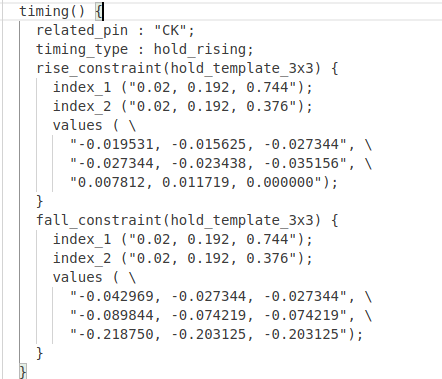

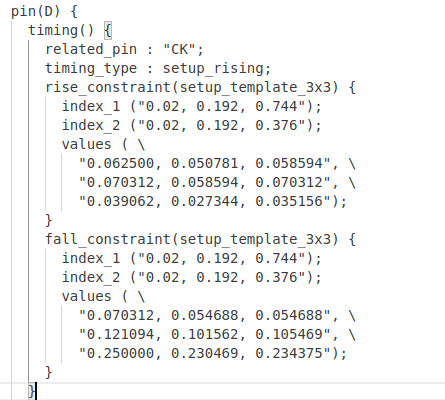

这些数值来自寄存单元综合库模型。比如TSMC_013工艺库中的DFFHQX1单元,可以查看其lib文件得到该模型的D端的建立时间约束和保持时间约束。

rise-constraint:给出D端由低电平变到高电平时的setup约束,跟D端输入转换时间和时钟的转换时间有关。

fall-constraint则给出D端由高电平变到低电平时的setup约束,跟输入转换时间和时钟的转换时间有关。[4]

图12 建立时间约束

保持时间约束同理。

rise-constraint:给出D端由低电平变到高电平时的hold约束,跟输入转换时间和时钟的转换时间有关。

fall-constraint:给出D端由高电平变到低电平时的hold约束,跟输入转换时间和时钟的转换时间有关。[4]

图13 保持时间约束

温度和电压对它们的影响:

1)温度越高,时延越高,要求D触发器的建立时间更加严格(建立时间越小越不会违例),如果很大就会违例。要求D触发器的保持时间越宽松(D触发器保持时间大一点也没事,因为时延长了)因此温度高,可能会造成建立时间不满足,而有利于保持时间。

2)电压越高,时延越小。越有利于建立时间,越不利于保持时间。所以电压过高会带来保持时间的违例。[5]

参考资料:

[1] 数字集成电路——电路系统与设计 [美]Jan M.Rabaey 周润德译

[2] 从门级理解D触发器的建立时间和保持时间 https://www.bilibili.com/video/BV13s4y1y7un/?spm_id_from=333.1007.top_right_bar_window_history.content.click&vd_source=62e6f94dd6da286dc562f0cd6ae35102

[3] 学堂在线:数字超大规模集成电路设计(2024春) 李翔宇 https://www.xuetangx.com/course/THU08071001503/19317140?channel=i.area.learn_title

[4] 标准单元工艺库(TSMC 90nm)文件详解https://blog.csdn.net/qq_41019681/article/details/118465237

[5] 建立时间和保持时间的理解以及电压温度对他们的影响https://blog.csdn.net/qq_42250376/article/details/126454974

[6] 建立时间与保持时间检查 讲芯片的邸老师 8-建立时间与保持时间检查_哔哩哔哩_bilibili