PS端Flash固化

Vivado版本:Vivado2020.2

芯片型号:RFSoC XCZU47DR

前提条件:Vitis工程编译完成,拨码开关拨到PS JTAG模式

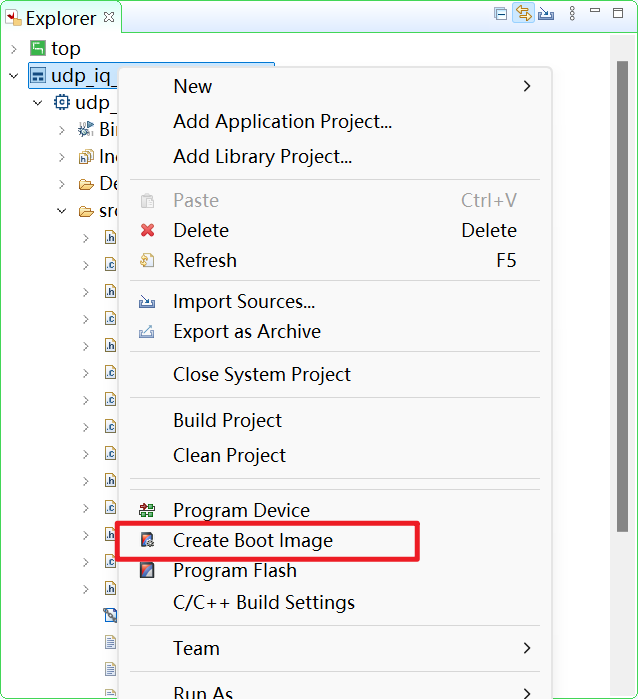

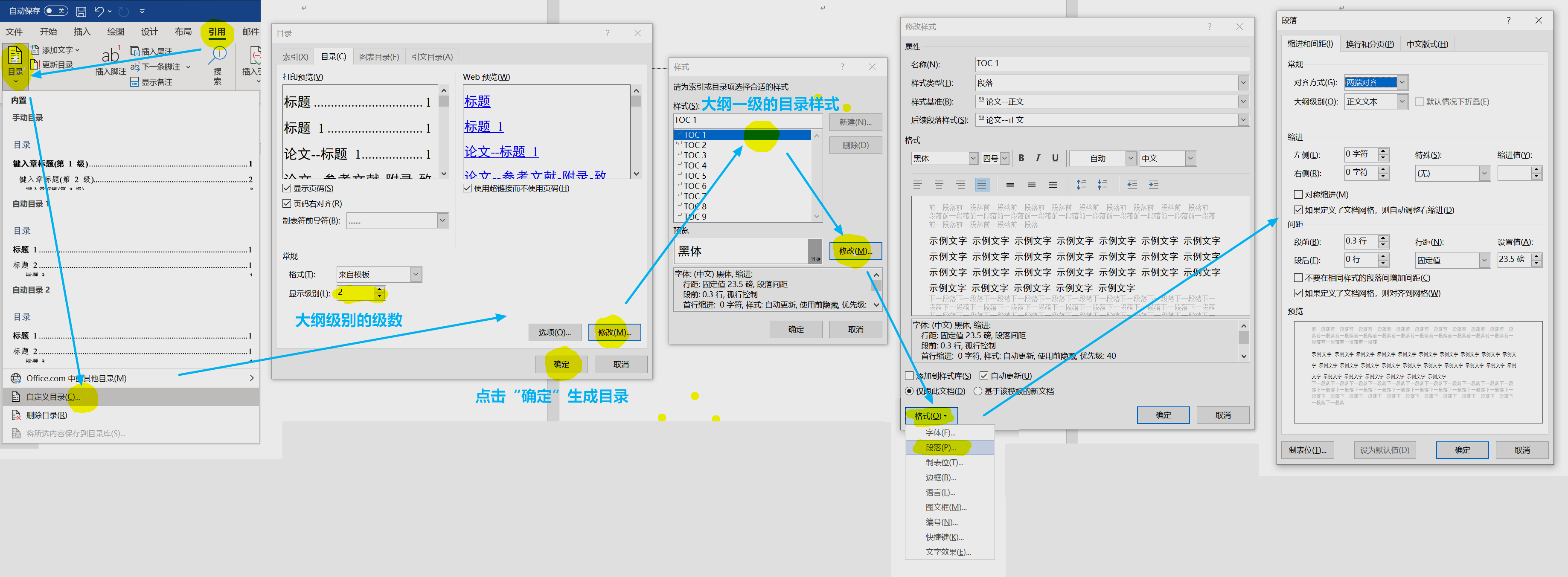

创建引导镜像

首先右键应用工程系统,点击Create Boot Image。

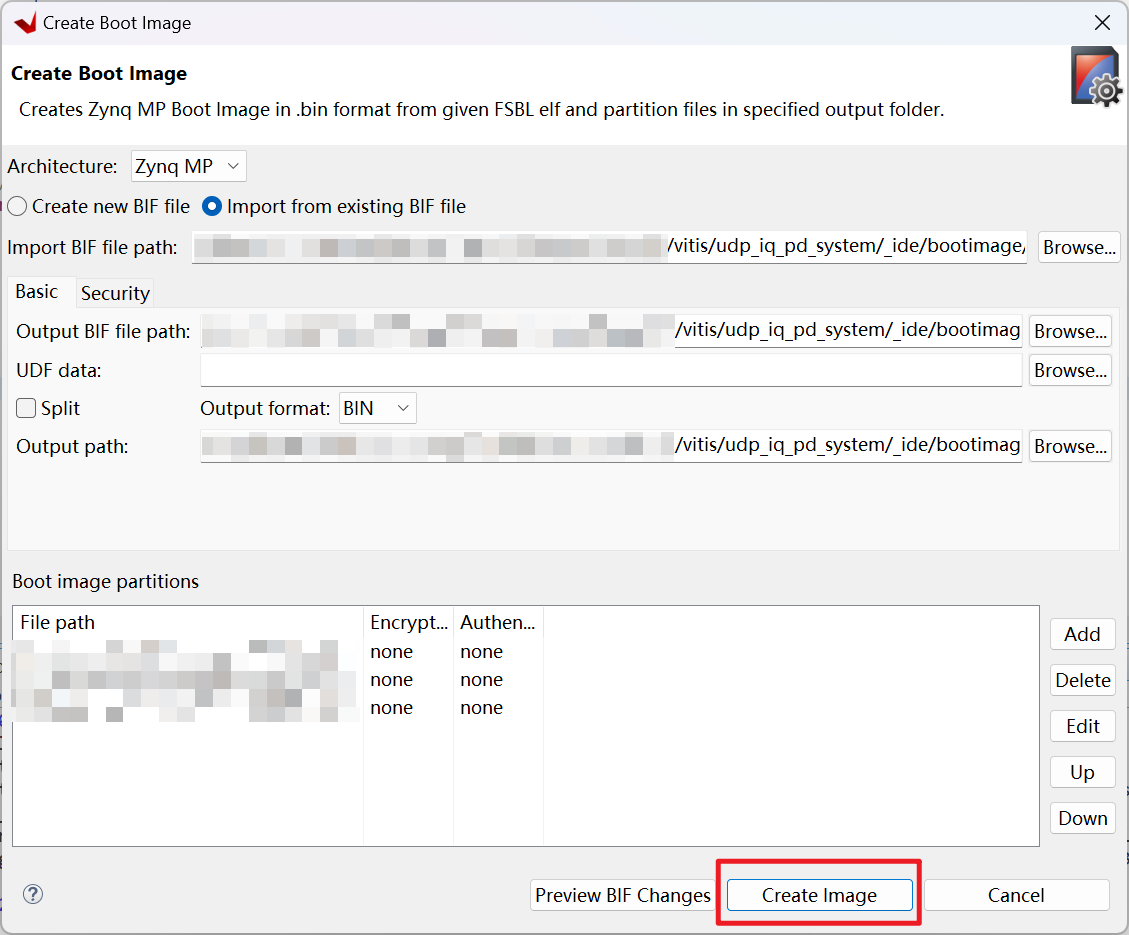

检查镜像工程的文件是否为固化需要的工程文件,点击创建镜像的选项即可完成创建,创建完成的镜像工程文件在_ide的文件路径下存储。

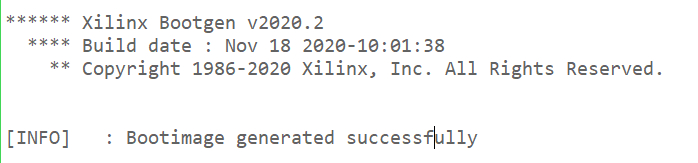

控制台显示如下创建完成。

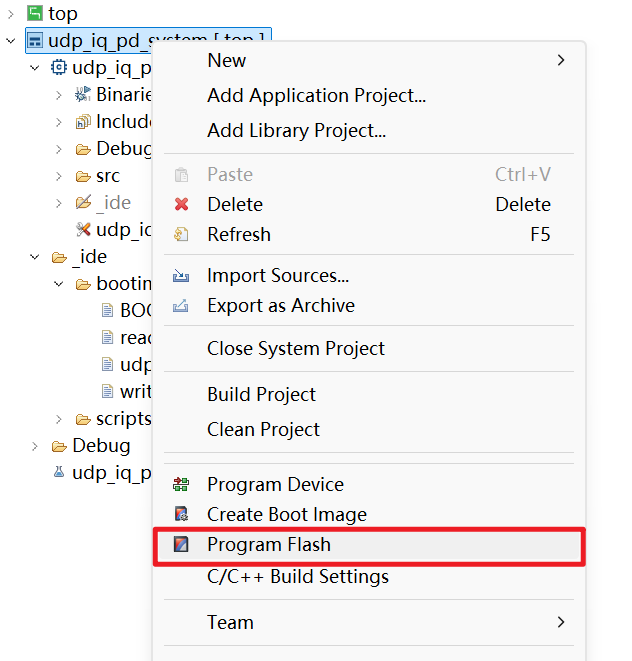

烧写镜像

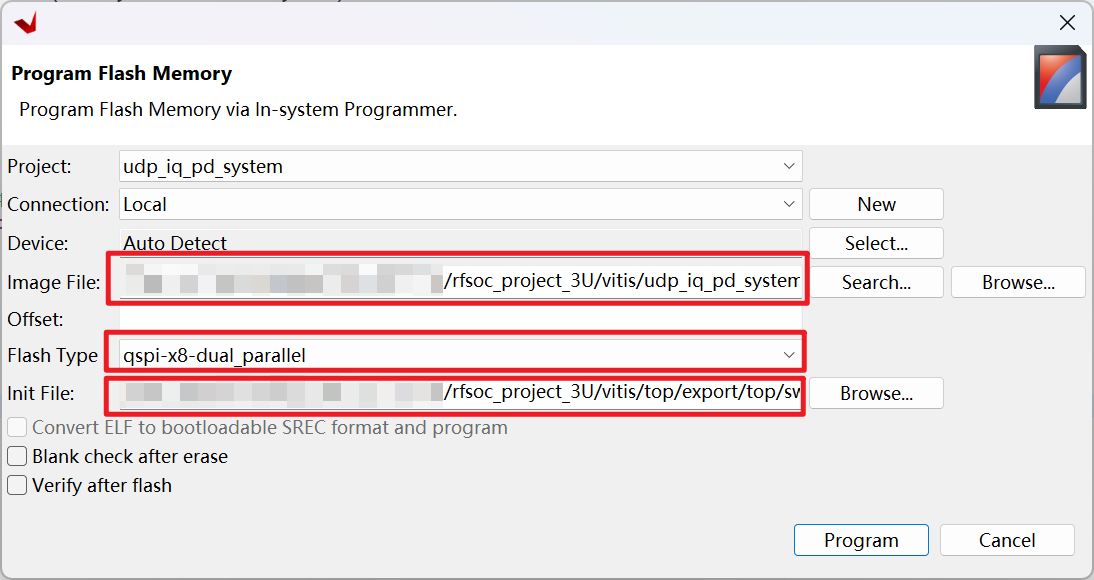

右键应用工程系统,点击Program Falsh。

确认镜像文件位置,确认Flash类型,确认初始化文件位置。无误后点击Program。

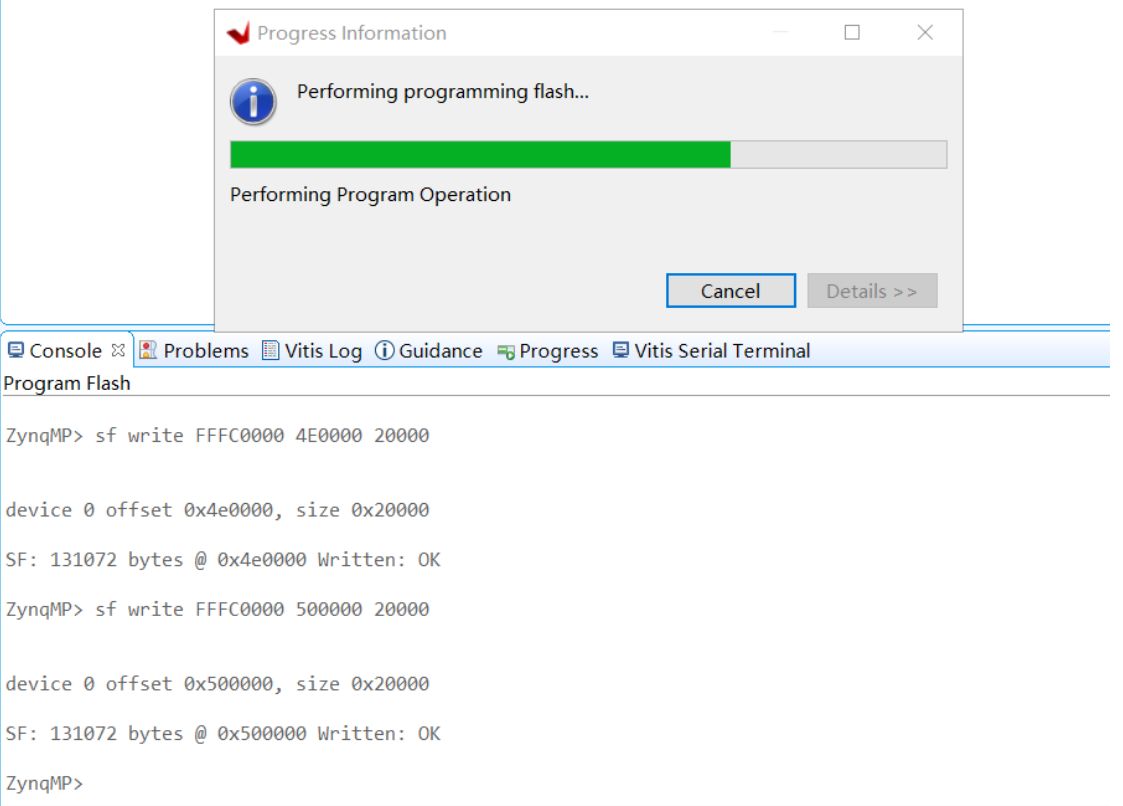

等待固化完成。

改变启动模式

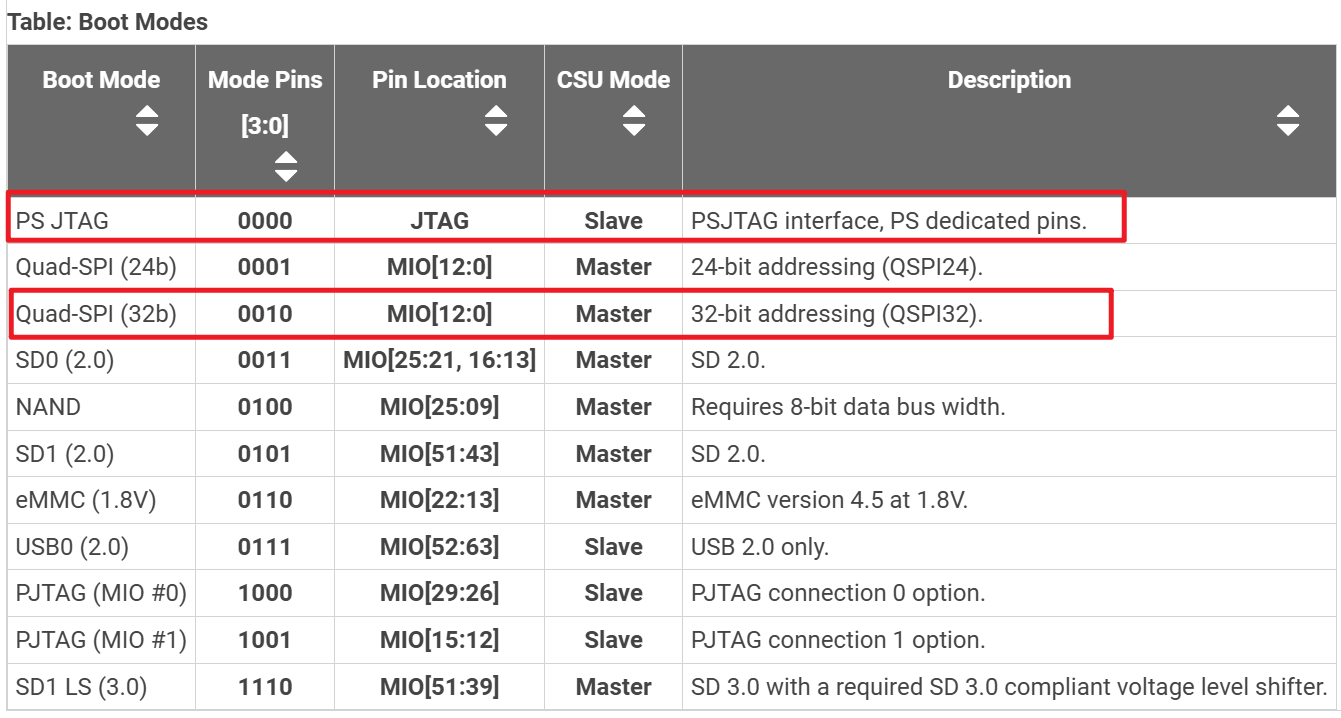

固化完成后关闭开发板电源。

根据Xilinx官方手册UG1085Boot Modes章节,拨动板子上的拨码开关。

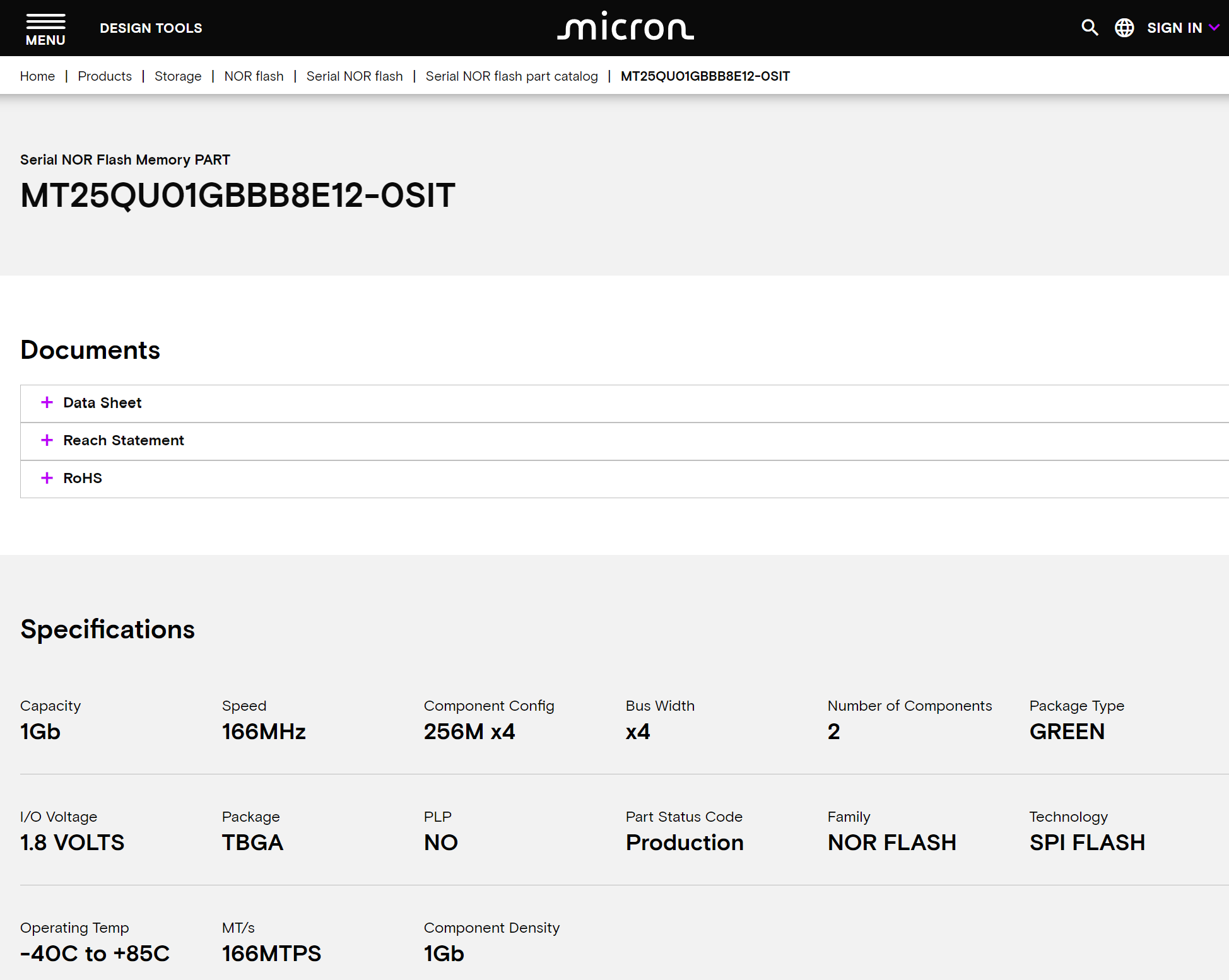

我这里是两片MT25QU01GBBB8E12-0SIT组成的FLASH,所以拨码开关值为:0010。

扩展知识

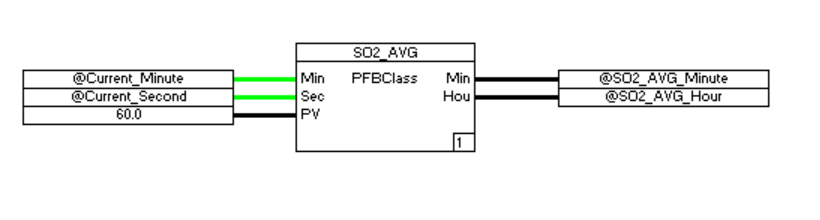

关于 QSPI 的位数 和 Flash 芯片的总线宽度 的详细知识如下:

QSPI 位数

QSPI (Quad SPI) 是一种增强的 SPI 接口协议,它扩展了传统 SPI 的数据传输方式:

-

传统 SPI 接口

:

- 数据线宽度为 1 位(即 MISO 或 MOSI 单条数据线)。

-

QSPI 接口

:

- 扩展为最多 4 位(即 IO0、IO1、IO2、IO3 四条数据线并行传输数据)。

- 数据总线可以在以下模式间切换:

- x1 模式:与传统 SPI 一样,只用 1 条数据线。

- x2 模式:使用 2 条数据线并行传输数据。

- x4 模式:使用 4 条数据线并行传输数据,是 QSPI 的核心优势。

- Zynq 的 QSPI:支持单 QSPI 的 x1、x2、x4 模式,双 QSPI 时可支持 x8 模式(即两个芯片并行,每个 x4)。

Flash 芯片总线宽度

- 总线宽度的定义:

总线宽度指的是 Flash 芯片在一次数据传输中可以同时处理的位数(例如 1 位、2 位、4 位或 8 位)。 - MT25QU01GBBB8E12-0SIT 的总线宽度:

- 支持 x1、x2 和 x4 模式。

- 在 QSPI 中运行时可以通过数据线 IO0~IO3 提供 4 位宽的数据并行传输。

- 当两个芯片组成 双通道(Dual Parallel)模式 时,可实现总线宽度 x8,大幅提高吞吐量。

- 硬件连接和电路设计:

- 每片 Flash 通过 4 条数据线(IO0-IO3)连接到 Zynq 的 QSPI 控制器。

- 如果是双 QSPI 模式,两片 Flash 芯片分别通过各自的 4 条数据线连接,总共 8 条数据线。

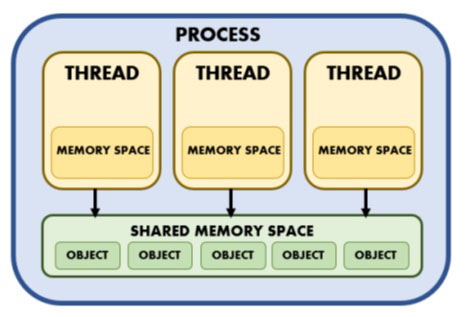

QSPI 位数与总线宽度的关系

-

单片 Flash 的模式:

- 在单片 Flash 中,QSPI 的最大位宽为 4 位,支持 x4 模式。

-

双片 Flash 的模式(Dual Parallel 模式):

- 通过将两片 Flash 芯片并联,每片工作在 x4 模式,整体实现 x8 模式。

- 在这种模式下,数据吞吐量是单片 Flash 的两倍,但启动镜像需要特别设计为双通道模式(每片存储部分镜像数据)。

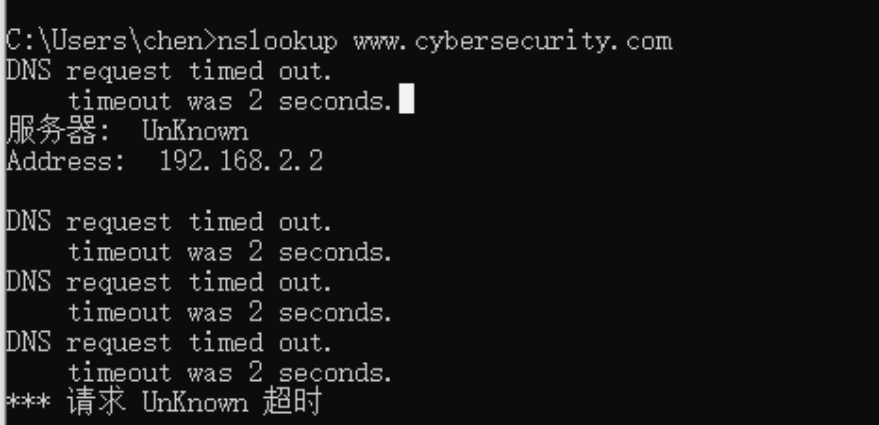

- 寻址位宽

-

24 位地址模式:

地址长度为 3 字节(24 位),最大寻址范围是 16MB(2^{24}bit = 16MB)。

适用于总容量 ≤ 16MB 的 Flash 存储器。 -

32 位地址模式:

地址长度为 4 字节(32 位),最大寻址范围是 4GB(2^{32}bit = 4GB)。

必须在 Flash 容量 > 16MB 时使用(如 MT25QU01GBBB8E12-0SIT 的 128MB 容量)。

Parallel 模式的定义

- Parallel 模式允许两片 QSPI Flash 芯片同时传输数据,每片工作在独立的 x4 模式,总线宽度扩展为 x8 模式。

- 主要特点:

- 两片 Flash 的 CS(Chip Select)独立控制。

- 同时发送相同的指令和地址,分别返回数据的高 4 位和低 4 位。

- 数据流合并为 8 位宽,从而实现更高的吞吐量。

![[豪の学习笔记] 计算机网络#001](https://img2024.cnblogs.com/blog/3555868/202411/3555868-20241114213740559-965309427.png)