- I2C的R16_I2C_CTRL2寄存器描述:

[5:0] FREQ :允许的范围在2~36MHz之间。必须设置在000010b 到100100b 之间

RB_I2C_FREQ决定SCL的建立时间和SDA的保持时间,理论上I2C

频率可以达到一分频,实际频率可在36MHz之上,可使用最高80MHz。

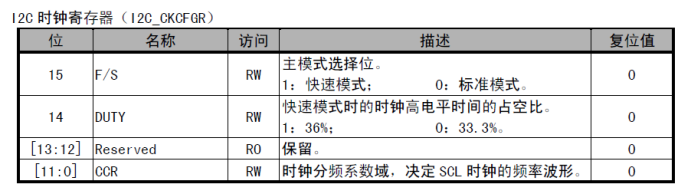

- I2C的R16_I2C_CKCFGR寄存器描述:

[11:0] CCR RW :时钟分频系数域,决定SCL 时钟的频率波形。

RB_I2C_CCR决定SCL高电平维持多少个系统主时钟周期。

其计算公式如下:(Tclk为FREQ时钟周期,Tscl为I2C的scl时钟周期,Thigh和Tlow分别为scl一个周期种的高低电平占比,Fclk为FREQ时钟频率,Fscl为I2C的scl时钟频率)

在I2C标准模式或SMBus模式下:(100kHz及其以下)

Thigh = CCR ×TPCLK1

Tlow = CCR ×TPCLK1

即:Tscl = Thigh+ Tlow = 2 * CCR ×Tclk

假设FREQ = 60,即频率为60MHz,需要得到100KHz频率,即:

CCR = = = = 300

在I2C快速模式下:

如果DUTY = 0:

Thigh = CCR ×Tclk

Tlow = 2 × CCR ×Tclk

即:Tscl = Thigh+ Tlow = 3 * CCR ×Tclk

如果DUTY = 1:

Thigh = 9 × CCR ×Tclk

Tlow = 16 × CCR ×Tclk

即:Tscl = Thigh+ Tlow = 25 * CCR ×Tclk

例如:在快速模式下,FREQ = 80,产生800kHz的SCL的频率:

CCR = = = = 4

注: 1. CCR允许设定的最小值为0x04,在快速DUTY = 0 模式下允许的最小值为0x0A(测试值,具体分频系数往极限调整时会受到建立时间和保持时间的影响,极限情况很可能采不到数据,比如在电平拉升的这段时间采,可能原本高电平采到低电平);在快速DUTY = 1 模式下允许的最小值为0x01;

2. 只有在关闭I2C时(PE = 0)才能设置CCR寄存器;

3. Fclk应当是10MHz的整数倍,这样可以正确产生400kHz的快速时钟。

3.I2C例程实际收发速率:

中断收发: 4.55702ms/200字节 (351k bit/s)

非中断收发: 4.51829ms/200字节 (354k bit/s)

注:该实际速度计算时按一字节8bit计算,没有将应答位时间计入(即一字节9bit),实际上只浪费了装填数据的时间,收发速度接近400k bit/s