Architecture and Process Integration Overview of 3D NAND Flash Technologies

3D NAND闪存技术的架构和工艺集成概述

摘要:在过去的几十年里,NAND闪存一直是最成功的非易失性存储技术之一,由于其高可扩展性和可靠的开关特性,它在电子设备中得到了广泛的应用。为了克服平面NAND闪存阵列的缩放限制,工业界和学术界都对NAND闪存的各种三维(3D)架构及其工艺集成方法进行了研究,并将其应用于商业批量生产。本文从架构和制造方法的角度对3D NAND闪存技术进行了回顾,并比较了这些架构的优缺点。

关键词:NAND闪存;三维建筑;过程集成

3D NAND闪存架构已经以各种结构实现,根据堆叠方向可分为两类:沟道堆叠和栅极堆叠。

图1显示了3D NAND闪存的结构-年份分类。东芝宣布推出首款基于栅极堆叠结构的3D堆叠闪存,如位成本可扩展(BiCS)、带电荷捕获层的管状BiCS(PBiCS)和带浮栅的水平沟道型浮栅(HC-FG)。

图1. 3D NAND闪存技术的按时间顺序发展。

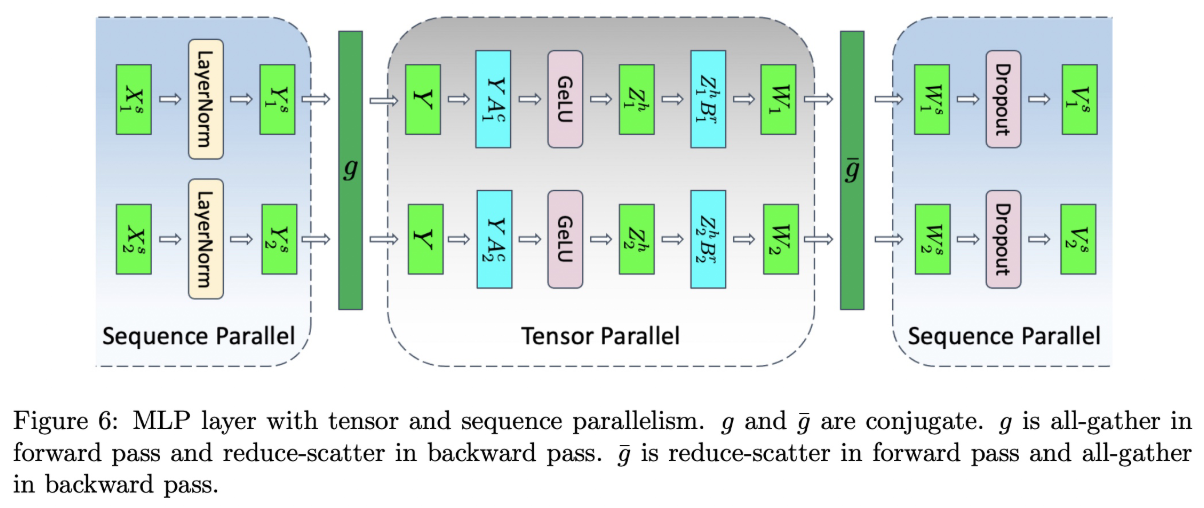

三维NAND闪存架构

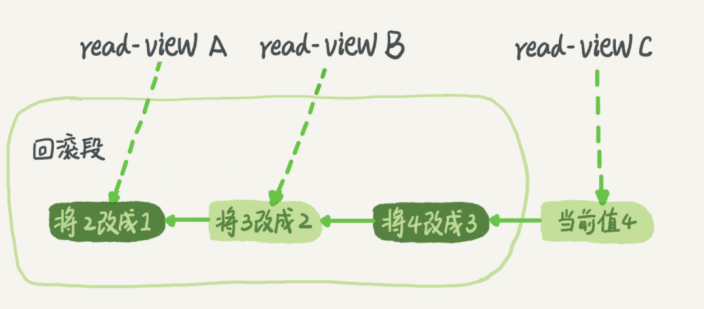

3D NAND闪存的架构通常可分为栅极堆叠结构和沟道堆叠结构,如图2所示。在栅极堆叠结构中,堆叠栅极层后形成沟道,电流沿垂直方向流动。单元结构主要基于全栅极(GAA),因为沟道孔填充有多晶硅(poly-Si)和栅极电介质堆叠;从本质上讲,这种结构存在几个由孔径引起的问题。相比之下,在沟道堆叠架构的传统平面NAND阵列中,电流沿横向流动。尽管沟道堆叠结构的缩放受到位线(BL)间距中ONO厚度的限制,但有必要保持字线(WL)沟道长度以保持有效的存储窗口。

此外,由于BL的水平和平行取向,很难将其与每一层连接起来。目前,由于沟道堆叠结构中的上述问题,大多数商业化的3D NAND架构使用栅极堆叠结构。

图2:(a) 栅极堆叠(垂直沟道)和(b)沟道堆叠(垂直栅极)3D NAND架构,

图3a、b分别比较了基于栅极堆叠结构和栅极第一制造方法的BiCS和PBiCS飞灰结构的横截面图。BiCS闪存结构是第一个提出的具有高密度和每比特成本的3D NAND架构。在BiCS结构中,垂直堆叠的栅极由下选择栅极(LSG)、上选择栅极(USG)和控制栅极(CG)组成,如图3a所示。由于在这种结构中沟道柱没有直接连接到p阱,因此栅极诱导漏极降低(GIDL)被用作擦除机制。PBiCS架构改善了BiCS闪存的局限性,包括编程/擦除窗口、保持特性、源极线(SL)的高电阻和多比特操作。

PBiCS飞灰具有U形串结构,而不是直线形状,在两个相邻闸门之间的底部形成管道连接(PC)。这种结构差异降低了SL电阻,因为它可以被第一和第二金属层访问,类似于传统的平面NAND闪存阵列。在可靠性方面,由于在制造过程中对捕获层的损伤较小,PBiCS飞灰具有更好的保持特性,金属布线的低电阻和SL处陡峭的受控扩散特性使PBiCS具有更好的截止特性。

图3(a)BiCS结构和(b)PBiCS结构的横截面图。

图4a显示了TCAT架构的横截面图。TCAT使用金属CG,因为使用了后栅极制造方法。多晶硅沟道孔使用与BiCS结构中类似的穿孔方法形成;然而,一个显著的区别是TCAT连接到p型基板,这允许体擦除操作。该结构中的两个多晶硅沟道共享由WL切割形成的公共源极线(CSL)。图4b显示,TCAT单元阵列的电路图等效于每串层90°旋转的平面阵列,其底端连接到CSL。接地选择线(GSL)和串选择线(SSL)晶体管分别位于串的顶部和底部,飞灰单元串联放置在它们之间。

图4(a)TCAT飞灰阵列结构的横截面图和(b)等效电路图。

图5a显示了VRAT架构,其中包含用于有效垂直互连的同一平面上的平面集成(PIPE)结构。在化学机械平面化(CMP)工艺期间,所有WL同时暴露在同一平面上。与阶梯状方法不同,WL不需要对每一层进行连续蚀刻,这意味着PIPE结构在堆叠后无需额外的光刻步骤即可提高WL互连的效率。VSAT旨在解决VRAT结构制造中的困难,如图5b所示。VSAT结构不是使用形成和填充底切区域的最后栅极工艺,而是使用掺杂多晶硅的栅极优先方法制造。由于VSAT结构不需要底切工艺,因此很容易实现垂直串和堆叠的WL,这类似于目前商业化的3D NAND闪存串。此外,VSAT架构的双栅极结构有效地延长了沟道长度,而没有单元密度损失,从而降低了截止电流。

VG NAND结构的示意图和晶胞图如图6所示。与BiCS和TCAT结构不同,这里的通道是水平堆叠的,除了SSL之外,它的结构几乎与平面灰阵列的结构相同,这意味着每层的有效单元大小保持为4F2。源极和有源体(Vbb)连接到CSL,实现体擦除操作,所需的SSLs数量取决于有源层的数量。在堆叠的有源沟道层之间使用常见的BL和WL,需要选择一个串来通过SSL偏置对特定的目标单元进行编程。

图5 具有PIPE结构的(a)VRAT和(b)VSAT示意图。

图6 VG NAND闪存阵列示意图。

与上述方法不同,浮动栅极用作DC-SF结构中的电荷存储层,如图7a所示。在这种结构中,FG被两个CG包围,并被多晶硅间电介质(IPD)和隧道氧化物覆盖。

它由两个CG组成,并呈现垂直方向。由于IPD层较厚,CG方向上不会发生隧穿。此外,与BiCS不同,由于FG中的隔离电荷,电荷扩散现象很少发生,如图7b所示。在BiCS的情况下,电荷扩散发生是因为CTL连续连接到相邻的电池,而在DC-SF中则不会发生,因为FG与每个电池分离和隔离。此外,由于两个CG的屏蔽效应,小区间的干扰可以忽略不计。它还具有宽的编程/擦除窗口、低工作电压和高耦合比。通过使用FG,DC-SF可以具有良好的保留特性;然而,由于存储膜比CTL厚,这限制了沟道孔尺寸的缩放,因此对3D堆叠不利。

图7(a)DC-SF结构鸟瞰图。(b)BiCS和DC-SF结构中的电荷扩散